在芯片的设计、生产、测试全流程中,ESD(静电放电)是无处不在的“隐形杀手”,瞬间的静电冲击可能直接导致芯片栅氧击穿、金属连线烧毁,最终引发失效。而 ESD 测试是验证芯片抗静电能力的核心手段,其中芯片级 ESD 测试的四大核心模型(HBM/MM/CDM/HMM)更是行业研发、量产的重要依据。

今天就带大家系统梳理芯片级 ESD 测试的主流模型,从模拟场景、等效电路到放电特征,一次性讲清核心要点,看懂芯片的“静电防护考卷”!

人体模型(HBM):最常见的静电失效场景

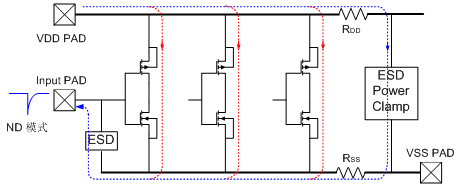

HBM 是芯片 ESD 测试中最基础、最常用的模型,也是实际应用中占比超 70% 的失效场景,核心模拟带静电的人体与芯片接触时的放电过程。

核心原理

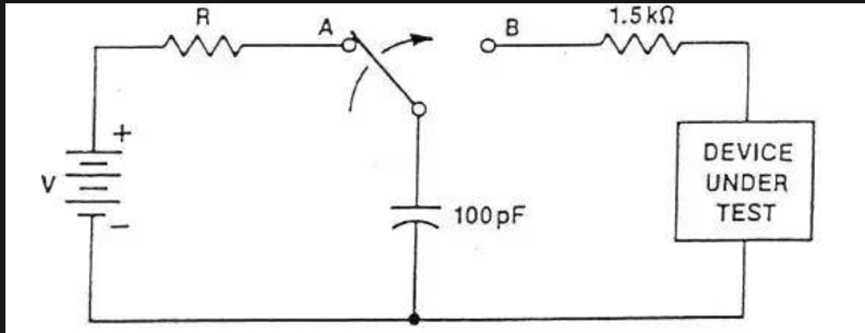

- 充电阶段:人体因摩擦、感应带上静电荷,等效为高压电源对 100pF 电容(Cesd)充电;

- 放电阶段:人体手指接触芯片管脚形成对地通路,充满电荷的电容通过 1.5kΩ 等效电阻(Resd)向待测芯片(DUT)放电。

关键特征

- 等效电路核心参数:100pF 电容 + 1.5kΩ 串联电阻;

- 放电波形:上升沿较缓,约 10ns,无振荡;

- 峰值电流:约 1.33 A/kV,2kV 测试时峰值约 2.66A,一般不超过 5A;

- 失效特点:因人体寄生电阻限流,冲击相对温和,多损伤芯片 I/O 接口,对内部核心电路影响较小。

开关开始处于A状态, 电源对人体等效电容Cesd充电, 其目 的主要是模拟人体因为摩擦或者感应带上静电荷的过程; 当开关切换到B状态时,A阶段充满电荷等效电容通过人体等效电阻Resd对待测器件放电, 其目 的是模拟人体接触到芯片管脚, 并产生对地通路而放电的过程。

机器模型(MM):产线设备的静电冲击

MM 模型针对芯片生产制造环节设计,模拟未做好静电防护的自动化设备(机械臂、夹具、探针等)带静电后,接触芯片管脚形成放电的过程。

核心原理

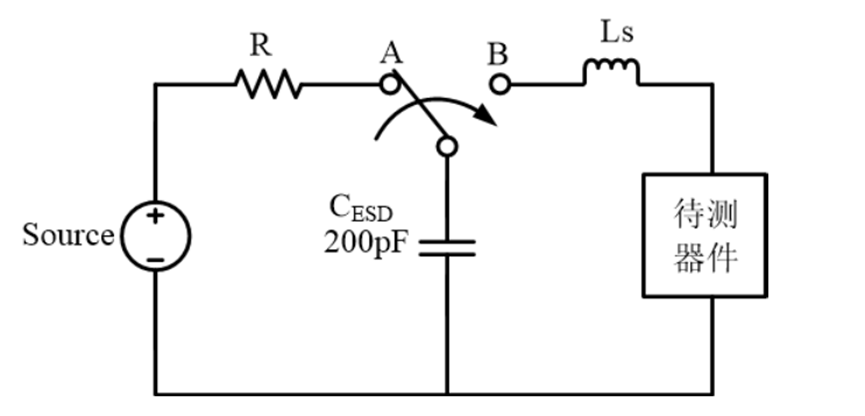

机器为金属材质,内阻极小,因此等效电路中无串联限流电阻,仅通过 200pF 储能电容向待测芯片直接放电,芯片其他管脚接地形成通路时,静电电荷快速转移。

关键特征

- 等效电路核心参数:200pF 电容,串联电阻 R=0Ω;

- 放电波形:上电速度快,上升沿 6-8ns,因寄生电感影响,波形会呈现正负振荡;

- 峰值电流:同电压下远高于 HBM,冲击性更强;

- 行业现状:因与实际失效场景关联度降低,JEDEC 已逐步淘汰该模型,不再作为芯片 ESD 强制测试项。

MM模型模拟的是金属, 而金属内阻很小, 因此上电速度很快,通常为6-8ns。 由于内阻较小, 同电压下MM模型的峰值电流较高,同时因为寄生电感,MM的放电波形会呈现正负振荡

组件充电模型(CDM):破坏性最强的芯片级 ESD

CDM 是先进工艺芯片(纳米级 / FinFet 工艺)最主要的 ESD 风险,核心模拟芯片自身带电后的放电过程,也是三种经典模型中破坏性最强的一种。

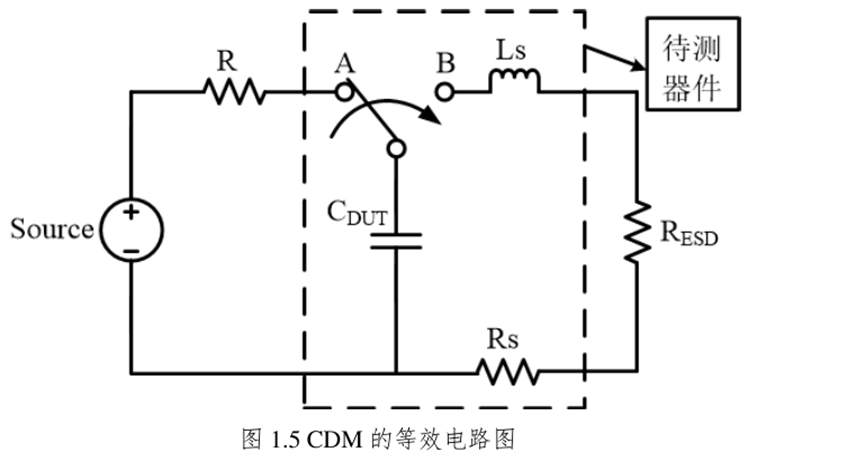

核心原理

芯片在制造、测试、运输过程中,通过摩擦、接触或感应自身带上静电荷(而非外部物体带电),当芯片管脚接触接地体时,内部大量静电荷通过管脚快速流出,形成放电。其等效电路充电阶段直接对芯片自身等效电容充电,放电回路的电阻、电感极小,电荷泄放速度极快。

关键特征

- 放电波形:上升时间极短,仅 0.1-0.6ns,脉冲持续时间约 5ns,属于“快脉冲、高峰值”波形;

- 峰值电流:远高于 HBM/MM,瞬间大电流易直接击穿芯片内部栅氧、损坏核心逻辑 / 模拟模块;

- 工艺关联:随着芯片工艺尺寸缩小,FinFet 工艺下电压瞬态过冲问题加剧,CDM 引发的失效愈发突出,成为高端芯片 ESD 设计的重点关注对象。

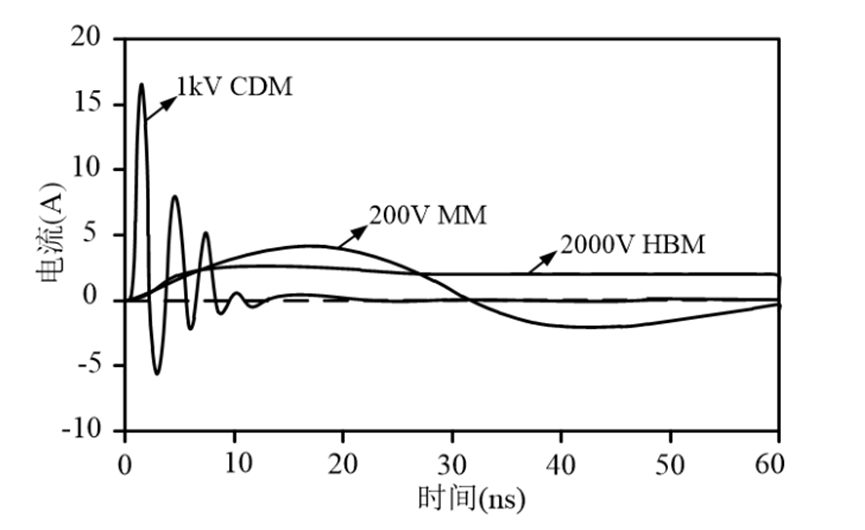

三种模型典型的放电波形图, 从中可以得出HBM的波形峰值最低, 但持续时间长;MM波形会产生正负振荡, 且峰值比HBM要高, 持续时间也较长;CDM波形的上升速度很快, 峰值很高且持续时间短。

人体金属放电模型(HMM):系统级 ESD 的新模型

HMM 是业界新研发的 ESD 测试模型,弥补了传统芯片级模型与实际系统应用的差距,核心模拟带静电的人体通过金属 / 机械部件(如数据线、外壳、设备接口)与芯片管脚接触的放电过程,主要用于评价芯片在电子系统中的 ESD 鲁棒性。

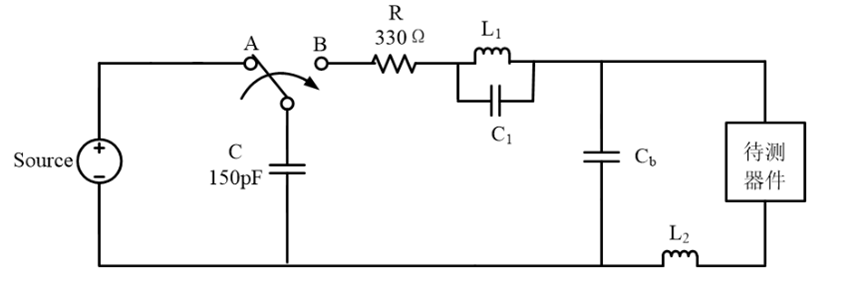

核心原理

充放电过程与传统模型一致,但因引入了金属部件,等效电路的寄生参数最多,包含寄生电感(L1/L2)、平板电容(Cb)、150pF 储能电容及 330Ω 电阻,更贴近实际系统中的静电传输场景。

关键特征

- 等效电路:寄生参数丰富,更贴合系统级应用实际;

- 放电波形:上升时间约 0.7ns,介于 CDM 与 MM 之间,脉冲持续时间约 50ns;

- 应用场景:主要用于芯片在终端系统中的 ESD 性能验证,衔接芯片级与系统级 ESD 测试。

充放电过程与之前模型一致, HMM模型的寄生参数为(L1,C1,L2) ,Cb为平板电容。 其放电波形上升时间很短, 约为0.7ns, 持续时间约为50ns。

四大模型放电波形大对比|一眼看懂核心差异

不同 ESD 模型的放电特征直接决定了其对芯片的损伤程度,核心差异集中在上升时间、峰值电流、持续时间、波形形态四个维度,经典对比特征如下:

- HBM:峰值最低,上升沿最缓(≈10ns),持续时间最长,波形无振荡;

- MM:峰值高于 HBM,上升沿 6-8ns,持续时间较长,波形因寄生电感呈正负振荡;

- CDM:上升最快(0.1-0.6ns),峰值最高,持续时间最短(≈5ns),快脉冲冲击性最强;

- HMM:上升时间 0.7ns,峰值适中,持续时间约 50ns,寄生参数影响显著,贴近系统实际。

简单总结:CDM 看瞬态抗冲击能力,HBM 看常规接触防护能力,HMM 看系统应用适配能力,而 MM 则因行业发展逐步退出主流测试体系。

文末小结

芯片级 ESD 测试的四大模型,分别对应了芯片从生产、测试到系统应用的不同静电失效场景,其核心设计逻辑均为模拟实际静电产生、传输、放电的全过程,为芯片 ESD 防护设计提供量化的测试标准。

对于芯片设计而言,HBM 和 CDM 是现阶段必须重点攻克的两大模型,车规、工业级芯片还需兼顾系统级的 HMM 测试;而在实际应用中,芯片的 ESD 等级并非越高越好,需结合应用场景平衡防护能力、芯片面积、功耗三者关系,找到最优解。

静电防护是芯片的“基础必修课”,看懂 ESD 测试模型,才能从源头理解芯片的静电防护设计逻辑,让芯片在全生命周期中远离静电失效风险!

文末互动

你在芯片研发 / 测试中,遇到过哪些典型的 ESD 失效问题?评论区一起交流~

-

芯片

+关注

关注

463文章

54422浏览量

469249 -

ESD

+关注

关注

50文章

2424浏览量

180413 -

测试

+关注

关注

9文章

6402浏览量

131673

发布评论请先 登录

深海连接器: 从原理到应用的全维度解析

RC电路的核心作用解析:从基础原理到实战应用

负氧离子监测系统:从原理到应用的全维度突破

深海连接器:从原理到应用的全维度解析

静电放电抗扰度ESD测试全解析:从原理到实战,一文讲透

测试ESD波形时示波器用什么探头?

ESD防护设计的核心准则

芯片 ESD 测试核心模型全解析|从基础原理到波形特征

芯片 ESD 测试核心模型全解析|从基础原理到波形特征

评论