电子发烧友网报道(文/周凯扬)要说去年内存市场最大的动静是DDR5内存的面世,那么今年的大新闻无疑是一众CXL内存的新品出现了。CXL这种新的互联技术标准给内存市场,尤其是数据中心内存市场带来了更大的空间,从带宽和容量上实现了数量级的增长。但说归说,一个标准能不能普及起来,关键还是在于有没有厂商跟进,CXL发布至今,我们就来看看IP、芯片和存储厂商们的动作。

Arm

作为开始在服务器和数据中心上抢夺x86份额的架构,Arm自然是早早就开始了CXL的布局,从Neoverse的第二代的产品中,全部都加入了CXL 2.0的支持,比如Neoverse V2、N2和E2等等。而到了下一代产品中,这三大产品线在提升性能和效率的同时,也会增加对CXL 3.0的支持。

更重要的是,Arm自身也有AMBA CHI这种连接SoC不同功能块之间的互联规范,未来有了UCIe和CXL,三大开放标准将为Arm生态带去全面的die to die和chip to chip连接解决方案。

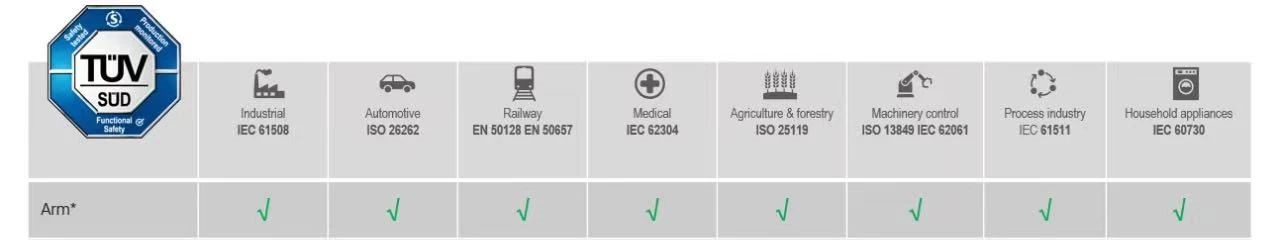

为了鼓励客户在CXL上与Arm合作,他们也点出了自己的几大优势。首先,在早年对CCIX这一标准的推进中,Arm已经对这种一致性设备技术有了足够的了解;其二,通过与合作伙伴之间的沟通,Arm最清楚需求上的变化,而且Arm在这个碎片化的生态系统中处于中立的地位;第三,Arm已经证实了自己在多个市场生态系统下的霸主地位,他们有信心在服务器和数据中心上展现自己的实力,推动整个CXL生态系统标准化。

澜起科技

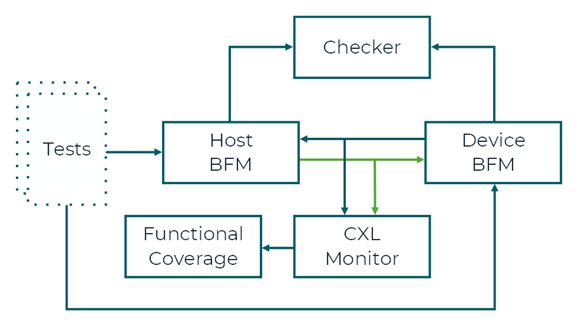

CXL并非一种新的内存制造技术,各大内存厂商造出的DDR4、DDR5服务器内存其实不会存在太大变化,但之所以能够通过CXL实现内存扩展,主要靠的还是全新的控制器芯片。比如澜起科技就在今年发布了首款CXL内存扩展控制器芯片(MXC),符合CXL 2.0中的Type 3内存扩展器规范,同时支持到PCIe 5.0的传输速率,兼容DDR4-3200和DDR5-6400的内存。

MXC芯片 / 澜起科技

在三星的发布的首款512GB CXL DRAM内存中,就用到了澜起科技的MXC芯片,今年8月SK海力士发布的DDR5 DRAM CXL内存,同样用到了MXC芯片。从今年OCP全球峰会上的演示来看,除了三星和SK海力士以外,澜起科技还会与美光合作,推出基于该芯片的CXL内存模组。

SK海力士

SK海力士也是积极推动CXL标准的先驱之一,甚至都已经为CXL内存的应用场景做好了规划,比如CXL最大的应用场景,内存扩展。根据SK海力士的说法,每通道两DIMM的时代已经迎来终结,未来数据中心的内存将摆脱大规模化的桎梏,至于内存带宽扩展,也可以通过CXL做到每个CPU接12通道内存,实现更优秀的交叉存取和加载延迟。

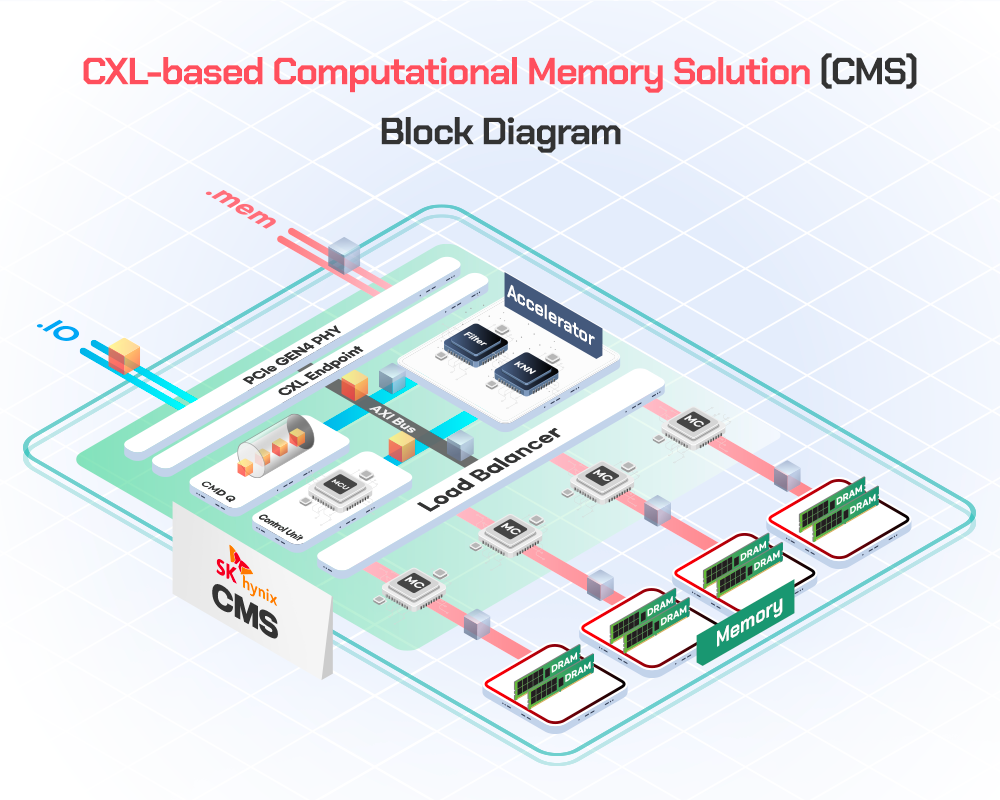

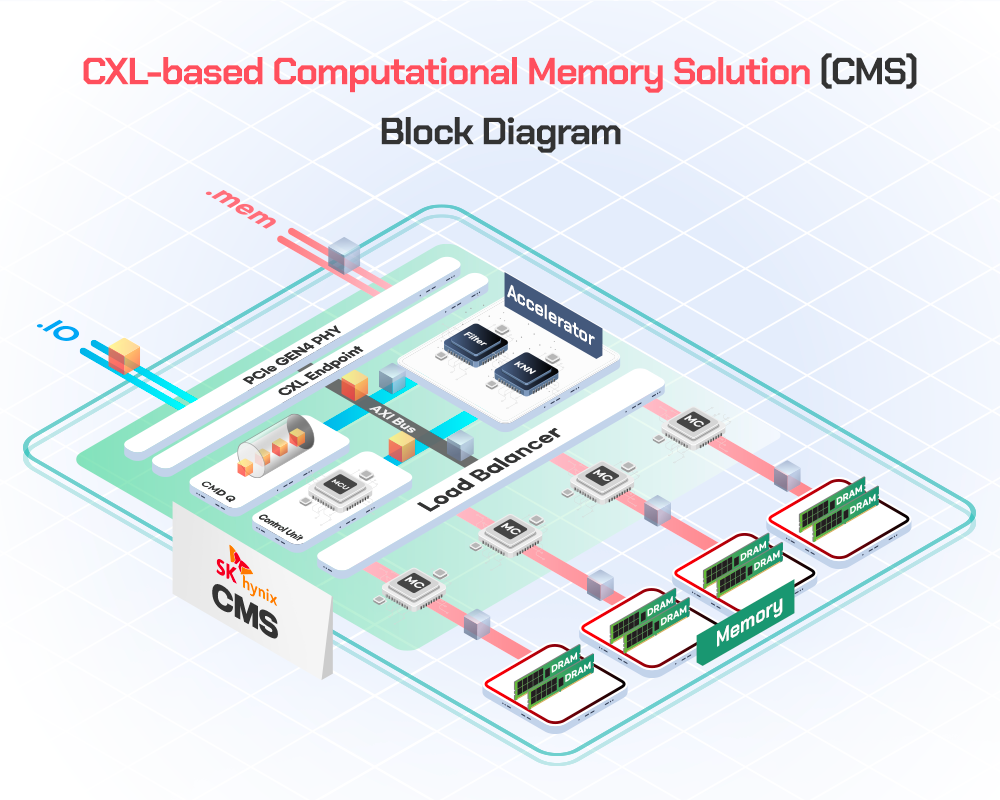

此外,SK海力士还设想了服务型内存这种场景,比如打造一个大型内存池容器,根据用户需求集成各种不同的内存介质,通过内存虚拟化来实现对xPU的灵活内存容量分配。另一个创新场景则是近内存计算,比如SK海力士最新推出的CXL计算内存方案(CMS)。

CXL计算内存解决方案 / SK海力士

从CMS的原理图来看,在支持CXL内存扩展的同时,SK海力士加入了不同的加速器来完成filter和KNN这些负责筛选分类的工作,对于机器学习来说能有奇效,甚至可以比几十个CPU内核的速度还要快上几倍。可以看出,在数据中心的AI/ML计算逐渐占大头后,这种针对特定运算的专用硬件已经开始出现在CPU、GPU等各个组件上,如今也在内存上现身了。

CXL内存延迟的问题

表面上云服务厂商还没有正式开始CXL的部署,毕竟CXL的产品生态也是差不多从今年起步的,然而他们也已经在评估测试CXL了。大家最担心的还是延迟问题,CXL虽然在带宽和容量之间找到了很好的定位,但内存延迟问题对于消费市场来说可能影响微乎其微,在数据中心上就会被无限放大。目前微软Azure以及Meta等等,都已经发表了一些公开数据,在两家的测试下,20%的负载都没有任何性能影响。由此看来,大部分负载还是得承受一些小小的牺牲,才能享受CXL带来的优势。

Arm

作为开始在服务器和数据中心上抢夺x86份额的架构,Arm自然是早早就开始了CXL的布局,从Neoverse的第二代的产品中,全部都加入了CXL 2.0的支持,比如Neoverse V2、N2和E2等等。而到了下一代产品中,这三大产品线在提升性能和效率的同时,也会增加对CXL 3.0的支持。

更重要的是,Arm自身也有AMBA CHI这种连接SoC不同功能块之间的互联规范,未来有了UCIe和CXL,三大开放标准将为Arm生态带去全面的die to die和chip to chip连接解决方案。

为了鼓励客户在CXL上与Arm合作,他们也点出了自己的几大优势。首先,在早年对CCIX这一标准的推进中,Arm已经对这种一致性设备技术有了足够的了解;其二,通过与合作伙伴之间的沟通,Arm最清楚需求上的变化,而且Arm在这个碎片化的生态系统中处于中立的地位;第三,Arm已经证实了自己在多个市场生态系统下的霸主地位,他们有信心在服务器和数据中心上展现自己的实力,推动整个CXL生态系统标准化。

澜起科技

CXL并非一种新的内存制造技术,各大内存厂商造出的DDR4、DDR5服务器内存其实不会存在太大变化,但之所以能够通过CXL实现内存扩展,主要靠的还是全新的控制器芯片。比如澜起科技就在今年发布了首款CXL内存扩展控制器芯片(MXC),符合CXL 2.0中的Type 3内存扩展器规范,同时支持到PCIe 5.0的传输速率,兼容DDR4-3200和DDR5-6400的内存。

MXC芯片 / 澜起科技

在三星的发布的首款512GB CXL DRAM内存中,就用到了澜起科技的MXC芯片,今年8月SK海力士发布的DDR5 DRAM CXL内存,同样用到了MXC芯片。从今年OCP全球峰会上的演示来看,除了三星和SK海力士以外,澜起科技还会与美光合作,推出基于该芯片的CXL内存模组。

SK海力士

SK海力士也是积极推动CXL标准的先驱之一,甚至都已经为CXL内存的应用场景做好了规划,比如CXL最大的应用场景,内存扩展。根据SK海力士的说法,每通道两DIMM的时代已经迎来终结,未来数据中心的内存将摆脱大规模化的桎梏,至于内存带宽扩展,也可以通过CXL做到每个CPU接12通道内存,实现更优秀的交叉存取和加载延迟。

此外,SK海力士还设想了服务型内存这种场景,比如打造一个大型内存池容器,根据用户需求集成各种不同的内存介质,通过内存虚拟化来实现对xPU的灵活内存容量分配。另一个创新场景则是近内存计算,比如SK海力士最新推出的CXL计算内存方案(CMS)。

CXL计算内存解决方案 / SK海力士

从CMS的原理图来看,在支持CXL内存扩展的同时,SK海力士加入了不同的加速器来完成filter和KNN这些负责筛选分类的工作,对于机器学习来说能有奇效,甚至可以比几十个CPU内核的速度还要快上几倍。可以看出,在数据中心的AI/ML计算逐渐占大头后,这种针对特定运算的专用硬件已经开始出现在CPU、GPU等各个组件上,如今也在内存上现身了。

CXL内存延迟的问题

表面上云服务厂商还没有正式开始CXL的部署,毕竟CXL的产品生态也是差不多从今年起步的,然而他们也已经在评估测试CXL了。大家最担心的还是延迟问题,CXL虽然在带宽和容量之间找到了很好的定位,但内存延迟问题对于消费市场来说可能影响微乎其微,在数据中心上就会被无限放大。目前微软Azure以及Meta等等,都已经发表了一些公开数据,在两家的测试下,20%的负载都没有任何性能影响。由此看来,大部分负载还是得承受一些小小的牺牲,才能享受CXL带来的优势。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54422浏览量

469239 -

IP

+关注

关注

5文章

1883浏览量

156692

发布评论请先 登录

相关推荐

热点推荐

设备救星疆鸿智能EtherNet/IP转DeviceNet压力变送器

设备救星疆鸿智能EtherNet/IP转DeviceNet压力变送器 去年大修期间,我们车间搞了个小改造——把一套老装置的压力监测系统接入全厂统一控制网络。说实话,这事说起来简单,做起来还挺折腾

从 4K 到 8K:AV over IP 正在迎来一次真正的技术跃迁

当分布式音视频产品在行业内遍地开花,AV over IP 从概念走向普及,大多数厂商仍在围绕 4K 方案做优化迭代时,一套面向下一代视听生态的8K 无损压缩可视化分布式系统,已经把超高

澜起科技发布PCIe 6.x/CXL 3.x AEC解决方案

澜起科技今日宣布,率先在国内推出基于PCIe 6.x/CXL 3.x标准的高性能有源电缆(AEC,Active Electrical Cable)解决方案。该方案面向数据中心从单机架向多机架复杂架构

从内存接口到PCIe/CXL、以太网及光互连,高速互连芯片市场分析

通信协议,通过信号处理、架构优化等方式,保障数据在各系统间高效、可靠传输。 高速互联芯片 按技术类别区分,高速互连芯片主要分为三大类:内存互连芯片、PCIe/CXL 互连

借助CXL和压缩技术实现高效数据传输

AI、科学计算、海量内存处理……这些硬核工作负载正在不断挑战系统极限。而 FPGA 异军突起,成为了实现高效数据传输的“关键推手”。想知道怎么在不改变整体架构的前提下,让带宽和能效实现“双飞跃”?答案就藏在压缩 IP 与基于 CXL(Compute Express Lin

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

最近扒了扒国产芯片的进展,发现中芯国际(官网链接:https://www.smics.com)的 14nm FinFET 制程已经不是 “实验室技术” 了 —— 从消费电子的中端处理器,到

发表于 11-25 21:03

从芯片到主板,科技创新实现高质量发展

数字化时代,科技的迅猛发展深刻影响着各个领域。从芯片到主板的集成,生动展现了科技创新如何成为推动高质量发展的核心动力。

老文章新视角:从静态测试到CI/CT生态的进化

从静态测试工具到CI/CT生态的进化,不仅是技术功能的叠加,更是软件工程方法论的范式跃迁。未来汽车行业的CI技术将不再是简单的“工具链拼接”,而是以虚拟化测试为底座、场景化为导向、标准化为纽带

智能无人设备从IP核到系统的全流程功能安全问题初探

功能安全是为许多智能无人设备保驾护航的重要措施,因此需要引起从IP到芯片和系统等各环节的重视,除了获得由权威机构在进行全流程审核,覆盖开发流程、测试报告及安全案例完整性之后获得ASIL

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

第二代 AMD Versal Premium 系列自适应 SoC 是一款多功能且可配置的平台,提供全面的 CXL 3.1 子系统。该系列自适应 SoC 旨在满足从简单到复杂的各种 CXL 应用需求

从IP到芯片,CXL的生态已经做起来了吗?

从IP到芯片,CXL的生态已经做起来了吗?

评论