作者:Ettore Giliberti,SmartDV Technologies资深应用工程师

在当今的高性能计算领域,确保处理器、存储和加速器之间快速可靠的通信对系统性能和可扩展性至关重要。因此,就诞生了Compute Express Link®(CXL®)标准:其目标是实现一致的内存访问、低延迟的数据传输,以及不同先进架构之间的无缝互操作性。

作为CXL联盟的活跃成员,SmartDV Technologies在设计和验证IP方面拥有数十年的专业知识,可以帮助工程团队了解不断发展的标准。我们符合规范的VIP产品组合使团队能够充满信心地采用最新的CXL版本来加速开发,同时保持鲁棒性和准确性。

随着CXL规范的快速演进发展,在对越来越多围绕它所打造的设计进行验证时,所使用的工具和构建的基础架构也必须同样迅速发展。维护与新规范的修订保持同步的验证IP (VIP)不是一项小任务,特别是处理从CXL 2.0到3.0的主要版本转换。

作为全球领先的VIP和定制IP解决方案提供商,我们在SmartDV Technologies亲眼目睹了VIP的快速适应能力的重要性,它们需要能够覆盖不同的版本,同时还要保持稳健性和准确性。这篇技术文章探讨了这些更新带来的技术挑战和工程考量因素,并引用了最近在支持CXL 3.0实际工作项目中所积累的示例。

持续演进的需要

基于CXL的硬件在流片前的验证既复杂又要求苛刻,因此VIP必须能够准确地模拟互连的主机和设备端,并提供可靠的协议检查器来验证系统行为。

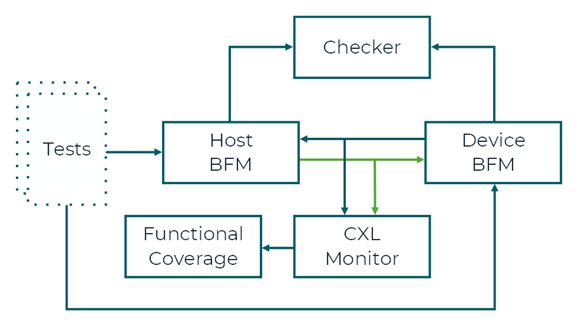

功能强大的VIP基础架构对于构建可靠的验证IP和随着规范的发展而实现快速更新至关重要。下面的图表说明了SmartDV的 CXL VIP所采用的高级架构。

图1:SmartDV CXL VIP功能原理图

随着CXL规范的更新,VIP也必须进行相应的升级,且通常要求在紧迫的时间内完成。

例如,从CXL 2.0到3.0的版本转换引入了一些重要的更改,这就需要对VIP进行大量更新,包括功能和协议处理。

关键变更和实施挑战

1. 支持256字节的数据Flit(流控制单元)

在CXL 3.0版本中,协议的Flit现已可支持256字节的数据,而CXL 2.0只支持68字节的数据。这带来了一些架构上的变化:

· 信用值(LLCRD),以前在单个Flit单元中传输,现在通过使用2字节字段(字节数为240-241)直接嵌入到协议Flit中。

· 在传输一个非空的协议Flit之前,请求、响应和数据(Flit类型为cache/mem)的初始信用值需要在协议Flit中公布。

· 公布的信用值反映了当前接收缓冲区的可用性。

2. Flit格式增强和循环冗余校验(CRC)处理

CXL 3.0引入了三种类型的Flit格式:

· 标准的256字节

· 延迟优化的(LO)Flit

· PBR Flit

延迟优化的Flit需要以不同的方式去计算CRC。前8个数据槽(122字节)需要在数据槽7 (6字节)中放置一个CRC,而其余数据槽(116B)需要一个单独的CRC。这种双重CRC结构要求在VIP内部要有精确实现和验证。

此外,现在的ARB/MUX链路管理数据包(ALMP)Flit包括CRC和前向纠错(FEC),而不再如CXL 2.0所要求的那样,为了完整性目的而需要复制数据。虽然这种改变简化了物理层表示层,但它将CRC/FEC管理的责任转移到协议栈中的一个全新位置。

3. 内存一致性和反向无效处理

CXL 3.0通过支持M2S反向无效窥探(Back-Invalidate Snoop, BISnp)通道改进了存储协议行为。在CXL 2.0中,设备到主机(device-to-host,D2H)的请求在等待M2S进程时可能会阻塞,从而限制了架构选择,无法使用诸如内含式窥探过滤器(Inclusive Snoop Filter)等手段。通过BISnp而不是CXL.缓存通道来解决一致性,CXL 3.0支持更灵活和高效的存储架构。

4. 重试机制被移至物理层

CXL 3.0中最重要的变化之一是将重试机制从链路层重新迁移到物理层。在CXL 2.0中,通过使用链路层中的本地和远程状态转换来管理重试。现在在CXL 3.0中,重试是通过一个Flit序列号握手系统来处理的。

全新的重试机制的主要特性包括:

· 新增传输端重试缓冲区,可用来存储所有协议Flits(CXL.io, CXL.cache / mem ALMP)。

· 基于序列号的、由确认驱动的缓冲区清除。

· 选择性否定确认(NACK)重放:能够重传特定的Flits,而不是重播所有未被确认的片段。

· 标准回放:所有等待确认的Flit的完整回放。

结语

为支持全新的规范修订版本,开发和更新CXL通用验证方法(UVM) VIP并不是一项简单的任务。即便有一个功能强大的、可重用的VIP基础架构,深入的领域知识和大量的工程工作也是必不可少的。为了让您了解所涉及的复杂性和所需时间,CXL 3.0主要的版本更新可能需要的工程工作量如下:

· 将重试机制迁移到物理层:需要4周时间

· 增加对256字节Flit和相关协议更改的支持:需要5周时间

这些时间估算都假设任务全部是由经验丰富的工程师负责,他们非常熟悉现有的VIP和CXL协议栈。

构建一个可扩展的、可自适应的CXL VIP不仅仅是编码工作;它也关系到对规范变更的预测和构建体系结构,从而适应未来的增长。

SmartDV Technologies凭借其在设计IP和验证IP两个方面都具有的丰富经验,为工程团队提供适用于像CXL这样的先进协议的高质量的、符合规范的VIP。随着标准的不断演进,SmartDV仍然致力于帮助客户保持领先地位。

-

芯片设计

+关注

关注

15文章

1128浏览量

56450

发布评论请先 登录

推荐高性能存储psram芯片

高性能计算集群在AI领域的应用前景

使用树莓派构建 Slurm 高性能计算集群:分步指南!

IBM Spectrum LSF如何助力半导体企业应对AI时代的高性能芯片需求

高性能计算面临的芯片挑战

Arm Neoverse CMN S3 推动Compute Express Link (CXL) 存储创新

让高性能计算芯片设计与CXL规范修订保持同步

让高性能计算芯片设计与CXL规范修订保持同步

评论