福晞2025

为方便用户了解和熟悉「福晞软件」,我们就软件的调试工具进行详细的讲解和说明,以帮助用户实现高效地开发和调试。

福晞软件提供了一套完整的芯片在线调试工具,用户可以通过这一系列的调试工具,在线观察芯片内部信号的变化。

本工具集提供了多种添加 Debugware IP 的方式,在完整运行福晞流程生成码流,并成功下载后,通过 Real Time Debug 工具可选择不同 LA Core,设置不同采样频率,不同触发条件。最后通过 Waveform 可以方便查看采样波形。

图 1-1清晰地描述了整个调试过程中不同工具的功能以及工具之间的相互依赖关系。

图 1-1 福晞软件调试流程

福晞软件在线调试主要分为以下4个步骤:

(1) 工程添加 Debugware IP;

(2) 运行综合,布局&布线,生成码流和下载;

(3) 设置触发条件;

(4) 查看波形。

在步骤(1)中,福晞软件提供了两种方式帮助用户在工程中添加 Debugware IP: Debugware UI 手动例化 Debugware IP 和借助 Debug Insert 工具自动添加 Debugware IP。

近期,我们将详细介绍上述相关步骤。

添加 Debugware IP

手动例化 Debugware IP

本节主要描述 Debugware IP 的手动例化使用方法。该 IP 核是一种嵌入式逻辑分析仪(Embedded Logic Analyzer),用于帮助设计人员观察 FPGA 内部信号跳变。采样信号波形存储 EMB 中,成功触发后可通过 JTAG 接口回读数据。用户可根据预设条件获取对应的波形图。

Debugware IP 支持以下功能:

动态配置触发条件

支持实时捕获

支持多种触发类型与条件:

(1) 算术运算

a. 等于(equal)

b. 不等于(not equal)

(2) 边沿检测

a. 上升沿(rise)

b. 下降沿(fall)

支持最多 4 个 LA 核

多 LA 核协同管理

支持多 EMB 扩展,以增加采样数据的位宽与深度

注意

确保设计满足时序要求;

确保 Debugware IP 实际使用的 EMB 数量不要超过当前器件可使用 EMB 总数。

Debugware IP 支持器件:

HME-M7,HME-M5,HME-HR3,HME-HR2,HME-H1,HME-H3,HME-H3P,HME-H7,HME-P0,HME-P1,HME-P2,HME-P3

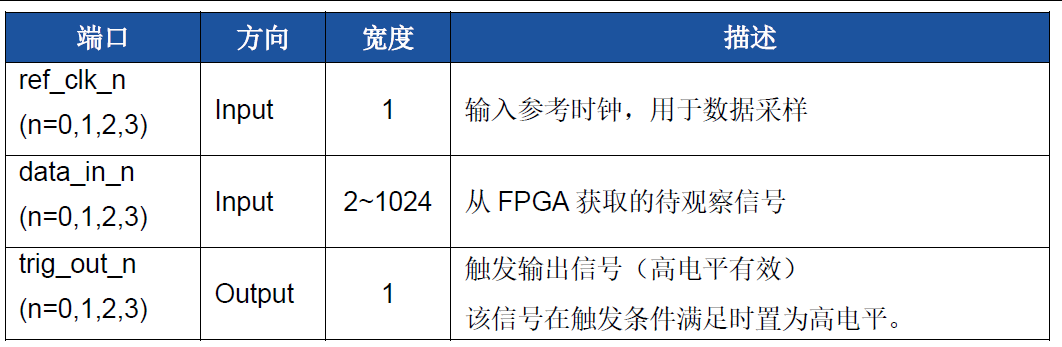

Debugware IP 端口介绍

表 2-1 Debugware IP 端口介绍

Debugware IP 框图

Debugware IP 由三部分组成:

TAP,LA Manager 和 LA Core,如图2-1所示。

TAP:JTAG 控制器的调试接口封装逻辑(为 JTAG 协议提供硬件适配层)。

LA Manager:Debugware IP 的中央控制单元,担任 TAP 模块与 LA 核之间的桥接枢纽,有且只有一个(1个 LA Manager 可同时控制最多4个 LA 核)。

LA Core:Debugware IP 的执行单元;包含两大核心模块:触发生成模块(Trigger Generator)和存储模块(Storage Module)。

图 2-1 Debugware IP UI 介绍

Debugware IP 使用介绍

用户可通过 Debugware 按以下步骤生成 Debugware IP:

步骤 1

按照图 2-2所示,从Wizard Manager中选择Debugware(v2.1a)启动 Debugware IP UI。

图 2-2 选择 Debugware IP

步骤 2

用户可按照图 2-3,图 2-4和图 2-5所示,配置Debugware IP。

图 2-3 输入模块名称

图 2-4选择 LA Core 的数量(最大值为4)

图 2-5配置存储参数

Trigger Model:设置触发模式,可选项为:Single 和 Multiple;选择 Single 时,Debugware 不支持多窗口触发方式;选择 Multiple 时,支持多窗口触发模式。但 Multiple 模式下,窗口个数设为1时,不等价于 Single 模式。Multiple 模式使用的资源数量比 Single 模式多。

Data Width:设置 Debugware 使用的 EMB 的数据位宽,数据位宽的值应该大于等于您要实际观察信号的数量;

Memory Depth:设置 Debugware 使用 EMB 的深度,该值大小决定触发时采样的周期数。

Input DFF Level:设置待观测信号的打拍个数,范围0~6。说明:改善增加 Debugware IP 对用户逻辑性能的影响,值越大影响越小,推荐值为2。

步骤 3

点击Finish生成 IP RTL 源代码文件,该文件会被自动加到工程中。然后,您需要在工程中手动例化 Debugware IP。并将需要观察信号接到 IP 的 data_in_n(n=0,1,2,3) 端口。

生成 IP 源文件时,UI 同时生成以图 2-3中 Module Name 命名的 *.adf 文件。该文件记录了 IP 使用的 LA Core 的配置信息:Core 使用的 Clock 名称、触发条件和 IP 使用的存储信息。在下文第4部分触发中,Real Time Debug 工具会加载 adf 文件中的初始触发条件。同时,adf 文件会记录用户自定义的触发条件。

运行流程

所有修改完成后,可依次运行综合、布局&布线和生成码流步骤,生成 *.acf 文件。

关闭调试

当完成当前调试过程后,您需要手动在工程源代码中删除 Debugware IP 的例化代码,重新运行流程生成新的 *.acf 文件。

自动添加 Debugware IP

除了上述介绍的手动例化 Debugware IP的方式,福晞软件还提供了 Debug Insert 工具。Debug Insert 是一款基于福晞综合网表 *.amv 文件进行调试的工具。因此,在使用 Debug Insert 工具之前,您需要提前运行综合,确保生成 *.amv 网表文件。

该工具在正确设置 LA Core 个数和选择待观察的信号后,会自动生成 *.dxc 约束文件。接下来,福晞运行流程时,福晞流程读取约束文件中 LA Core 的信息,在 *.amv 网表中自动添加 Debugware IP。

因此,该工具可以帮助用户在工程中自动添加 Debugware IP,这避免了用户手动修改 RTL 源代码,简化了 IP 添加的过程,在一定程度上提高了用户调试效率。

启动 Debug Insert 工具

依次选择Tools -> Debug Insert;

在Flow Navigator 窗口中, 依次选择Synthesize->Open Synthesized Design->Debug Insert;

在Project或者Hierarchy窗口中,新建 *.dxc 文件,双击 *.dxc 文件打开工具,如图 2-7。

图 2-7 Debug Insert 界面

设置 LA Core

在Core Setting页面,设置 LA Core参数:

Trigger Model:设置触发模式,可选项为:Single 和 Multiple;选择 Single 时,Debugware 不支持多窗口触发方式;选择 Multiple 时,支持多窗口触发模式。但 Multiple 模式下,窗口个数设为1时,不等价于 Single 模式。Multiple 模式使用的资源数量比 Single 模式多。

Core Name:设置 LA Core 的名称,名称需要保持唯一。

Memory Depth:设置 Debugware 使用 EMB 的深度,该值大小决定了触发时采样周期数。

Input DFF Level:设置待观测信号的打拍个数,范围0~6。说明:改善增加 Debugware IP 对用户逻辑性能的影响,值越大影响越小,推荐值为2。

Clock:在LA Core行Clock列对应单元格双击,弹出Search Design对话框如图 2-8,设置要观察信号所在时钟域。未设置 Clock 时,该单元格用红色标记,并显示N/A,如上图 2-7 Debug Insert 界面。

图 2-8 时钟选择

另外,可通过工具栏中⊗或者右键菜单“Remove Core”删除当前选中 LA Core。

注意

Debug Insert 工具无需设置数据位宽,工具会根据实际选择信号个数自动确定;

如果综合网表中没有有效时钟,LA Core 将无法选择时钟;

在保存时,如果 Clock 显示为 N/A(未配置),将不能保存。

选择观察信号

Debug Insert 工具提供了两种添加信号的方式:

在 RTL 中使用MARK_DEBUG宏标记观察信号(wire 或者 reg)。

使用 Debug Insert UI 对话框选择福晞综合 amv 网表中信号。

(1)使用MARK_DEBUG宏

在 RTL 源文件,找到对应的 reg 或者 wire 信号,在信号前添加属性:(* MARK_DEBUG = “YES” *),然后保存 RTL,如图 2-9所示。

图 2-9 MARK_DEBUG 宏

运行综合成功后,打开 Debug Insert,选择Create a new debug constraint file。Debug Insert 工具会自动加载 RTL中标记的信号。如图 2-10:

图 2-10 LA Core 页面

如图 2-10所示,工具会自动根据 MARK_DEBUG 标记的信号所属时钟域创建 LA Core。每个时钟域对应一个 LA Core,同时时钟域内的观察信号也对应添加到 LA Core 对应的被观察信号页面。

在被观察信号页面,RTL 中标记的信号和 UI 中手动添加的信号使用不同图标标记:

代表 RTL 标记,

代表 UI 手动添加,

如下图 2-11所示:

图 2-11 MARK_DEBUG 宏添加信号

(2)使用Debug Insert UI对话框

点击 LA Core 名称对应的页面,切换到被观察信号页面。在本页面可通过⊕或者右键“Add Nets”打开福晞综合 .amv 网表中所有 Net 信号集合对话框,如图 2-12。在本对话框中,依次选择观察信号,选择完成后,点击OK,选择信号将被添加到被观察信号页面。

图 2-12 可观察信号集合

Search Design窗口中,可根据Net Name进行查找。在该窗口中,Net 列表显示福晞综合 .amv 网表中所有的信号信息,表格有以下3列:

Net Name:信号的名称。

Status:显示该信号是否已经被添加到 LA Core 中,如果已经添加,

则以

标记。

Driver Module:显示该信号的驱动模块类型。

生成 *.dxc

在完成 LA Core 设置和选择完被观察信号后,可通过

Core 页面

或者右键菜单Generate弹出

Summary对话框,显示所有配置信息。在Summary对话框中(如图2-13),选择Generate,生成 *.dxc 文件,Debugware IP文件和 *.adf 文件。

注意

使用 Debug Insert 工具生成的 adf 文件为:fx_insert_debugware_v2_1,不可修改。

图 2-13 Summary 对话框

生成 *.dxc 文件后,该文件会自动加入工程,并显示在福晞软件的Hierarchy窗口和Project窗口,如图 2-14所示。编辑已存在 dxc 文件,可通过在 Hierarchy 或者 Project 窗口双击 .dxc 文件,打开 Debug Insert 工具。

图 2-14 Hierarchy 和 Project 窗口

运行流程

经过前边三个小节:

设置 LA Core,选择观察信号和生成 *.dxc;已经生成了

调试约束文件 *.dxc 和 *.adf 文件。*.dxc 文件记录了调试需要的 LA Core 设置以及需要观察的信号。 Debugware IP 的添加需要重新编译工程生成新的 *.acf 文件。

在 Console 窗口打印如下 log 信息,说明流程正常启动,如图 2-15。

图 2-15 Debug Insert 流程 log

关闭调试

完成调试流程后,您可以选择以下任意一种方式关闭调试流程:

在图 2-14Hierarchy或Project窗口中,选中 *.dxc 文件,在右键菜单中选择Remove From Project,移除 *.dxc 文件;

在图 2-7Debug Insert界面中,将Enable选项取消勾选。

注意

如图 2-1所示,由于芯片中有且只有一个 JTAG 模块,因此工程中不能同时使用手动例化 Debugware IP和自动添加 Debugware IP添加 IP。否则,运行流程时,将会报如下错:

ERROR : [PLACER 01201] : The cell JTAG_DBWV1 only one in device, so can't place u_debug_u_tap_genblk1_u_jtag.

如果 Placer 报上述错误,请检查您工程中是否同时例化了 IP 并添加了处于 Enable 状态的 .dxc 文件。

下载

通过前边介绍的手动例化 Debugware IP或自动添加Debugware IP方式,生成 *acf 码流文件后,

您可以通过

或者Tools->Downloader打开下载界面,

如图3-1所示。选择对应的 acf 文件,点击Program按钮下载码流至芯片。

图 3-1 Downloader 界面

(未完待续……)

-

FPGA

+关注

关注

1663文章

22494浏览量

638993 -

IP

+关注

关注

5文章

1882浏览量

156672 -

布线

+关注

关注

9文章

833浏览量

86248 -

调试工具

+关注

关注

1文章

59浏览量

13027

原文标题:福晞®软件调试工具介绍:工程添加 Debugware IP

文章出处:【微信号:HME-FPGA,微信公众号:HME京微齐力】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

福晞软件调试工具介绍之工程添加Debugware IP(2)

Nuclei Studio 编译调试工程

VB TCP/UDP Socket调试助手软件 Socket调试工具软件

介绍Lauterbach调试工具的应用

多核应用调试工具CodeViser介绍

京微齐力福晞软件全面提升设计师交互体验

福晞软件调试工具介绍之工程添加Debugware IP(1)

福晞软件调试工具介绍之工程添加Debugware IP(1)

评论