可重构计算芯片(Reconfigurable Computing Chip)是基于可重构计算架构设计的芯片。可重构计算是一种时空二维编程的并行计算模式。与之相对,传统的通用处理器是时域编程的计算模式,FPGA是空域编程的计算模式。可重构计算芯片是集成电路领域的颠覆性技术,具有广泛适用性。

所谓可重构计算是指在配置信息的控制下,利用系统中的可编程计算资源,根据应用的需要构造出最适配的计算架构,达到或接近专用集成电路的高性能。可重构计算的本质是通过多次重新配置可编程计算资源的功能和互连,使系统兼具高性能、低功耗、易维护、低成本等多种优良特性。

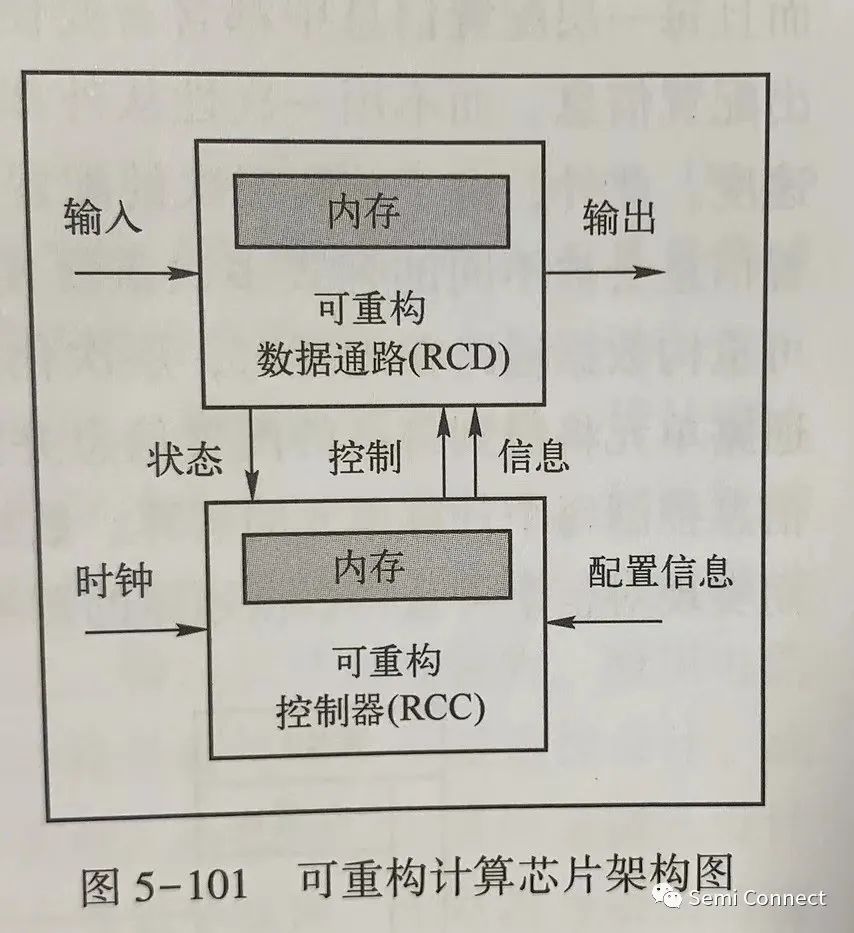

可重构计算芯片硬件架构由可重构数据通路(Reconfigurable Datapath,RCD)和可重构控制器(Reconfigurable Controller,RCC)两部分组成,如图5-101所示。其中可重构数据通路负责数据流的并行处理,可重构控制器负责配置信息管理和任务映射调度。在可重构数据通路负责数据流的并行处理,可重构控制器负责配置信息管理和任务映射调度。在可重构计算系统中,数据通路可通过调用或修改配置信息被动态重配,这样既保留了用定制电路(硬件方法)实现计算的性能,又具有用处理器方法(软件方法)实现计算的灵活性。

可重构计算芯片的配置策略可分为静态重构和动态重构。静态重构只能在可重构计算芯片的数据通路进行计算之前对其进行功能重构。静态重构只能在可重构计算芯片的数据通路进行计算之前对其进行对过大而无法对数据通路进行功能重构。最典型的具有静态重构特征的可重构计算芯片是FPGA。FPGA的常见工作方式是系统上电时从片外存储器中加载配置信息进行功能重构。FPGA配置信息的规模一般很大,重构过程通常会持续几十至几百毫秒甚至多大几秒的时间。等功能重构完成之后,FPGA才能进行相应的计算。

在计算过程中,FPGA的功能无法再被重构。如需重构,一定要首先中断FPGA当前正在进行的计算任务。因为是单比特编程器件(细粒度可重构计算芯片),所以FPGA的灵活性非常高,在不考虑容量的前提下几乎可以实现任何形式的数字逻辑。这也是FPGA能够在商业上获得极大成功的重要原因之一。然而,细粒度给FPGA带来了海量的配置信息,重构的时间代价和功耗代价就变得非常大。而典型的动态可重构芯片的重构时间一般在几纳秒到几十纳秒的范围。

由于功能重构的时间代价相对较小,可重构计算芯片的数据通路在计算过程中也能够进行功能重构的特性被称为动态重构。最典型的具有动态重构特性的可重构计算芯片是粗粒度可重构阵列(Coarse-Grained Reconfigurable Architecture, CGRA)。CGRA的常见工作方式是:在CGRA完成某个既定的计算任务之后,迅速对其加载新的配置比特流进行功能重构。重构过程通常仅会持续几个到几百个时钟周期。等功能重构完成之后,CGRA再继续执行该新配置的计算任务。

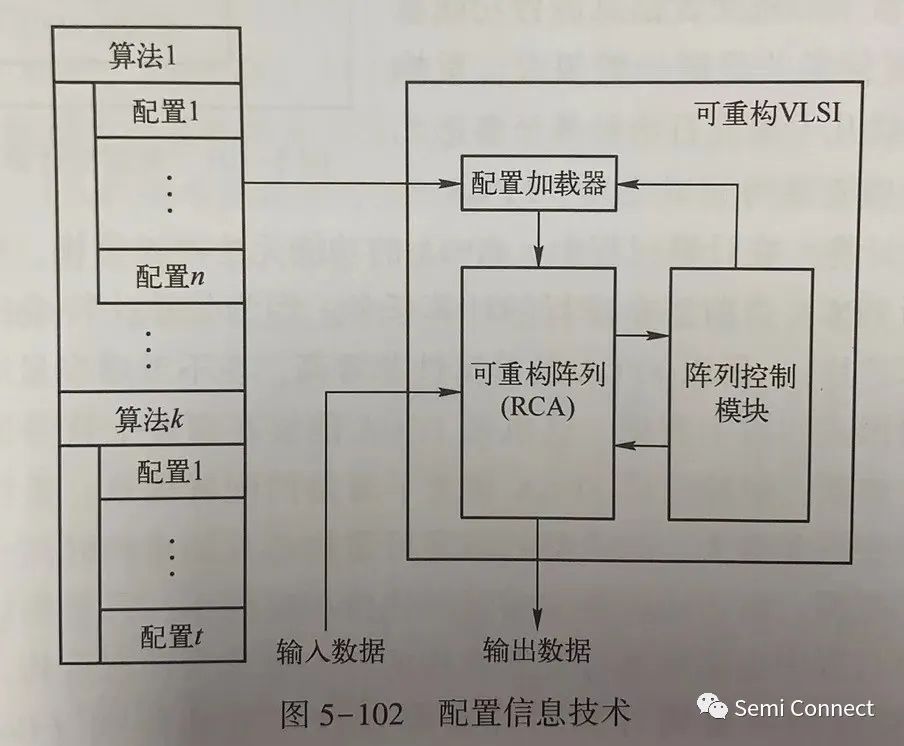

可重构计算芯片区别于其他电路实现形式的一大特点就是需要对数据通路进行配置,配置完成后它就像ASIC电路一样以较高的性能实现指定的功能。如图5-102所示,可重构数据通路通过配置加载器从外部加载配置,这部分构成了可重构数据通路的配置部分。缩短可重构数据通路通过配置加载器从外部加载配置,这部分构成了可重构数据通路的配置部分。缩短可重构数据通路的配置时间是十分重要的,这样可以很快地完成不同配置之间的切换,提高电路的实时响应能力。

常用的缩短配置时间的方式有两种:一是提高数据通路的粒度以减少配置信息的总量,配置时间相应减少;二是通过层次化的配置结构减少从数据通路外部输入的配置信息数量,并且实现对配置信息存储在不同的存储器中,而且每一层配置信息中都含有要使用的下一层配置信息的列表,这样逐层地调出配置信息,而不用一次性从外部将大量配置信息全部输入,从而提高了配置速度。此外,由于较高层次的配置信息只含有底层配置信息的列表,底层的配置信息会被不同的列表多次重复使用,从而达到了减少配置信息总量的目的。

可重构数据通路在配置时,层次化的配置结构被一层一层打开,最终每个数据通路单元将得到自己的配置信息并完成配置。数据通路控制模块通过解析配置信息控制每个计算单元的运算、数据的输入/输出、配置信息的加载时间等,从而实现对整个可重构数据通路的调度。

近年来,可重构计算技术已成为集成电路研究的新热点。可重构计算芯片具备硬件随软件变化而变化、软硬件双编程的特点,突破了传统的基于硬件进行软件编程的计算模式,实现了“电路跟随算法变,架构跟随应用变“的高能效动态可重构计算技术。

审核编辑 :李倩

-

芯片

+关注

关注

463文章

54410浏览量

469151 -

集成电路

+关注

关注

5464文章

12681浏览量

375670

原文标题:可重构计算芯片

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

安克创新发布Thus™芯片:存算一体架构重塑AI音频新生态

交流微电网架构设计:拓扑结构、核心组件与适配场景

西格电力微电网总体架构设计:分层分布式控制体系构建

2022全新版!Java分布式架构设计与开发实战(完结)

微电网总体架构设计原则:安全、高效、灵活的三重导向

光伏四可装置硬件平台架构详解:计算单元、通信接口与可靠性设计

嵌入式软件分层架构设计原则

AES和SM4算法的可重构分析

全球首款“可逆计算”冰河芯片诞生,相比普通芯片节能30%

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片到AGI芯片

智慧工厂的“隐形大脑”:边缘计算网关凭什么重构设备连接新逻辑?

AI芯片:加速人工智能计算的专用硬件引擎

工业4.0的“全能战士”——如何用一颗芯片重构智能工厂的算力版图?

清微智能官宣:国产可重构芯片全球出货量突破2000万颗

基于可重构计算架构设计的芯片

基于可重构计算架构设计的芯片

评论