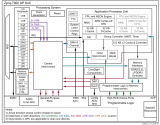

电可编程逻辑器件(Electrically Programmable Logic Device,EPLD)是指采用电信号的可擦可编程逻辑器件。

EPLD的设计流程通常有以下几个主要步骤:

1、使用原理图或者用硬件描述语言对逻辑进行设计描述;

2、在设计者把设计的逻辑编写到器件中之前,有必要对设计结果的正确性进行验证,一般通过计算机软件进行仿真,检查其是否符合设计需求,这称为“前仿”;

3、经过计算机软件编译转换为化简后的布尔代数表达式,编译软件将特定表达式适配进相对应的器件,生成器件的标准装载文件(JED文件),通常将这个过程称为“综合”;

4、把逻辑下载到器件中进行功能检测。

通常可以用原理图或硬件描述语言来设计EPLD器件的逻辑功能。原理图描述非常直观,直接用电路器件来描述电路功能,缺点是不够简洁。常用的硬件描述语言有Verilog、VHDL语言等。硬件描述语言可以精确地实现电路的逻辑功能。

对于仿真和综合,目前比较常用的工具有Modelsim、Quartus等。编程器是一种专门对可编程器件进行编程的设备。需要通过编程器将JED文件下载到器件中让芯片按照设计逻辑工作。编程下载的过程是指计算机把JED文件下载到编程器中,再根据器件特点把JED文件写入器件内部。

审核编辑 :李倩

-

EPLD

+关注

关注

0文章

8浏览量

10818 -

可编程逻辑器件

+关注

关注

5文章

145浏览量

31036

原文标题:电可编程逻辑器件EPLD

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

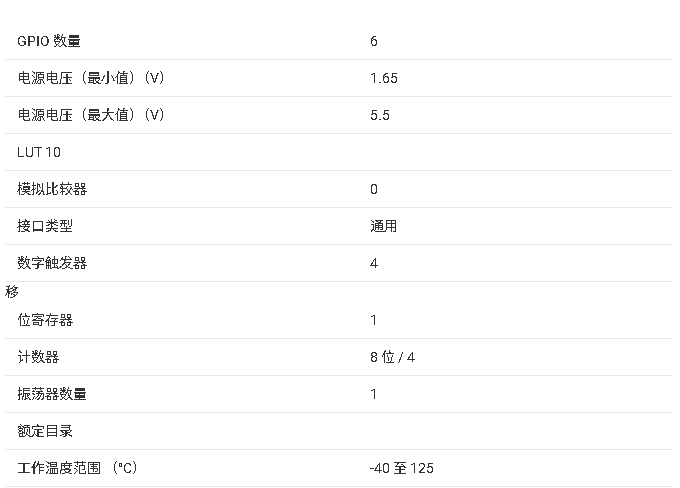

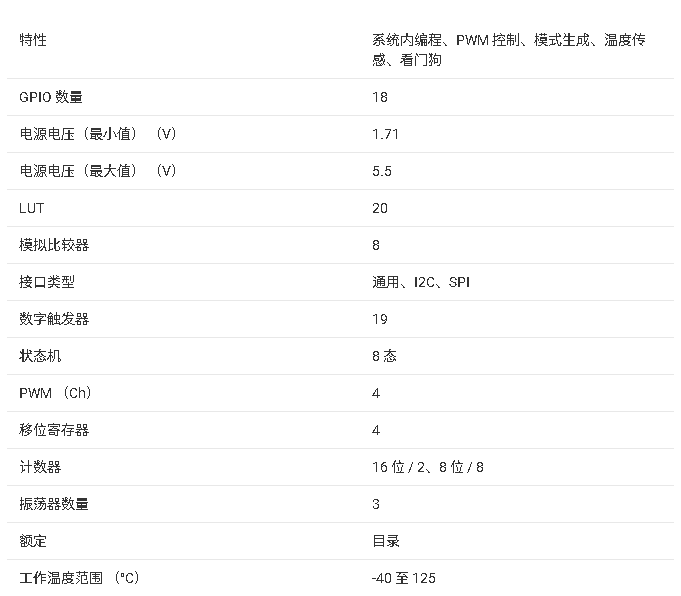

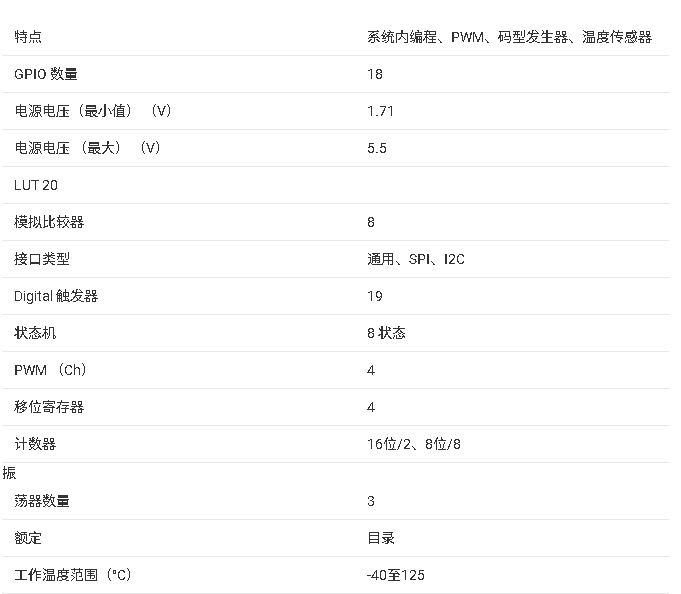

PSoC 4200L:可编程系统芯片的卓越之选

探索UPSD3212A/C/CV:集成8032 MCU、USB与可编程逻辑的闪存可编程系统设备

SDRAM工业动态随机存储器在可编程逻辑控制器(PLC)的应用

西门子交通与罗彻斯特电子合作的成功案例

Zynq全可编程片上系统详解

罗彻斯特电子为Lattice产品提供持续供货支持

思尔芯邀您共聚 FPT 2025,赋能可编程技术新未来

电可编程逻辑器件EPLD的设计流程

电可编程逻辑器件EPLD的设计流程

评论