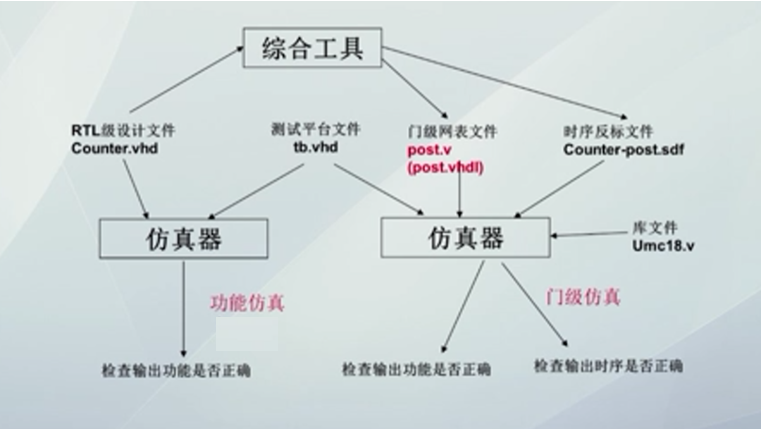

经过逻辑综合过程后,Verilog代码被转化成门级网单,转化后的门级网单需要被验证与Verilog代码功能是否一致,需要进行门级仿真。

Verilog代码的仿真可以被称为功能仿真,可以验证Verilog代码功能与设计需求是否一致。

验证Verilog代码过程中需要编写测试平台文件tb.vhd,该平台文件仍可以在门级仿真中使用。门级仿真所用的仿真器(仿真工具,如

Modelsim)与功能仿真相同,门级仿真还需要逻辑综合保存的文件:门级网表文件和时序反标文件(时序相关信息),门级网表文件所用的底层电路(如:与门)的特性信息在库文件中,库文件由芯片制造公司提供,各个芯片制造公司的库文件因其元器件性能的差异而不同。

综上,门级仿真基于测试平台文件、门级网表文件、时序反标文件、库文件,可以进行更精确的仿真。设计人员除了可以通过门级仿真验证门级网单与Verilog代码功能是否一致,还可以检查门级电路的时序是否正确。

图片来源:学堂在线《IC设计与方法》

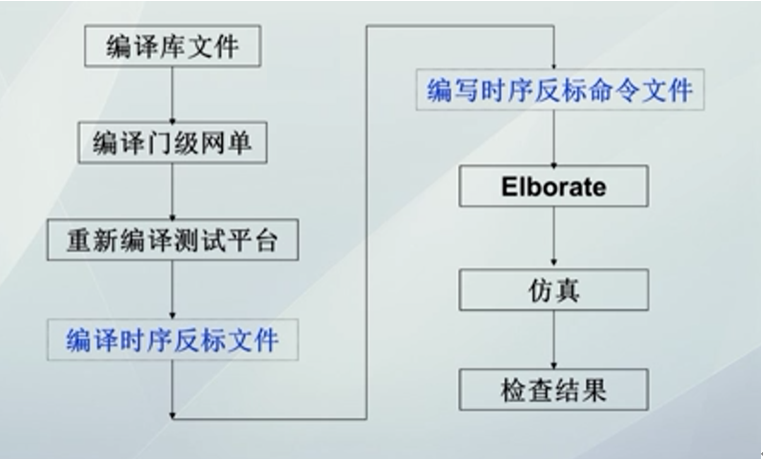

门级仿真的过程与功能仿真过程相类似,不同之处在于需要将库文件重新编译,库文件编译结束后,依次编译门级网单、测试平台、时序反标文件,并编写时序反标的命令文件。

如果仿真工具采用Modelsim,时序反标文件可以内嵌在Modelsim工具中,不需编译。如果采用NC仿真工具,还需要进行Elborate(个人理解Elborate步骤是进行精细化的设定)。

最后进行仿真并检查结果。

图片来源:学堂在线《IC设计与方法》

编译库文件时,需将底层门级电路单独建立库,而不能将库文件混入到芯片设计代码中。这是因为库文件中有数百个元器件,混入芯片设计代码中,难以定位由设计人员自主设计的部分。

因为设计方案最终确定前需要反复修改,所以编译过程会反复进行,库文件也需要重新编译,需要及时清理过去编译的内容。

因为门级网单的仿真步长(根据网络资料理解:连续系统仿真中设置的最小时间间隔)和库文件的仿真步长不一定相同,需要设置统一的仿真步长。底层单元库(库文件)仿真步长通常设置在ps(皮秒,1s=10-12s)量级,设计人员编写的芯片代码仿真步长通常设置在ns(纳秒,1ns=10-9s)量级。

进行门级仿真前,时序反标信息需要标注到门级网单中。标注方式采用Verilog代码中$sdfannotate系统任务,$sdfannotate系统任务可以向仿真工具输入门级网单的时序信息。

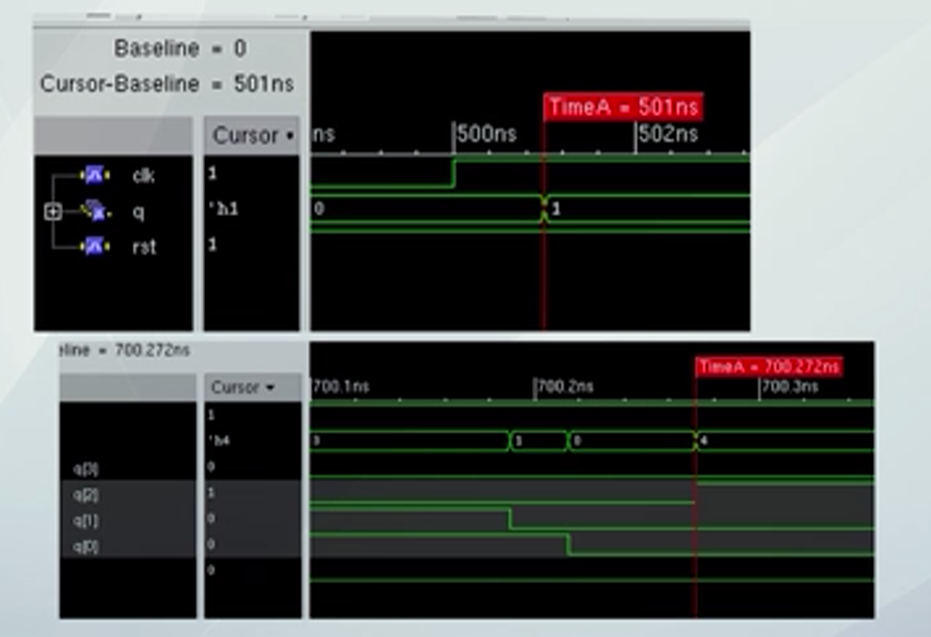

下图是门级仿真的结果。偏上的图片中,延时显示的是1ns,长于门元器件的延时,意味着时序反标可能不正确。当时序反标不正确时,库文件会采用默认延时,即该库文件的默认延时是1ns。时序反标不正确的原因可能是反标文件名错误、反标流程错误等。

偏下的图片是反标正确的结果,延时在0.1ns左右。正常情况下,下图所映射的电路输出应该从3直接变为4,但实际输出由3变为1,再变为0,再变为4,所对应的波形会显示出毛刺。如果该输出只作为状态信号(只在信号稳定时作为输入)或输出指示(如指示发光二极管发光),没有什么影响,其他情况需要考虑毛刺的影响。

图片来源:学堂在线《IC设计与方法》

审核编辑 :李倩

-

仿真

+关注

关注

53文章

4406浏览量

137665 -

Verilog

+关注

关注

30文章

1370浏览量

114125

原文标题:芯片设计相关介绍(26)——门级仿真

文章出处:【微信号:行业学习与研究,微信公众号:行业学习与研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

车规级与消费级芯片的差异与影响

英飞凌IPOSIM平台加入基于SPICE的模型生成工具,助力提升系统级仿真精度

双级式光伏发电并网系统实时仿真

康谋分享 | 物理级传感器仿真:破解自动驾驶长尾场景验证难题

EGBox:一体化工业级实时仿真旗舰平台,全功能覆盖

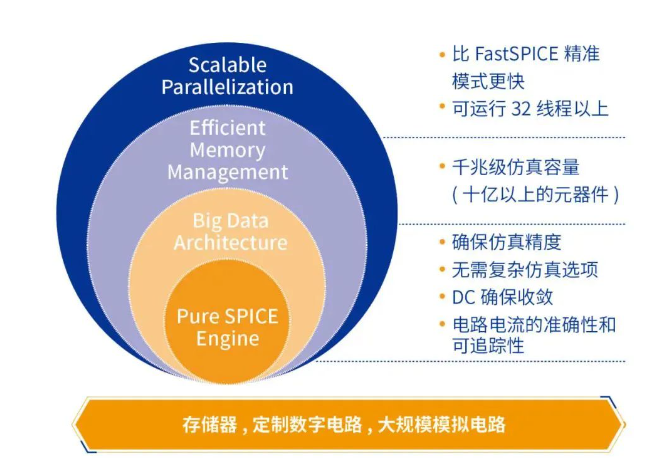

概伦电子千兆级高精度电路仿真器NanoSpice Giga介绍

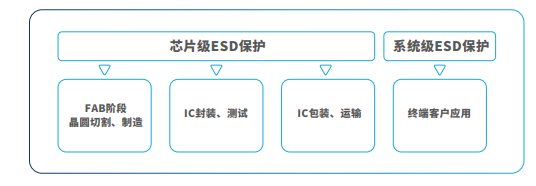

概伦电子芯片级HBM静电防护分析平台ESDi介绍

光伏发电系统篇:单级式并网系统实时仿真

光伏发电系统篇:单级式并网系统实时仿真

芯片设计之门级仿真

芯片设计之门级仿真

评论