声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半导体

+关注

关注

328文章

24545浏览量

202243 -

蚀刻工艺

+关注

关注

2文章

51浏览量

11677

发布评论请先 登录

相关推荐

半导体发展的四个时代

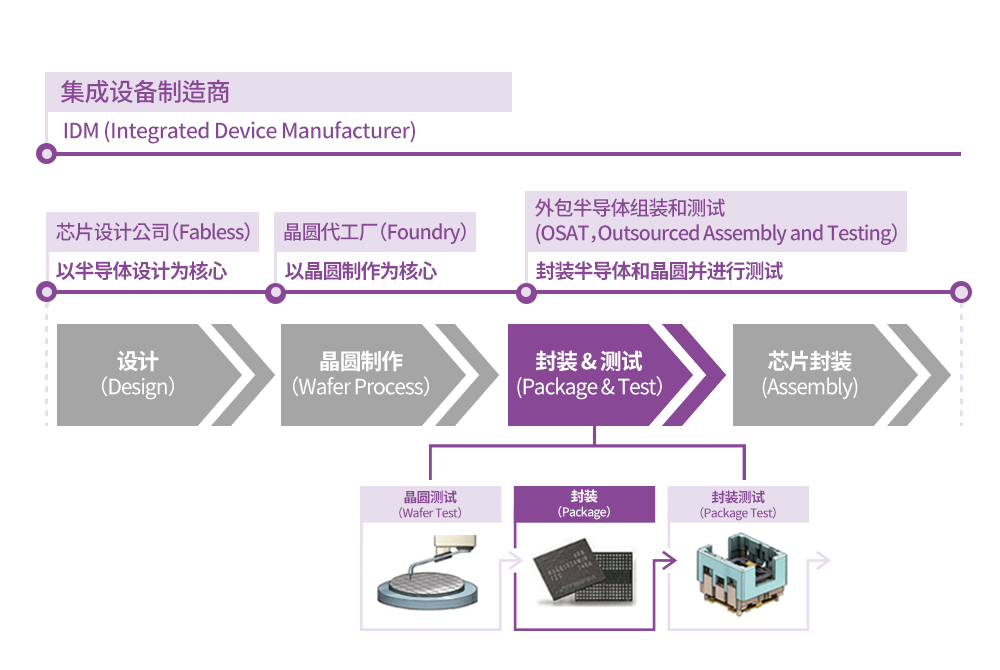

个生态系统,让每家公司都能够专注于他们的核心竞争力,这是管理复杂性的一个好方法。这就是第三个时代所发生的事情。芯片的设计和实施由无晶圆厂半导体公司负责,设计基础设施由 EDA 公司负责,工艺技术则交给

发表于 03-27 16:17

半导体发展的四个时代

一个生态系统,让每家公司都能够专注于他们的核心竞争力,这是管理复杂性的一个好方法。这就是第三个时代所发生的事情。芯片的设计和实施由无晶圆厂半导体公司负责,设计基础设施由 EDA 公司负责,工艺技术则

发表于 03-13 16:52

PCB的蚀刻工艺及过程控制

另外一种工艺方法是整个板子上都镀铜,感光膜以外的部分仅仅是锡或铅锡抗蚀层。这种工艺称为“全板镀铜工艺“。与图形电镀相比,全板镀铜的缺点是板面各处都要镀两次铜而且蚀刻时还必须都把它们腐蚀

发表于 12-06 15:03

•451次阅读

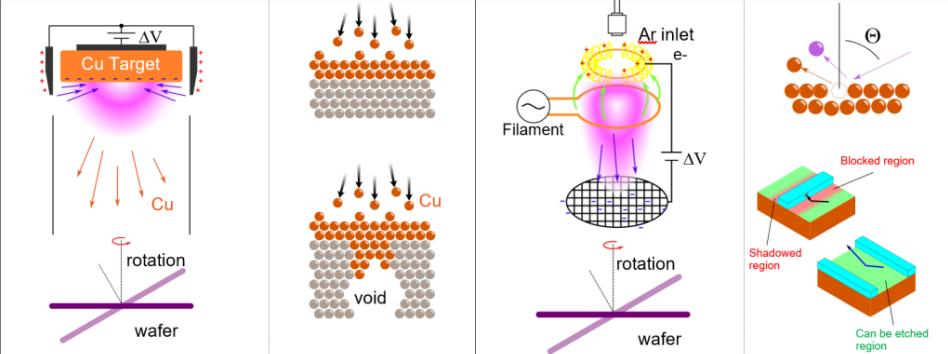

降低半导体金属线电阻的沉积和蚀刻技术

铜的电阻率取决于其晶体结构、空隙体积、晶界和材料界面失配,这在较小的尺度上变得更加重要。传统上,铜(Cu)线的形成是通过使用沟槽蚀刻工艺在低k二氧化硅中蚀刻沟槽图案,然后通过镶嵌流用Cu填充沟槽来完成的。

PCB线路板的蚀刻工艺需要注意哪些细节问题

一站式PCBA智造厂家今天为大家讲讲pcb打样蚀刻工艺注意事项有哪些?PCB打样蚀刻工艺注意事项。PCB打样中,在铜箔部分预镀一层铅锡防腐层,保留在板外层,即电路的图形部分,然后是其余的铜箔被化学方法腐蚀,称为蚀刻。

浅谈PCB蚀刻质量及先期存在的问题

要注意的是,蚀刻时的板子上面有两层铜。在外层蚀刻工艺中仅仅有一层铜是必须被全部蚀刻掉的,其余的将形成最终所需要的电路。这种类型的图形电镀,其特点是镀铜层仅存在于铅锡抗蚀层的下面。

发表于 09-07 14:41

•606次阅读

pcb蚀刻是什么意思

在印制板外层电路的加工工艺中,还有另外一种方法,就是用感光膜代替金属镀层做抗蚀层。这种方法非常近似于内层蚀刻工艺,可以参阅内层制作工艺中的蚀刻。

发表于 09-06 09:36

•966次阅读

如何实现PCB蚀刻工艺中的均匀性呢?有哪些方法?

PCB蚀刻工艺中的“水池效应”现象,通常发生在顶部,这种现象会导致大尺寸PCB整个板面具有不同的蚀刻质量。

发表于 08-10 18:25

•1188次阅读

半导体前端工艺:沉积——“更小、更多”,微细化的关键(上)

在半导体制程中,移除残余材料的“减法工艺”不止“刻蚀”一种,引入其他材料的“加法工艺”也非“沉积”一种。比如,光刻工艺中的光刻胶涂敷,其实也是在基底上形成各种薄膜;又如氧化

半导体八大工艺之刻蚀工艺-干法刻蚀

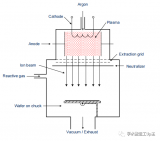

离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对

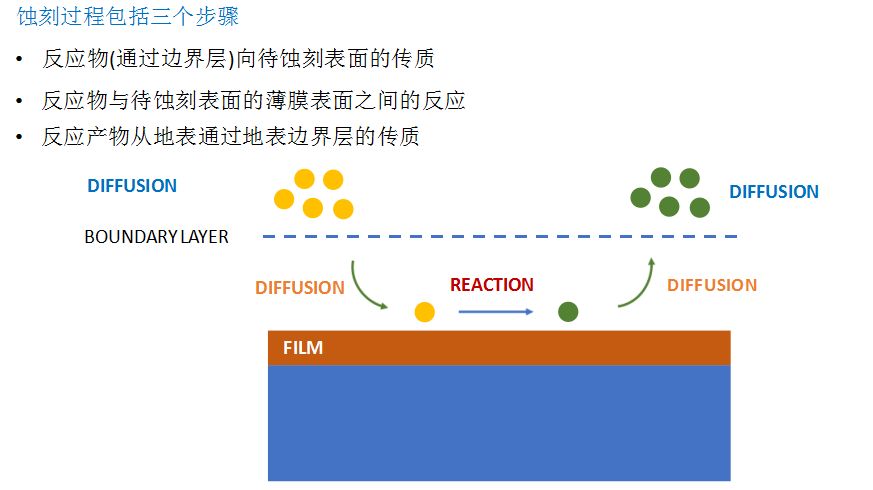

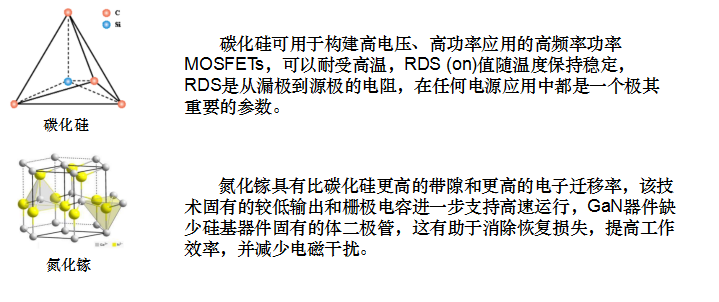

半导体蚀刻工艺课堂素材分享(3)(三)

半导体蚀刻工艺课堂素材分享(3)(三)

![[<b class='flag-5'>半导体</b>前端<b class='flag-5'>工艺</b>:第二篇] <b class='flag-5'>半导体</b>制程<b class='flag-5'>工艺</b>概览与氧化](https://file1.elecfans.com/web2/M00/B1/D7/wKgZomVdeemAEcbqAAInhahz1Ko856.png)

评论