现在科技越来越发达,芯片设计也在不断创新与突破,前段时间IBM就研制出了全球首颗2nm芯片,这颗芯片能够容纳500亿个晶体管,它的最小单元比DNA的单链还要小。2nm芯片的到来,在半导体行业影响重大,台积电随之也宣布了联合台达和麻省理工在一纳米芯片领域取得了关键性的进展,所以很多小伙伴都想知道芯片工艺的极限在哪里?我们就来了解下1nm芯片的工艺是否已经是到达了极限?

其实现在芯片的特征尺寸只是一个代号,只要性能、密度能够提升30%—50%就能出现新一代的工艺技术,所以芯片的工艺极限是不可预估的,1nm也不是芯片工艺的极限。

总的来说,芯片工艺技术发展肯定是越来越小的,因为人们对于性能的追求是永无止境的,所以芯片1nm之后肯定是还能再小的,只是时间问题。

审核编辑;chenchen

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

462文章

53581浏览量

459550 -

1nm

+关注

关注

0文章

16浏览量

4073

发布评论请先 登录

相关推荐

热点推荐

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

最近扒了扒国产芯片的进展,发现中芯国际(官网链接:https://www.smics.com)的 14nm FinFET 制程已经不是 “实验室技术”

发表于 11-25 21:03

台积电2纳米制程试产成功,AI、5G、汽车芯片

又近了一大步。 这一历史性节点不仅意味着制程技术的再度跨越,也预示着未来AI、通信与汽车等核心领域即将迎来一场深刻的“芯革命”。 1、技术再突破 与现行的3nm工艺相比,台积电

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

个先例,其变化形式如图6所示。

晶背供电技术已被证明,它可以很好地解决5nm以下芯片的电源完整性问题,同样也证明

它是优化特定版图设计任务的用力工具。

图6 功能性晶

随着工艺创新的层出不穷,相信摩尔神话

发表于 09-06 10:37

下一代高速芯片晶体管解制造问题解决了!

在半导体工艺演进到2nm,1nm甚至0.7nm等节点以后,晶体管结构该如何演进?2017年,imec推出了叉片晶体管(forksheet),作为环栅(GAA)晶体管的自然延伸。不过,产

发表于 06-20 10:40

手机芯片进入2nm时代,首发不是苹果?

电子发烧友网综合报道,2nm工艺制程的手机处理器已有多家手机处理器厂商密切规划中,无论是台积电还是三星都在积极布局,或将有数款芯片成为2nm工艺

发表于 03-14 00:14

•2342次阅读

1nm光谱分辨率1200条光谱通道在高光谱相机行业是什么水平?

随着科技的发展,高光谱成像技术因其能够提供丰富的物质信息而受到越来越多的关注。本文主要探讨了1纳米(nm)光谱分辨率和1200条光谱通道配置对于高光谱相机性能的影响及其在不同领域的应用潜力。 高光谱

集成电路制造工艺中的伪栅去除技术介绍

厚度成为影响晶体管性能的关键因素。然而,栅氧厚度的减小极限受到隧穿漏电效应的限制,当氧化硅层薄至2nm以下时,隧穿漏电现象变得显著,且随厚度减小呈指数级增长,使得1nm以下的栅氧厚度变得不切实际。 为了克服这一挑战,英特尔

欧洲启动1nm及光芯片试验线

高达14亿美元,不仅将超越当前正在研发的2nm工艺技术,更将覆盖从1nm至7A(即0.7nm)的尖端工艺领域。NanoIC试验线的启动,标志

ADS1292R的PGA2N输出3.3V是不是芯片出问题了?

ADS1292R大家好,今天遇到个问题,做了个ADS1292R的心电放大电路。之前可以出波形,但是工频干扰好严重,今天上午再测,开始还比较正常,但是后来就不正常了,程序没有改动,PGA2N输出3.3V,PGA2P输出0V,3.3是芯片

发表于 01-20 09:37

OptiFDTD应用:用于光纤入波导耦合的硅纳米锥仿真

介绍

在高约束芯片上与亚微米波导上耦合光的两种主要方法是光栅或锥形耦合器。[1]

耦合器由高折射率比材料组成,是基于具有纳米尺寸尖端的短锥形。[2]

锥形耦合器实际上是光纤和亚微米波导之间的紧凑模式

发表于 01-08 08:51

过期的锡膏是否还能再使用?

过期的锡膏是否还能再使用,取决于多个因素,包括锡膏的储存条件、过期时间以及锡膏本身的特性。以下是对过期锡膏能否再使用的详细分析:

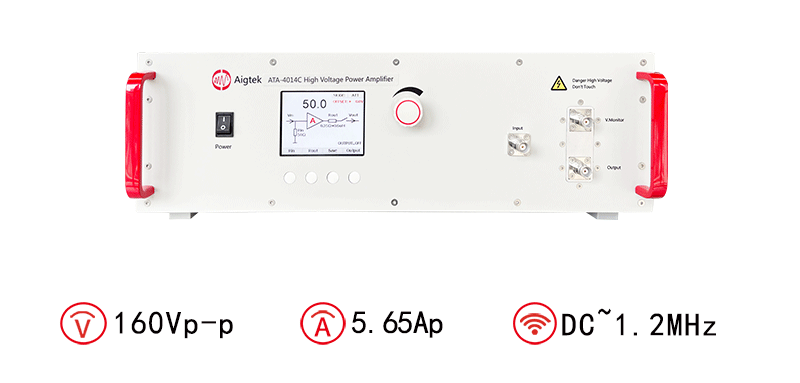

Aigtek功率放大器如何帮助制备(1~100nm)级的纳米薄膜

材料、平面显示器、超导材料、气体催化材料、过滤器材料、光敏材料、高密度的磁性记录材料。那么 功率放大器 可以帮助制备(1~100nm)级的纳米薄膜吗? 首先,我们来聊一聊纳米薄膜材料的

ADS1118初始化的时候是不是送寄存器A0P1就可以了,不需要再送A2P3?

A0p1 或A2p3就可以读取相应的差分值。

2、想知道初始化的时候是不是送寄存器A0P1就可以了,不需要再送A2P3.

发表于 12-19 08:09

1nm工艺是不是极限了 芯片1纳米后还能再小吗

1nm工艺是不是极限了 芯片1纳米后还能再小吗

评论