说说latch与verilog的联系。

还是照惯例,首先必须放上关于latch的定义和解释。ALTERA 的recommended HDL coding中提到:

A latch is a small combinational loop that holds the value of a signal until a new value is assigned.

从上可以看出,latch是一个记忆元件或者说是存储单元,他能保持信号的值

同时在网上找了找关于latch的中文定义。

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

从一般情况来看,锁存器多数是有电平锁存的。当电平无效时,输出信号随输入信号变化,就像通过了缓冲器;当电平有效时,输出信号被锁存。

看了很多关于verilog的语法资料,大多其中并没有谈到latch,latch和verilog发生联系是在用verilog进行FPGA或者ASIC设计时。而在此由于本人正式学习用verilog进行FPGA设计,

而涉及到的书中均提到要采用同步设计,避免采用latch。从网上找了找为什么不使用latch的原因:

不要锁存器的原因有二:1、锁存器容易产生毛刺,2、锁存器在ASIC设计中应该说比ff要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和ff来组成锁存器,这样就浪费了资源。3、锁存器的出现使得静态时序分析变得更加复杂

所以又可以得出一条指导性的原则:

在能使用DFF或者寄存器的时候,坚决不使用latch

说了latch的定义和latch的危害,现在要来说说latch的产生和避免

查阅资料,结合自己的理解,总结出无意生成latch的三大原因:

1、不完整的if或者case结构

2、不完整的敏感信号列表

latch的出现总是与不完整有关,组合电路本应该是完整的,最理想的写法可能是一个输入对应一个输出,当一个输入没有相应的输出或者引起输出的信号没有作为输入的时候,Latch产生了!

先解释第一点不完整的if结构,例如:

if(a)

begin

out = 1'b1;

end

当a为1时输出为1,当a为0时由于没有相应的译码语句,所以输出将保持,此时将生成latch而不是原来想要的组合电路。

而对于不完整的case语句,例如:

always@( * )

case(a)

3'b000: b = 8'd1;

3'b001: b = 8'd5;

3'b010: b = 8'd8;

3'b011: b = 8'd17;

endcase

此时语句中没有default,当a为4、5、6、7时没有响应的译码语句,输出将保持,此时将生成latch。

对于第二点不完整的敏感信号表,夏雨闻老师的书中有提到:

如是说道:在赋值表达式右边参与赋值的信号都必须在always@(敏感电平列表)中列出。

如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,那么在综合时,将会为该没有列出的信号隐含地产生一个透明锁存器。

所以得出指导性的原则:

务必写好if和case所有的分支,务必写全敏感信号列表!

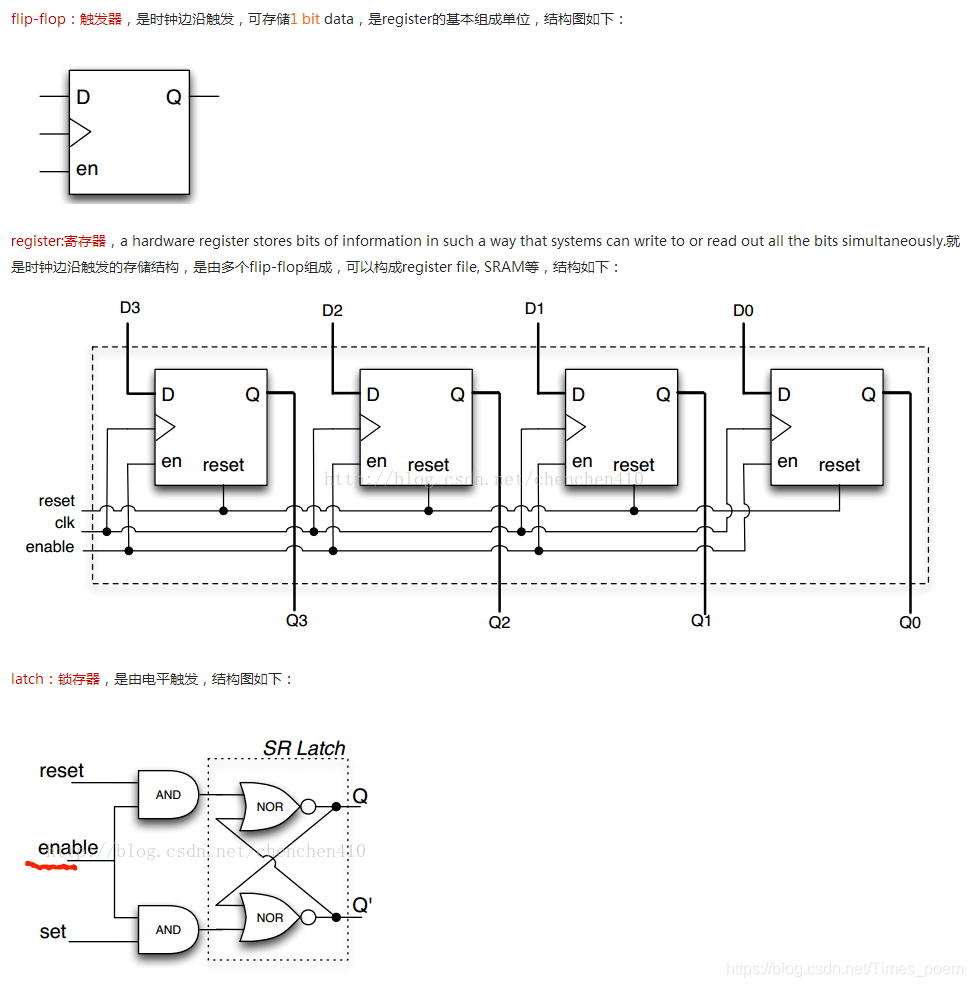

关于硬件中常见的基本存储元件的定义、中英文对应的名字会模糊,今天特地查明具体定义。

触发器:flipflop

锁存器:latch

寄存器:register

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,仅当锁存器处于使能状态时输出才会随着数据输入发生变化。

触发器是边沿敏感的存储单元,数据存储的动作由某一信号的上升或者下降沿进行同步的。

寄存器用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。触发器是在时钟的沿进行数据的锁存的,而锁存器是用电平使能来锁存数据的。所以触发器的Q输出端在每一个时钟沿都会被更新,而锁存器只能在使能电平有效器件才会被更新。有一些教科书里的触发器实际是锁存器。在FPGA设计中建议如果不是必须那么应该尽量使用触发器而不是锁存器。

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

20、D 触发器和D 锁存器的区别。

两个锁存器可以构成一个触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

21、latch和filp-flop的异同

都是时序逻辑,但latch受所有的输入信号控制,只要输入信号变化,latch就变化。也正因为如此,latch很容易出毛刺。

flip-flop是触发器,只有在被时钟触发时才采样当前的输入,产生输出。如果使用门电路来搭建latch和ff,则latch消耗的门资源比ff要少。但是你用的如果是 fpga,那么内部一般带DFF单元,反而用触发器更好。

22、latch与register的区别,

为什么现在多用register.行为级描述中latch如何产生的行为级描述中latch一般是由于if或case逻辑表述不完全产生的。

异同:

1、 latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。

DFF由时钟沿触发,同步控制。

2、 latch容易产生毛刺(glitch),DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用 latch的集成度比DFF高。

但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。

4、 latch将静态时序分析变得极为复杂。

一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。有些地方没有时钟,也只能用latch了。比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用 latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。

关于latch的讨论 latch和flip-flop都是时序逻辑,区别为:

latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;

flip- flop受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。当然因为二者都是时序逻辑,所以输出不但同当前的输入相关还同上一时间的输出相关。

1、没有时钟端,不受系统同步时钟的控制,无法实现同步操作;

2、对输入电平敏感,受布线延迟影响较大,很难保证输出没有毛刺产生;

在 xilinx和altera器件的slice和LE中都能够同时支持生产d-latch和d-ff,在这一层面上二者有什么区别暂时没有想到。如果使用门电路来搭建latch和ff,则latch消耗的门资源比ff要少,这是latch比ff优越的地方。latch的最大缺点就是没有时钟端,和当前我们尽可能采用时序电路的设计思路不符。latch是电平触发,相当于有一个使能端,且在激活之后(在使能电平的时候)相当于导线了,随输出而变化,在非使能状态下是保持原来的信号,这就可以看出和flip-flop的差别,其实很多时候latch是不能代替ff的

1.latch对毛刺敏感

2.在ASIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现

3.latch将静态时序分析变得极为复杂

4. 目前latch只在极高端电的路中使用,如intel 的P4等CPU。FPGA中有latch单元,寄存器单元就可以配置成latch单元,在xilinx v2p的手册将该单元成为register/latch单元,附件是xilinx半个slice的结构图。其它型号和厂家的FPGA没有去查证。——个人认为xilinx是能直接配的而altera或许比较麻烦,要几个LE才行,然而也非xilinx的器件每个slice都可以这样配置altera的只有DDR接口中有专门的latch单元,一般也只有高速电路中会采用latch的设计。altera的LE是没有latch的结构的又查了sp3和sp2e,别的不查了,手册上说支持这种配置。有关altera的表述wangdian说的对,altera的ff不能配置成latch,它使用查找表来实现latch,

一般的设计规则是:在绝大多数设计中避免产生LATCH.它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出.latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。有些地方没有时钟,也只能用latch了。

对latch进行STA的分析其实也是可以,但是要对工具相当熟悉才行.不过很容易出错.当前PrimeTime,是支持进行latch分析的.现在一些综合工具内置的STA分析功能也支持比如RTL compiler, Design Compiler. 除了ASIC里可以节省资源以外。我感觉latch这个东西在同步设计里出现的可能还是挺小的吧,现在处理过程中大都放在ff里打一下,影响不太大吧

标签:无标签latch与DFF的区别收集了一下网上资源,总结如下:

1、latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

2、latch容易产生毛刺(glitch),DFF则不易产生毛刺。

3、如果使用门电路来搭建latch和DFF,则latch消耗的门资源比DFF要少,这是latch比DFF优越的地方。所以,在ASIC中使用latch的集成度比DFF高,但在FPGA中正好相反,因为FPGA中没有标准的latch单元,但有DFF单元,一个LATCH需要多个LE才能实现。

4、latch将静态时序分析变得极为复杂。一般的设计规则是:在绝大多数设计中避免产生latch。它会让您设计的时序完蛋,并且它的隐蔽性很强,非老手不能查出。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。有些地方没有时钟,也只能用latch了。比如现在用一个clk接到latch的使能端(假设是高电平使能),这样需要的setup时间,就是数据在时钟的下降沿之前需要的时间,但是如果是一个DFF,那么setup时间就是在时钟的上升沿需要的时间。这就说明如果数据晚于控制信号的情况下,只能用 latch,这种情况就是,前面所提到的latch timing borrow。基本上相当于借了一个高电平时间。也就是说,latch借的时间也是有限的。在if语句和case不全很容易产生latch,需要注意。VIA题目这两个代码哪个综合更容易产生latch:

代码1

always@(enableorinaorinb)

begin

if(enable)begin

data_out=ina;

end

elsebegin

data_out=inb;

end

end

代码2

input[3:0]data_in;

always@(data_in)

begin

case(data_in)

0:out1=1'b1;

1,3:out2=1'b1;

2,4,5,6,7:out3=1'b1;

default:out4=1'b1;

endcase

end

答案是代码2在综合时更容易产生latch。

使用条件语句不当在设计中生成了原本没有想到的锁存器:、

例1:在一个always语句中不正确使用if语句

Always@(alord)always@(alord)

begin begin

if(al)q<= d; if(al) q <= d;

end elseq<= 0;

end

在这个always块中,if语句只保证了当al=1时q才取d的值。这段程序并没有给出当al=0时q的取值,那么当al=0时q取何值?在always块中在给定的条件下变量没有被赋值,那么变量将保持原值,也就是说将会生成一个锁存器。

如果当设计人员希望当al=0时,q的值为0,则else项就必不可少了。请注意看右边的always块,整个verilog程序模块综合出来后,always块对应的部分不会生成锁存器。

Verilog HDL程序的另一种偶然生成锁存器是在使用case语句时缺少default项的情况下发生的。

Case语句的功能是:在某个信号取不同的值时,给另一个信号赋不同的值。如下,如果sel=00,q取a值,而sel=11,q取b值。这个例子不清楚的是:如果sel取00和11以外的值时q将赋予什么值?在这个例子中,默认q保持原值,这就会自动生成锁存器。

always@(sel[1:0]oraorb)always@(sel[1:0]oraorb)

case(sel[1:0])case(sel[1:0])

2’b00:q<= a; 2’b00: q <= a;

2’b11:q<= b; 2’b11: q <= b;

endcase default:q<= ‘b0;

endcase

有锁存器无锁存器

避免生成锁存器的方法:如果用到if语句,最好写上sles项;如果用case语句,最好写上default项。遵循上面两条原则,就可以避免发生这种错误,使设计者更加明确设计目标,同时也增强了verilog程序的可读性。

原文标题:FPGA学习-verilog(flipflop和latch以及register的区别)

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22504浏览量

639305 -

寄存器

+关注

关注

31文章

5620浏览量

130428 -

硬件

+关注

关注

12文章

3635浏览量

69172 -

锁存器

+关注

关注

8文章

958浏览量

45477

原文标题:FPGA学习-verilog(flipflop和latch以及register的区别)

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体中常见的载流子散射机制

新思科技发布全新软件定义硬件辅助验证解决方案

学习电子电路中常见的问题

深入解析IPM器件数据手册中的电流定义:Ic、Icp、Io(peak)和Io(rms)

晶振使用中常见问题与解决方法

硬件消抖方案元件参数的计算方法

常见的电能质量在线监测装置硬件故障有哪些?

自动驾驶中常提的硬件在环是个啥?

CPM系列核心板,一款存储灵活的嵌入式核心板

IEC 62353中常用的术语和定义

【HarmonyOS 5】鸿蒙中常见的标题栏布局方案

SMT 料号怎么构成?这些常见电子元件别再傻傻分不清

硬件中常见的基本存储元件的定义

硬件中常见的基本存储元件的定义

评论