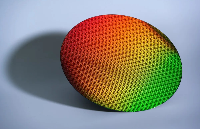

通过调节稳态PEB温度分布实现DI CD的可控性

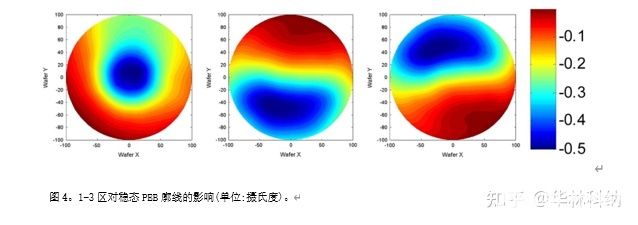

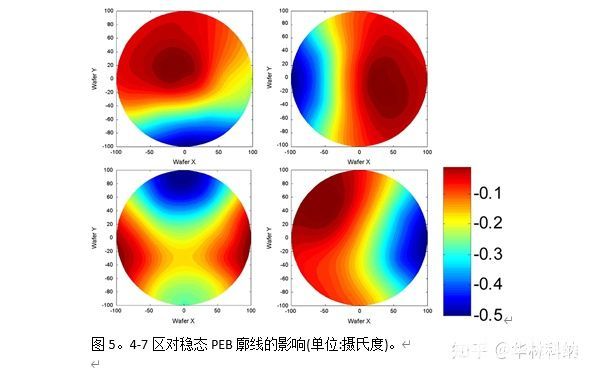

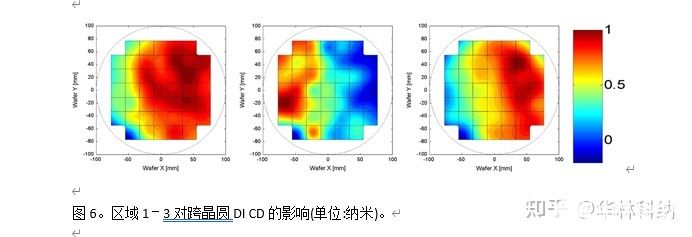

我们提出的CDU控制方法的一个基本假设是,通过多层烘烤板的区域控制器偏移调整来调整整个晶片的稳态PEB温度分布,可以有效地控制整个晶片的DI CD。这通过在设计实验的一次运行中DI CD和PEB温度分布之间的相关性分析来验证,其中故意提高晶片下半平面中的局部PEB温度,以便降低那里的局部DI CD。图10示出了稳态PEB温度与具有0.82的的DI CD强烈相关。

CDU控制和CDU控制方法

A.具有CD到偏移模型的DI CDU控制方法

只要光刻序列中的CD变化源(例如抗蚀剂厚度变化和显影变化)是系统的和稳定的,并且所产生的CD变化是系统的和稳定的,调整多层烘烤板的PEB分布以补偿这些系统的CD干扰并改善CDU是可行的。该方法依赖于通过诸如CD-SEM或散射测量法的计量工具对系统的跨晶片CD变化的精确捕获,以及对多区PEB烘烤板上PEB温度的空间分布的有效控制。

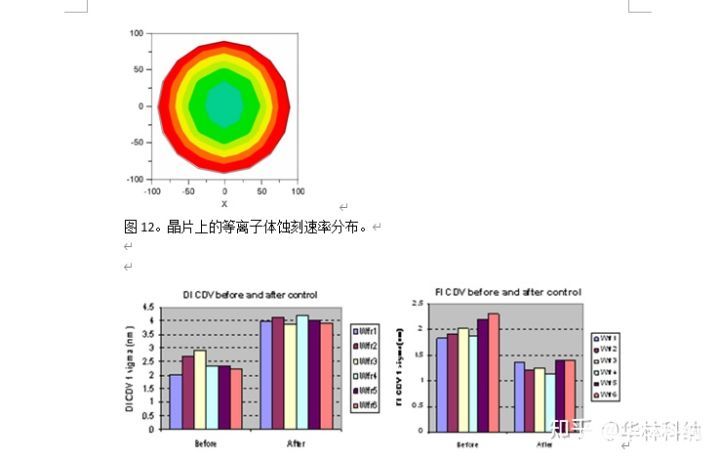

等离子体蚀刻偏置模型

由于等离子体室设计、气流、气压和其他设备设计问题,等离子体蚀刻工艺通常会引起一定的等离子体蚀刻偏置信号。此外,等离子体蚀刻偏置信号通常是稳定和系统的。这里,等离子体蚀刻偏置特征被定义为测量的跨晶片FI CD(蚀刻后CD)和DI CD(显影后CD)之间的差异,其被表示为等离子体蚀刻偏置信号与蚀刻室的晶片蚀刻速率曲线密切相关。图12示出了我们在我们的工业伙伴的制造厂中使用的蚀刻室的晶片上测量的等离子体蚀刻速率曲线。

结论和讨论

我们华林科纳采用先进的建模和控制技术,通过有意调整整个晶片的PEB温度分布来补偿晶片的变化源,从而提高整个晶片的晶片均匀度。实验构建了多区PEB热板设备模型通过设计的实验,并结合光刻和蚀刻工艺的工艺模型,可以预测最佳的PEB热板偏移设置,以最小化FI CD变化。实验实现了40%的FI CD变化减少,这验证了所提出的方法的有效性。如果集成计量可用,则有望实现额外的FI CD均匀性改善缩短基线表征和PEB热板设置调整之间的时间延迟。

审核编辑:符乾江

-

半导体

+关注

关注

339文章

31279浏览量

266705 -

光学

+关注

关注

4文章

890浏览量

38263

发布评论请先 登录

新型HERB技术如何重塑芯片蚀刻工艺

通过光刻和蚀刻工艺顺序提高整个晶圆的关键尺寸均匀性(3)

通过光刻和蚀刻工艺顺序提高整个晶圆的关键尺寸均匀性(3)

评论