定义

ECC校验是一种内存纠错原理,它是比较先进的内存错误检查和更正的手段。ECC内存即纠错内存,简单的说,其具有发现错误,纠正错误的功能,一般多应用在高档台式电脑/服务器及图形工作站上,这将使整个电脑系统在工作时更趋于安全稳定。

技术原理

内存是一种电子器件,在其工作过程中难免会出现错误,而对于稳定性要求高的用户来说,内存错误可能会引起致命性的问题。内存错误根据其原因还可分为硬错误和软错误。硬件错误是由于硬件的损害或缺陷造成的,因此数据总是不正确,此类错误是无法纠正的;软错误是随机出现的,例如在内存附近突然出现电子干扰等因素都可能造成内存软错误的发生。

为了能检测和纠正内存软错误,在ECC技术出现之前,首先出现的是内存“奇偶校验(Parity)”。内存中最小的单位是比特,也称为“位(bit)”,位有只有两种状态分别以1和0来标示,每8个连续的比特叫做一个字节(byte)。不带奇偶校验的内存每个字节只有8位,如果其某一位存储了错误的值,就会导致其存储的相应数据发生变化,进而导致应用程序发生错误。而奇偶校验就是在每一字节(8位)之外又增加了一位作为错误检测位。在某字节中存储数据之后,在其8个位上存储的数据是固定的,因为位只能有两种状态1或0,假设存储的数据用位标示为1、1、1、0、0、1、0、1,那么把每个位相加(1+1+1+0+0+1+0+1=5),结果是奇数。对于偶校验,校验位就定义为1,反之则为0;对于奇校验,则相反。当CPU读取存储的数据时,它会再次把前8位中存储的数据相加,计算结果是否与校验位相一致。从而一定程度上能检测出内存错误,奇偶校验只能检测出错误而无法对其进行修正,同时虽然双位同时发生错误的概率相当低,奇偶校验却无法检测出双位错误。

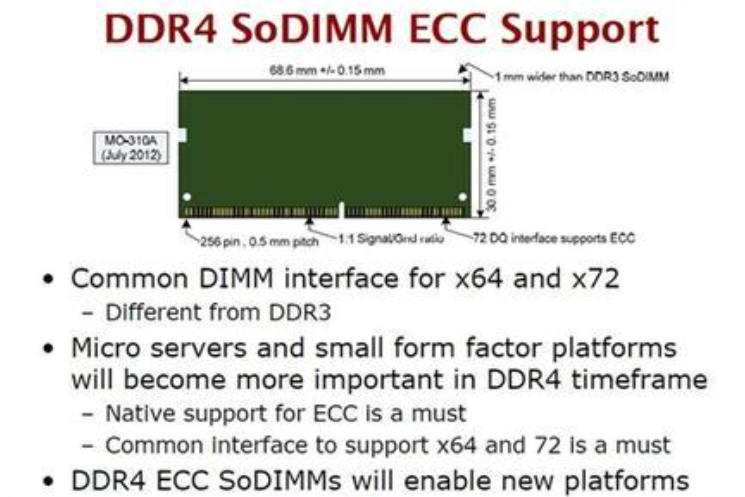

通过上面的分析我们知道Parity内存是通过在原来数据位的基础上增加一个数据位来检查当前8位数据的正确性,但随着数据位的增加Parity用来检验的数据位也成倍增加,就是说当数据位为16位时它需要增加2位用于检查,当数据位为32位时则需增加4位,依此类推。特别是当数据量非常大时,数据出错的几率也就越大,对于只能纠正简单错误的奇偶检验的方法就显得力不从心了,正是基于这样一种情况,一种新的内存技术应允而生了,这就是ECC(错误检查和纠正),这种技术也是在原来的数据位上外加校验位来实现的。不同的是两者增加的方法不一样,这也就导致了两者的主要功能不太一样。它与Parity不同的是如果数据位是8位,则需要增加5位来进行ECC错误检查和纠正,数据位每增加一倍,ECC只增加一位检验位,也就是说当数据位为16位时ECC位为6位,32位时ECC位为7位,数据位为64位时ECC位为8位,依此类推,数据位每增加一倍,ECC位只增加一位。总之,在内存中ECC能够容许错误,并可以将错误更正,使系统得以持续正常的操作,不致因错误而中断,且ECC具有自动更正的能力,可以将Parity无法检查出来的错误位查出并将错误修正。

示例

ECC(Error Checking and Correcting,错误检查和纠正)内存,它同样也是在数据位上额外的位存储一个用数据加密的代码。当数据被写入内存,相应的ECC代码与此同时也被保存下来。当重新读回刚才存储的数据时,保存下来不ECC代码就会和读数据时产生的ECC代码做比较。如果两个代码不相同,他们则会被解码,以确定数据中的哪一位是不正确的。然后这一错误位会被抛弃,内存控制器则会释放出正确的数据。被纠正的数据很少会被放回内存。假如相同的错误数据再次被读出,则纠正过程再次被执行。重写数据会增加处理过程的开销,这样则会导致系统性能的明显降低。如果是随机事件而非内存的缺点产生的错误,则这一内存地址的错误数据会被再次写入的其他数据所取代。

审核编辑:符乾江

-

嵌入式

+关注

关注

5209文章

20657浏览量

337070 -

ECC

+关注

关注

0文章

104浏览量

21761

发布评论请先 登录

32GB (x72, ECC, DR) 288 - Pin DDR4 RDIMM:技术剖析与设计考量

S32K314导入ECC公钥ImportEccKeyReq函数返回错误0x055A5A399怎么解决?

一文解读CRC校验

这是谁家部将,都做到内置ECC了!

芯片失效分析篇 —— 浅谈MICRON Memory ECC 功能

示波器如何校验探头补偿?

CS校验原理与应用

CRC校验的原理和应用

CRC校验的本质和物理意义

进行数据校验时如何保证场景覆盖的全面性?

怎样选择适合的数据校验系统时间同步硬件?

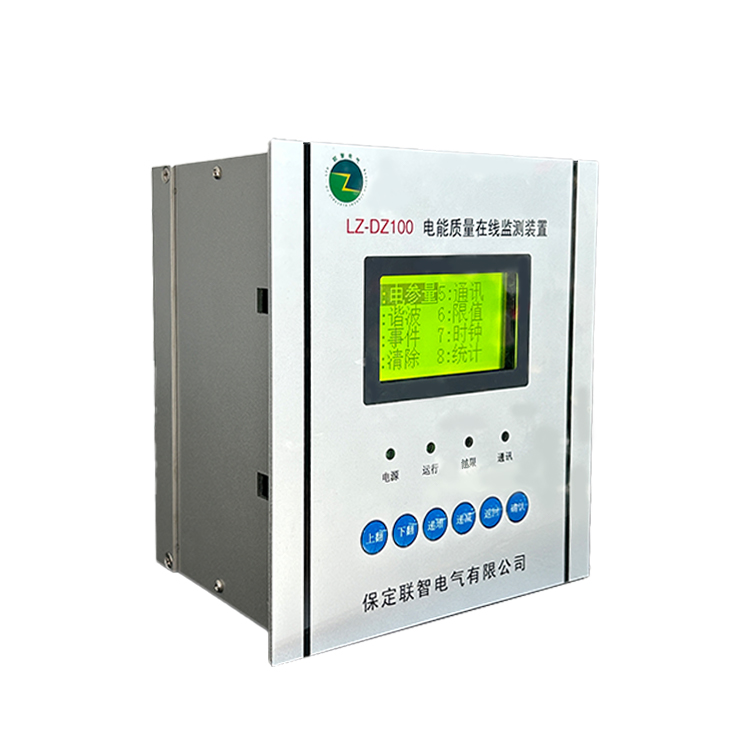

如何确保电能质量在线监测装置的数据校验的准确性?

搞定英伟达 H100 ECC 报错:从原理到维修,一步到位解烦忧

ECC校验的详细讲解

ECC校验的详细讲解

评论