PCI-SIG 工作组打算发布每代信号速率翻倍的 PCI Express (PCIe) 版本。从 Gen1 开始,2.5 GT/s 的信令速率在 Gen2 中翻倍至 5 GT/s,原计划在 Gen3 中翻倍至 10 GT/s。PCIe Gen1 和 Gen2 协议中的编码需要 20% 的开销,因此有效数据链路速率分别为 2 GT/s 和 4 GT/s。

该小组为 Gen3 确定了两个选择:将信令速率提高到 10 GT/s,保持协议的 20% 开销不变,或者指定 8 GT/s 的较低信令速率和较低的编码开销。在对扩展 PCIe 互连带宽的技术可行性进行了六个月的分析后,该小组确定可以采用主流硅工艺技术制造 8 GT/s。他们还确定 PCIe 可以与现有的低成本材料和基础设施一起部署,同时保持与 PCIe 堆栈的完全兼容性。

通过将编码要求从 8b/10b 提高到 128b/130b,新协议将编码开销降低到 1-2%。因此,PCIe Gen3 提供了 7.99 GT/s 的有效链接速率,从而使 PCIe Gen2 的有效链接速率翻了一番。编码方案的改变还包括如下的加扰/解扰算法:x23 + x21 + x16 + x8 + x5 + x2 + 1。

PHY 实施挑战:发送、接收

抖动会阻碍大多数通信链路的完整性。这在高数据速率通信的情况下更为明显。为了有效应对这些挑战,工程师需要最大限度地减少产生的抖动并最大限度地提高抖动容限。在传输过程中,锁相环形式的时钟生成需要产生尽可能少的噪声和抖动。

为此,一些设计人员实施了环形振荡器,而其他设计人员则选择了电感电容 (LC) 振荡器。环形振荡器会产生更多抖动,但在 5 GT/s PCIe Gen2 PHY 中仍然可以管理。然而,对于 8 GT/s 的 Gen3,LC 振荡器的较低抖动,特别是降低随机抖动,有助于将误码率降低到优于所需的 10 -12。

PCIe Gen3 还集成了可选的扩频时钟生成 (SSCG),以降低电磁干扰 (EMI) 的频谱密度。如果没有 SSCG,PCIe Gen3 将在时钟频率及其谐波上分布的许多窄带上辐射 EMI。这导致频谱在某些频率下可能超过 FCC 和其他监管限制(日本的 JEITA 和欧洲的 IEC)的 EMI。出于这个原因,一些制造商使用 SSCG 在消费产品中实施 PCIe Gen3 并且仍然满足 EMI 监管要求。

PCIe Gen3 的最大损耗通道需要传输去加重和接收均衡。随着数据速率增加到 8 GT/s,板载数据损失增加,因为传输线充当低通滤波器并衰减更高频率的传输。结果:数据看起来已损坏。Gen3 建议对发射机进行去加重以提升高端频率并去加重低频。在 Gen3 中,去加重已增加到 7.5 dB,最小上升时间为 19 ps,而 Gen2 规范为 6.5 dB,最小上升时间为 30 ps。建议为 PCIe Gen3 发送器使用三抽头前馈均衡器。

在接收端,传输需要从尽可能多的抖动和噪声中恢复。不同的 PHY 实现使用不同的均衡方案。一些使用连续时间线性均衡 (CTLE),已证明足以满足 5 GT/s 传输。但是,除了 CTLE,8 GT/s 传输还需要接收端的另一个阶段,即决策反馈均衡 (DFE)。当适当平衡时,与完全依赖 DFE 相比,这两种方案可以最大限度地降低功耗。这种平衡的两级方法以尽可能低的功耗实现开放式眼图。

具有较少抽头数的 DFE 实施可降低功耗。通过使用必要的通道模型和平衡的 CTLE-DFE 进行广泛的系统分析,设计人员可以优化 DFE 中使用的抽头数量。MoSys 的 PHY 实施已经在 10 GT/s SERDES 芯片中验证了该架构。

控制器-PHY 互操作

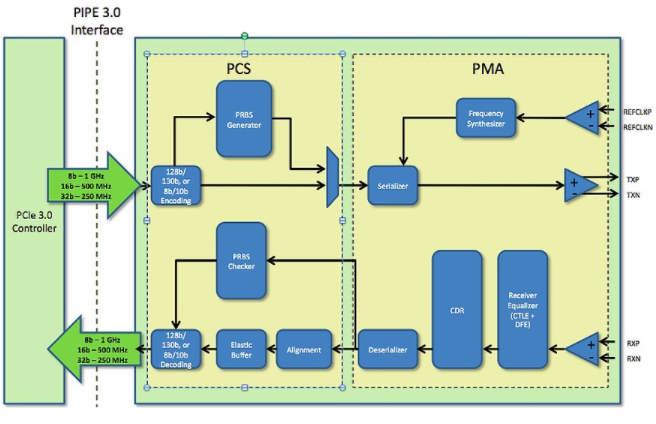

集成 PCIe Gen3 链路的片上系统 (SoC) 设计必须同时处理控制器(也称为 MAC 或链路层)和 PHY,如图 1 所示。控制器与 SoC 的其余部分接口一方面通过片上总线,另一方面通过 PHY。PHY 接口由 PHY Interface for PCI Express (PIPE) 规范明确定义。因此,作为起点,控制器和 PHY 都必须遵守 PIPE 规范,以保持合规性并确保互操作性。

图 1:为确保互操作性,控制器和 PHY 必须与符合 PIPE 规范的 SoC 设计接口。

其他关键点

PCIe Gen3 需要几个其他相关实现,包括 3 dB、12 dB 和 20 dB 的三个不同的分线通道;800 mV 至 1,200 mV 的差分输出电压,具有 400 mV 的低功率选项;和交流耦合和标称 100 欧姆差分终端。直流和奈奎斯特频率下的差分回波损耗分别为 10 dB 和 15 dB。

MoSys 的 PCIe Gen3 IP 块实现满足当前在 v0.71 中发布的所有要求,并提供 GDSII 文件中的物理介质附件 (PMA) 解决方案和作为可综合 Verilog 寄存器传输级别的物理编码子层 (PCS)。

IP 准备就绪

借助128b/130b 编码方案和加扰多项式,PCIe Gen3 提出了许多传输和接收问题,所有这些问题都在最新规范中得到解决。MoSys 在当前可用的电气兼容 IP 块中集成了 PCIe Gen3 功能,使 SoC 设计团队能够继续设计过程并在新产品中利用更高的 8 GT/s 速度。根据规范,这些模块向后兼容早期规范的 2.5 GT/s 和 5 GT/s 速度。

作者:Ali Burney,Prasad Saggurti

审核编辑:郭婷

-

控制器

+关注

关注

114文章

17886浏览量

195318 -

寄存器

+关注

关注

31文章

5620浏览量

130457 -

PCIe

+关注

关注

16文章

1483浏览量

88979

发布评论请先 登录

9FGV0441:PCIe Gen 1 - 4应用的低功耗时钟发生器

9FGL699:PCIe Gen2 6输出低功耗差分合成器深度解析

PCIe 接口-4路光纤处理卡-青翼科技高性能FPGA板卡

9FGV0441:PCIe Gen 1 - 4 应用的低功耗时钟发生器

【PCIE732】光纤卡,具备PCIe接口的万兆光纤卡

深入剖析DS80PCI102:PCIe链路扩展的得力助手

Amphenol ICC的PCIe® M.2 Gen 5卡边缘连接器:高性能连接新选择

Amphenol HD Express®:满足PCIe® Gen 6需求的高性能互连系统

Amphenol Cool Express Link™ EDSFF E3 2C PCIe® Gen 5/6 电缆连接器:高性能存储连接的新选择

Amphenol PCIe® Gen 6 Mini Cool Edge IO连接器:下一代高速互连解决方案

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

镓未来 Gen3 平台重磅发布|六大核心突破,助力功率半导体产业再度升级!

PCIe Gen 5 CEM连接器技术解析与选型指南

今日看点:我国科学家研制出高精度可扩展模拟矩阵计算芯片;Microchip 推出首款 3nm PCIe Gen 6 交换芯片

陆芯科技推出IGBT单管AU40N120T3A5

克服向PCIe Gen3迁移的SoC设计挑战

克服向PCIe Gen3迁移的SoC设计挑战

评论