PS配置启动过程

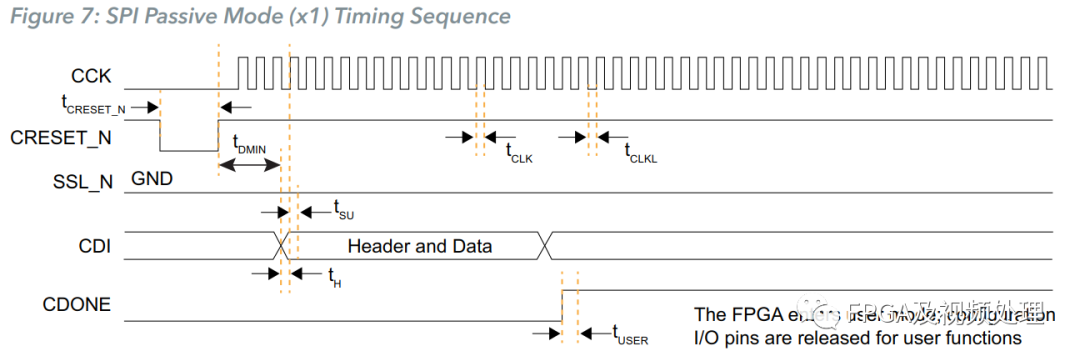

这里以X1模式为例,PS的配置过程如下:

(1)在启动配置之前要先把CRESET_N拉低tCRESET_N,然后拉高;

(2)在CRESET_N拉高之后,要等待tDMIN,才可以发送同步码,这期间可以翻转CCK;

(3)发送同步码,数据与时钟为上升沿触发;要求外部处理器连续发送数据直到数据完成;

(4)数据发送完成后,继续发送CCK时钟100周期,或者一边发送一边检测CDONE,直到CDONE为高。实际上也确实有客户因为没有拉时钟而启动不了的情况。

控制信号处理

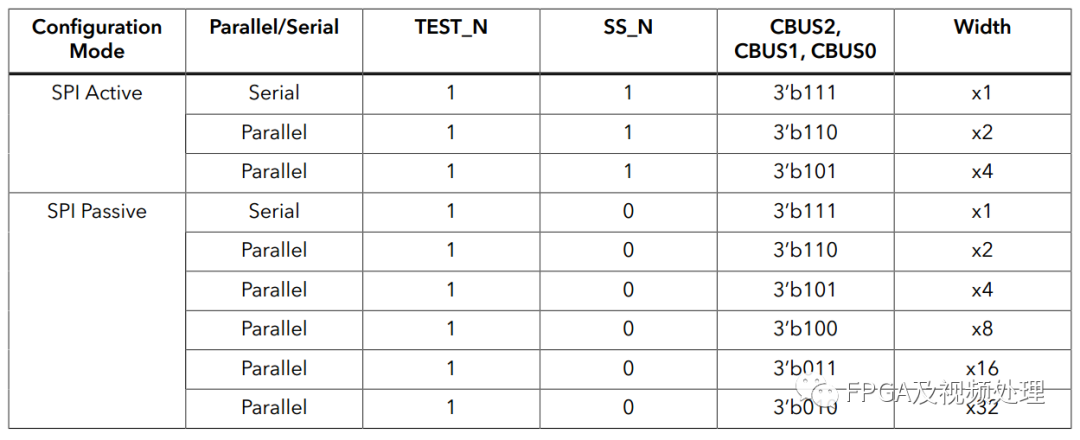

易灵思Trion FPGA的配置模块主要由CBUS[2:0]、SS_N和TEST_N,CSI几个信号控制。FPGA进入用户模式前不要对这几个信号进行翻转。

目前易灵思的Programmer工具只支持PS x1模式,x2及更高位宽需要通过外部微处理器,如MCU来操作。

这里需要注意的是在配置过程中,控制信号不要进行翻转,目前看到的现象是在多次配置过程中,在连续两次配置过程中,由于CSI翻转造成第二次配置失败。

应用案例

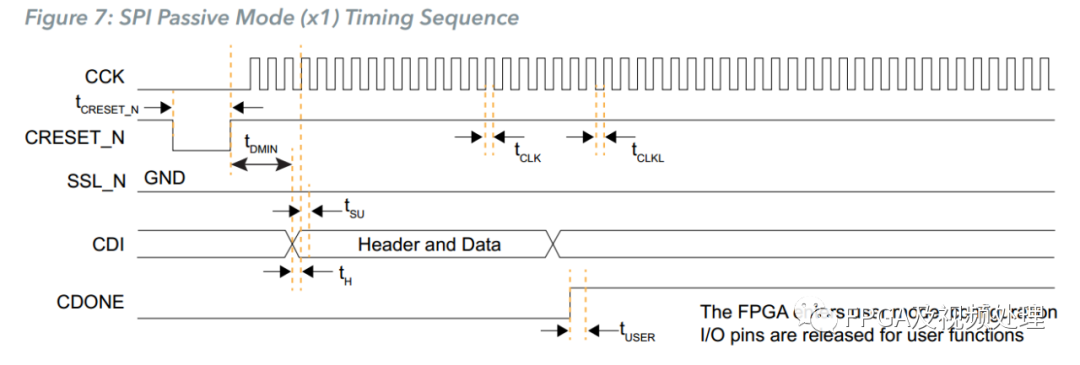

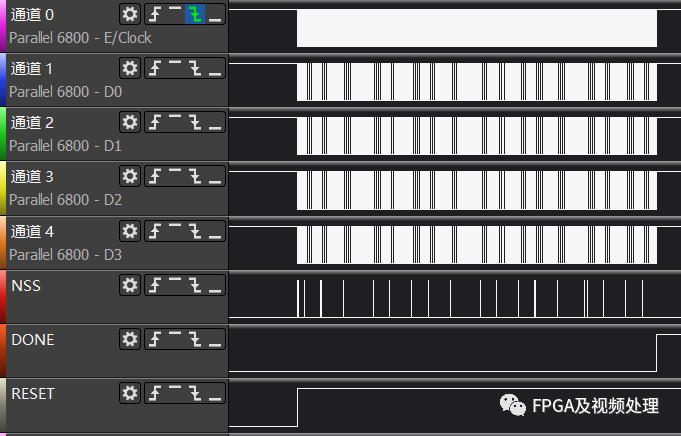

目前T20F169测试PS x4模式。时钟为30MHz,tCRESET_N拉低790ns,tDMIN为2us,数据配置完成后又继续发送时钟100个以上。可以启动。用时104ms

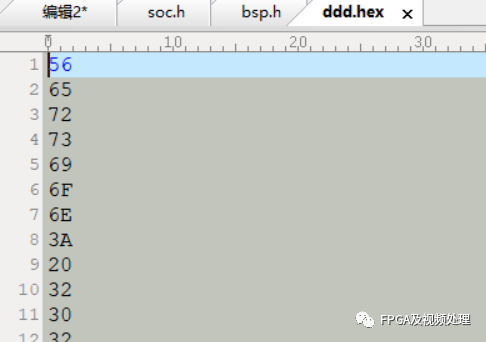

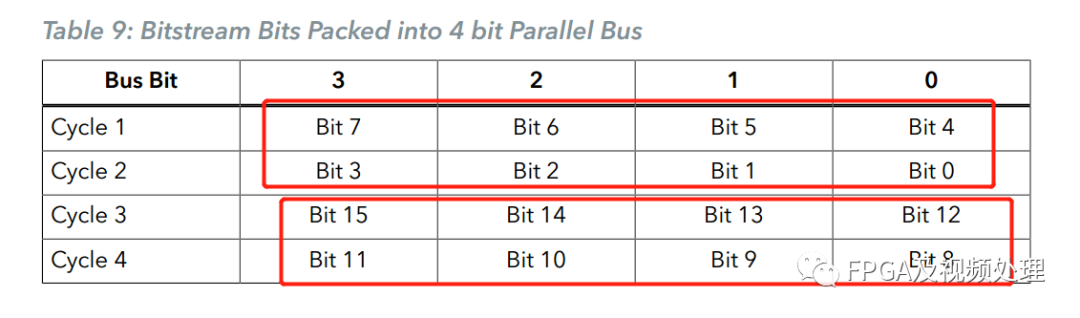

另外要提下数据顺序问题,实际在发送过程是依次发送的。

整体配置过程波形如下,SS_N有时会有很多毛刺,时钟之间也会有一些持续拉高的时间,但都不影响。

审核编辑 :李倩

-

FPGA

+关注

关注

1663文章

22491浏览量

638935 -

控制信号

+关注

关注

0文章

200浏览量

12727 -

易灵思

+关注

关注

6文章

66浏览量

5577

原文标题:易灵思Trion FPGA PS配置模式--update(2)

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

赛灵思FPGA电源解决方案全解析

基于易灵思eMMC IP的Linux系统加载方案

易灵思助力2025年全国大学生嵌入式芯片与系统设计竞赛圆满落幕

易灵思Sapphire SoC中RISC-V平台级中断控制器深度解析

易灵思助力上海集成电路紧缺人才培训项目顺利结课

易灵思2025 FPGA技术研讨会成都站圆满收官

易灵思与思特威第二届机器视觉方案大会圆满收官

易灵思与南京大学集成电路学院暑期课程圆满结课

易灵思 FPGA TJ375的PLL的动态配置

易灵思Trion FPGA PS配置模式--update

易灵思Trion FPGA PS配置模式--update

评论