为 ADC 生成采样时钟是对干净(低抖动)时钟生成要求最苛刻的应用之一。使用嘈杂的时钟会直接影响数据转换器准确转换其接收信号的能力。信噪比 (SNR) 是模数转换器的一项重要规格,用于量化 ADC 工作的准确程度。以下是将 SNR 与抖动联系起来的公式:

信噪比 = -20*log(2π*F IN *t J ); 其中 t J是 RMS 时间抖动,F IN是模拟带宽。t J (RMS) 是通过在编码带宽上对相位噪声进行积分而获得的。

我不会重新讨论公式的推导,因为它可以在网络上的其他地方找到。

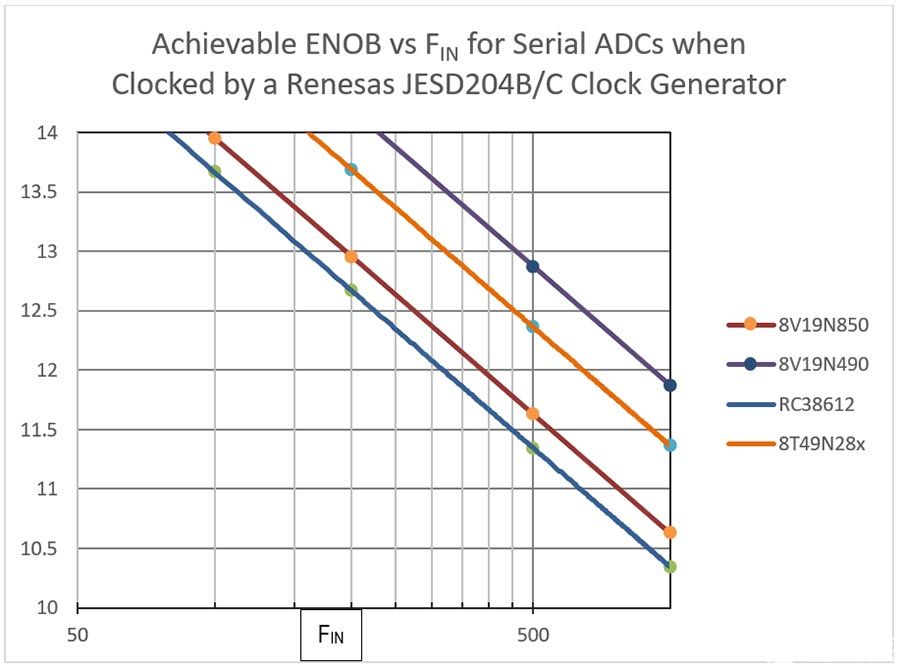

瑞萨的计时产品组合是业内最大的。为了帮助您找到最适合您需求的部分,瑞萨电子提供了以下图表。以下是如何使用图表来确定满足您需求的正确部分:在 XY 网格上找到与您的用例相对应的点,然后向右移动和/或向上移动到图表上的下一个实线对角线。您遇到的第一条实线表示瑞萨推荐您首先考虑的设备。为并行和串行输出 ADC 提供了单独的图表。现代串行输出 ADC 通常需要具有 JESD204x 同步功能,因此对于该图表,仅填充了支持 JESD204B/C 的时钟器件(图 1)。

要探索此处推荐的设备的替代方案,请使用先前提供的公式 [t J = (10^(SNR/-20))/ (2π*F IN ),但求解 t J ] 来确定您需要的抖动性能。将t J (作为最大抖动)插入到我们的时钟发生器产品组合或JESD204B/C 时钟抖动衰减器产品组合的参数搜索表中。

图 1. 当由 Renesas JESD204B/C 时钟发生器提供时钟时,串行 ADC 的 ENOB 与 FIN

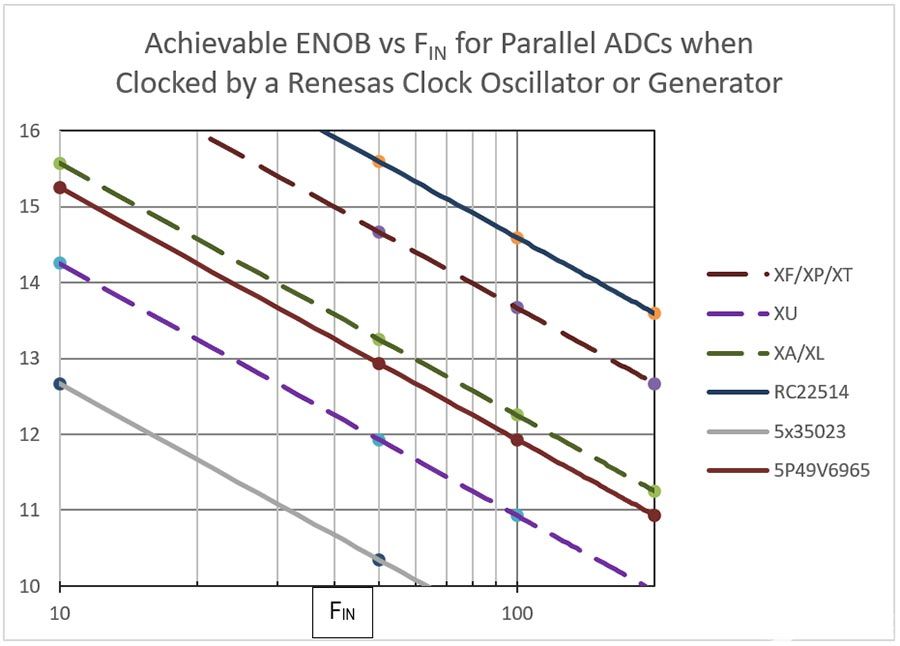

如果您的系统中只有一个转换器需要时钟,您最好从下表(图 2)中选择一个振荡器(见虚线),但如果您需要多个时钟用于附加转换器(或其他组件) ),选择时钟发生器(实线)可能会为您提供更好的服务。

图 2. 当由 Renesas JESD204B/C 时钟发生器或振荡器提供时钟时,并行 ADC 的 ENOB 与 FIN

审核编辑:郭婷

-

振荡器

+关注

关注

28文章

4156浏览量

142333 -

adc

+关注

关注

100文章

7450浏览量

553836 -

Renesas

+关注

关注

0文章

1769浏览量

24308

发布评论请先 登录

LMR544xx系列电源转换器:工业应用的理想选择

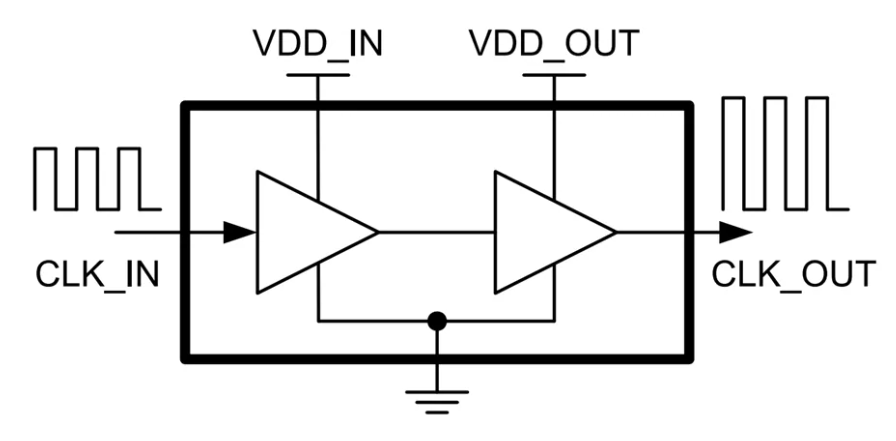

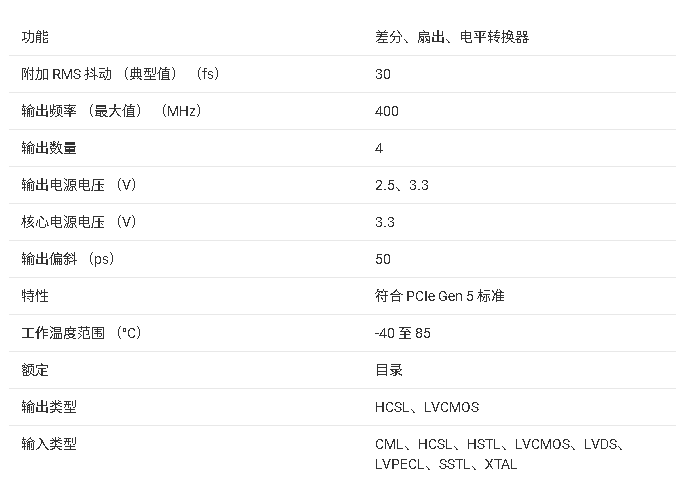

Texas Instruments CDCBT1001时钟缓冲器与电平转换器技术解析

LMK00334四输出时钟缓冲器与电平转换器技术文档总结

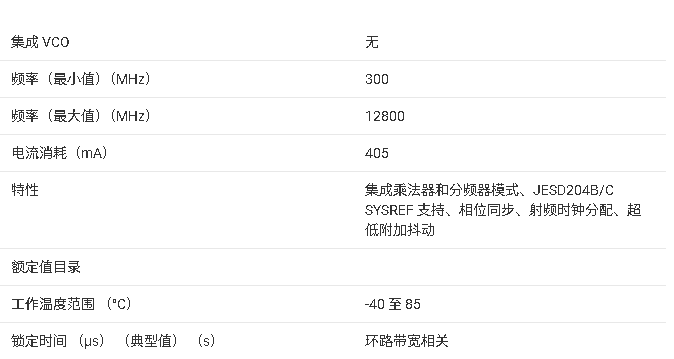

LMX1204 低噪声高频 JESD 缓冲器/乘法器/分频器技术文档总结

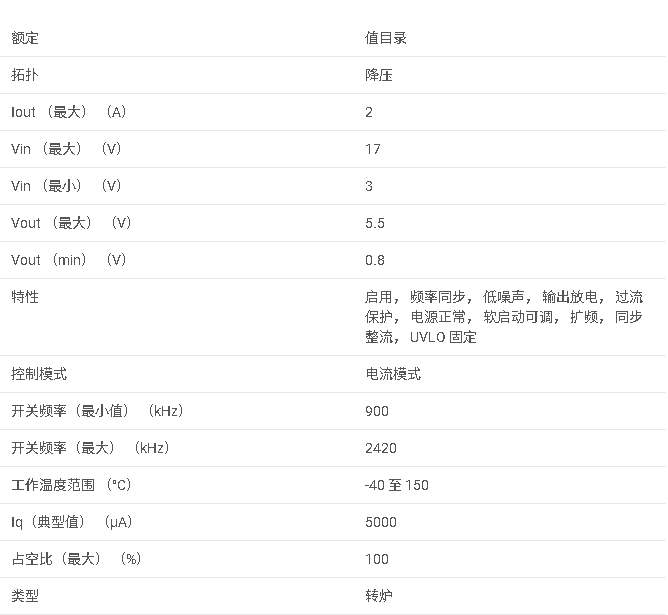

TPS62912 具有集成铁氧体磁珠滤波器补偿的 17VIN、2A 低噪声和低纹波降压转换器数据手册

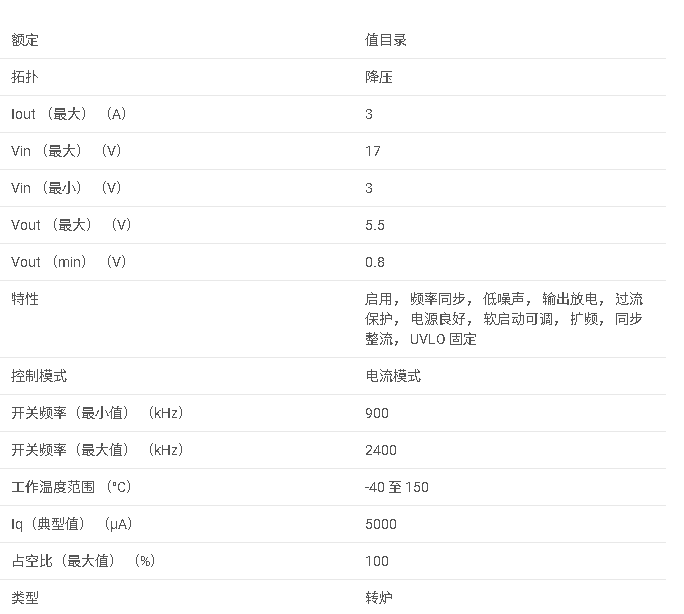

TPS62913 具有集成铁氧体磁珠滤波器补偿的 17VIN、3A 低噪声和低纹波降压转换器数据手册

AD、DA转换器接口技术与实用线路

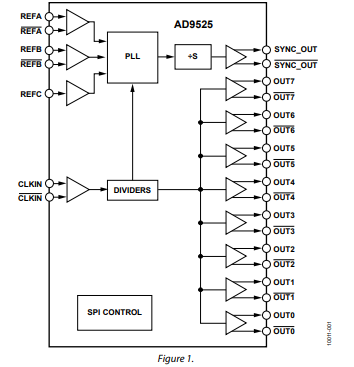

AD9525旨在满足长期演进(LTE)和多载波GSM基站设计的转换器时钟技术手册

为转换器时钟应用选择最佳器件

为转换器时钟应用选择最佳器件

评论