LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器

在电子设计领域,时钟信号的精确分配和转换至关重要。今天要给大家介绍的是德州仪器(TI)的 LMK00804B-Q1,一款高性能的时钟扇出缓冲器和电平转换器,它在多个方面展现出了出色的性能。

文件下载:lmk00804b-q1.pdf

1. 产品特性亮点

1.1 高可靠性与宽温范围

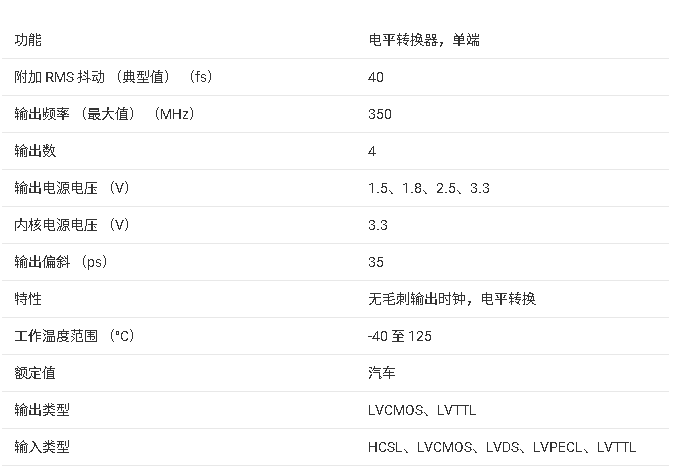

LMK00804B-Q1 通过了 AEC-Q100 认证,器件温度等级为 1,工作温度范围在 -40°C 至 +125°C (T_{A}) ,这使得它能够在严苛的汽车环境中稳定工作。

1.2 多电压输出支持

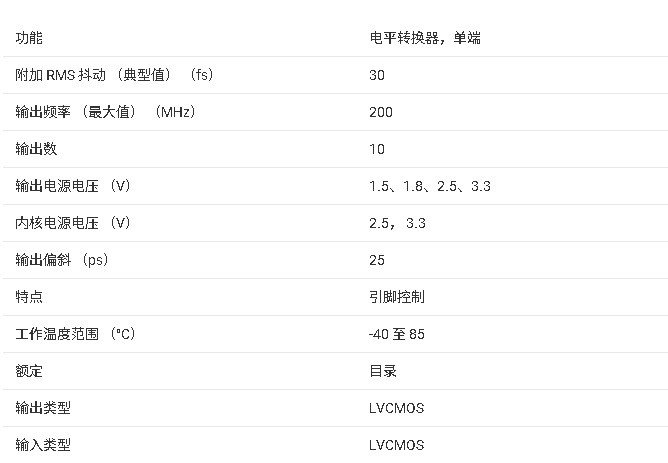

具备四个 LVCMOS/LVTTL 输出,支持 1.5 - 3.3V 的电压电平。其在 40MHz 时典型的附加抖动仅为 0.1ps RMS,噪声底为 -168dBc/Hz,最大输出频率可达 350MHz,输出偏斜最大为 35ps,器件间偏斜最大为 550ps。这样的性能表现,为高精度的时钟分配提供了有力保障。

1.3 双可选输入

提供两个可选输入,CLK_P、CLK_N 对可接受 LVPECL、LVDS、HCSL、SSTL、LVHSTL 或 LVCMOS/LVTTL 信号;LVCMOS_CLK 则接受 LVCMOS/LVTTL 信号,增强了输入信号的兼容性。

1.4 同步时钟使能

拥有同步时钟使能功能,内部同步时钟使能输入,可消除时钟使能端断言或去断言时输出端的短脉冲或毛刺脉冲。当禁用时钟时,输出保持逻辑低电平状态。

1.5 多种电源配置

核心/输出电源有多种配置可选,如 3.3V/3.3V、3.3V/2.5V、3.3V/1.8V、3.3V/1.5V,满足不同的电源需求。

1.6 小巧封装

采用 16 引脚 VQFN 封装,节省了 PCB 空间。

2. 应用场景广泛

LMK00804B-Q1 在高级驾驶辅助系统(ADAS)中有着重要的应用,包括前向远程雷达、中/短程雷达以及超短程雷达。在这些应用中,它能够将低抖动时钟分配到四个收发器,提高级联毫米波雷达系统的整体目标检测和分辨率。

3. 详细规格解读

3.1 绝对最大额定值

在使用过程中,要注意器件的绝对最大额定值,如电源输入电压 (V{DD}) 、电源输出电压 (V{DDO}) 、输入电压 (V_{I}) 等,超出这些范围可能会对器件造成永久性损坏。

3.2 ESD 评级

人体模型(HBM)的 ESD 等级为 2,静电放电电压为 ±2000V;带电设备模型(CDM)的 ESD 等级为 C5,静电放电电压为 ±750V。在操作过程中,要采取适当的防静电措施,防止 ESD 对器件造成损害。

3.3 推荐工作条件

推荐的电源输入电压 (V{DD}) 为 3.135 - 3.465V,电源输出电压 (V{DDO}) 有多种范围可选,环境温度 (T{A}) 在 -40°C 至 125°C 之间,最大输出频率 (f{OUT}) 为 350MHz。

3.4 热信息

了解器件的热性能参数,如结到环境的热阻 (R{theta JA}) 、结到外壳(顶部)的热阻 (R{theta JC(top)}) 等,有助于进行合理的散热设计,保证器件在正常温度范围内工作。

3.5 电源特性

在推荐的工作电源和温度范围内,通过 (V{DD}) 的电源电流 (I{DD}) 典型值为 21mA,通过 (V{DDO}) 的电源电流 (I{DDO}) 典型值为 5mA。

3.6 电气特性

包括 LVCMOS/LVTTL 直流电气特性和差分输入直流电气特性,这些特性规定了输入输出电压、电流等参数的范围,是进行电路设计的重要依据。

3.7 开关特性

如传播延迟、输出偏斜、上升/下降时间、附加抖动、相位噪声底等,这些特性影响着时钟信号的质量和传输性能。

4. 设计与应用建议

4.1 电源供应

虽然没有严格的电源供应排序要求,但通常建议先对电源输入电压 (V) 进行排序,再对电源输出电压 (V_{DDO}) 进行排序。同时,要注意电源滤波,使用旁路电容器消除电源中的低频噪声,插入铁氧体磁珠隔离高频开关噪声。

4.2 布局设计

- 接地平面:使用实心接地平面,为器件和旁路电容器、时钟源和目标设备之间提供低阻抗返回路径。通过五个过孔将芯片的裸片附着焊盘(DAP)连接到实心 GND 平面,避免其他系统电路的返回路径穿过器件的局部接地,以减少噪声耦合。

- 电源引脚:遵循电源供应原理图和布局示例进行设计。

- 输入输出端接:将输入端接或偏置电阻尽可能靠近 CLK_P/CLK_N 引脚和 LVCMOS_CLK 引脚放置,在 50Ω 输入输出迹线中避免或最小化过孔,以减少阻抗不连续性。在时钟输出 Q[3:0] 处使用 43Ω 串联电阻匹配驱动器阻抗和迹线阻抗。

4.3 未使用引脚处理

对于未使用的输入和输出引脚,要根据其内部连接和特性进行正确处理。例如,CLK_EN 必须在提供有效参考时钟之前保持低电平;CLK_P/CLK_N 输入在使用单端输入时要注意内部上拉和下拉电阻的影响;LVCMOS_CLK 输入内部下拉电阻确保其在悬空时为低电平;未使用的输出可以悬空。

4.4 输入信号要求

为了充分发挥 LMK00804B-Q1 的优势,输入信号的摆率最好达到 3V/ns 或更高。差分信号输入通常比单端信号更优,因为它能提供更高的摆率和共模抑制能力。

5. 总结

LMK00804B-Q1 凭借其丰富的特性、广泛的应用场景和良好的性能表现,成为了时钟分配和电平转换领域的一款优秀产品。在实际设计过程中,我们需要充分了解其规格参数和设计建议,结合具体的应用需求,进行合理的电路设计和布局,以确保系统的稳定性和可靠性。大家在使用过程中遇到过哪些问题呢?欢迎在评论区分享交流。

-

电平转换器

+关注

关注

1文章

268浏览量

21188

发布评论请先 登录

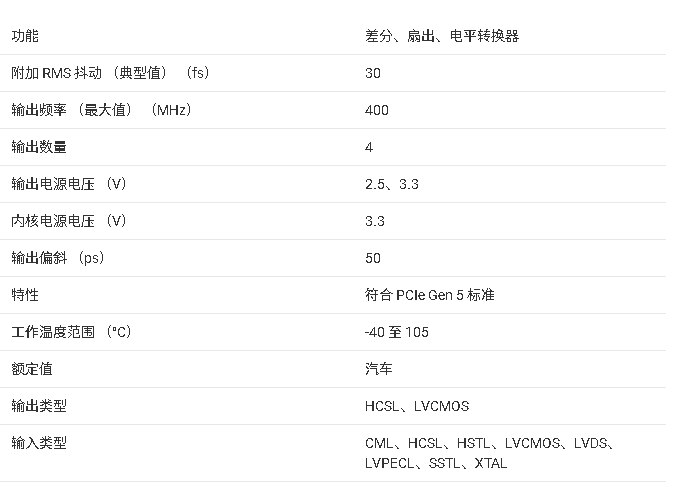

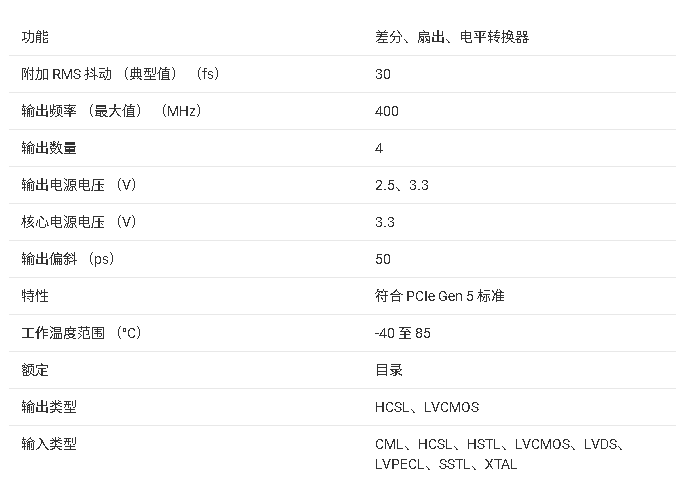

LMK00334-Q1四路输出PCIe第1代至第5代时钟缓冲器和电平转换器数据表

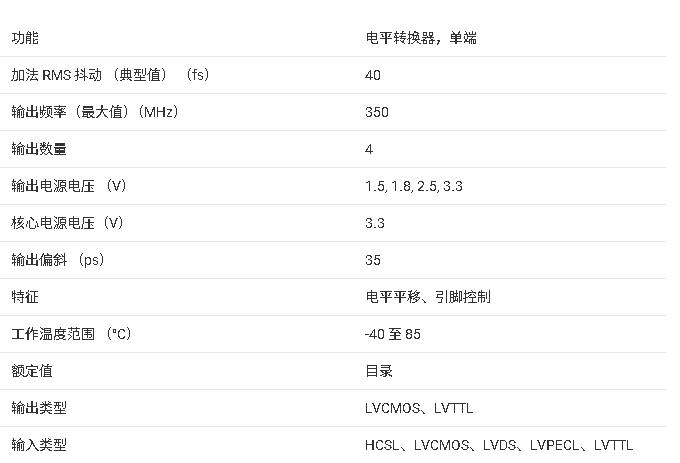

LMK00804B-Q1 1.5V至3.3V、1路至4路高性能LVCMOS扇出缓冲器和电平转换器数据表

具有通用输入的LMK00101超低抖动LVCMOS扇出缓冲器/电平转换器数据表

LMK00804B低偏移1到4多路复用差动/LVCMOS到LVCMOS/TTL扇出缓冲器数据表

LMK00804B 低偏斜1:4多路复用差分/LVCMOS至LVCMOS/TTL扇出缓冲器技术文档总结

LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器

LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器

评论