中国,北京-2022年4月6日-智能系统连接解决方案先驱Astera Labs今日宣布,其面向PCI Express® (PCIe®) 5.0和Compute Express Link™ (CXL™) 2.0的Aries Smart Retimers现已进入量产阶段。率先上市的Aries Smart Retimer产品组合圆满完成与关键行业合作伙伴之间严苛的互操作性测试,测试涵盖各种PCIe 5.0处理器、FPGA、加速计算、GPU、网络、存储和交换机SoC,为在企业数据中心和云中的广泛部署铺平了道路。

Astera Labs首席执行官Jitendra Mohan表示:“PCIe 5.0和CXL技术是满足下一代服务器在云中运行智能工作负载的高速连接需求的关键组成部分。Aries Smart Retimers产品的发布和行业合作伙伴互操作性测试的圆满完成,将推动向具有专用机群管理性能的更高宽带互联顺利过渡。

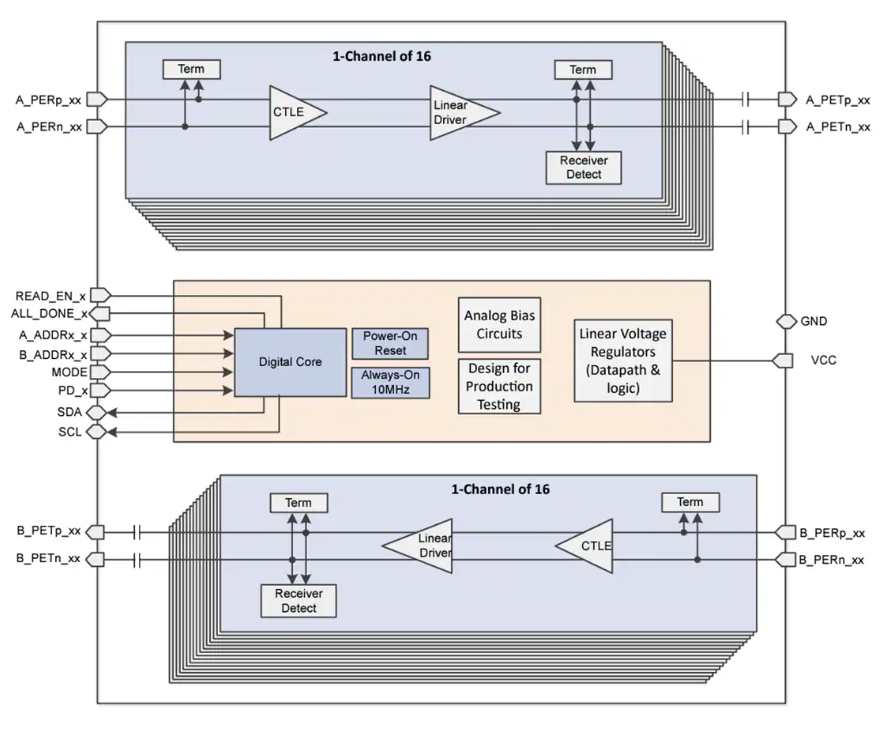

Aries PCIe 5.0和CXL 2.0 Smart Retimers克服了信号完整性的问题,可实现高达32 Gbps、低于10ns的延迟和内置机群管理,以及对大规模企业和云服务器部署至关重要的深度诊断功能。

NVIDIA硬件工程产品高级副总裁Brian Kelleher表示:“如今的工作负载优化基础架构不仅需要高带宽、低延迟的PCIe 5.0和CXL互连,还要在日益复杂的服务器拓扑中的所有元器件之间实现稳健的互操作性。与优秀的生态系统伙伴合作(例如Astera Labs),并采用其先进解决方案(例如Aries Smart Retimers),是确保大规模无缝部署我们AI平台的关键。”

Astera Labs Cloud-Scale Interop Lab提供了严苛的测试,确保在Aries Smart Retimers与PCIe/CXL的Root Complex和End Point之间建立稳健的互操作性,让客户可以放心地进行设计,并减少在整个开发阶段所花费的时间和精力。

Broadcom数据中心解决方案集团副总裁兼总经理Jas Tremblay指出:“Broadcom与Astera Labs密切合作,以实现其Aries PCIe 5.0 Smart Retimer与我们PEX89000交换芯片之间的无缝互操作性。我们的即插即用型解决方案将共同促进业界在下一代高性能服务器中,广泛采用PCIe 5.0连接,以释放人工智能、机器学习和云计算等数据密集型工作负载。”

Samsung Electronics解决方案产品与开发副总裁Soonjae Won表示:“通过采用面向企业服务器的开创性PCIe 5.0 PM1743 SSD,Samsung巩固了其在高端存储技术领域的行业领先地位。与Astera Labs及其Aries Smart Retimer的合作,使我们在逐渐形成生态系统之初,确保了出色的企业PCIe 5.0存储性能和可靠性。”

供货情况:

Aries PCIe 5.0和CXL 2.0 Smart Retimers可通过www.AsteraLabs.com/Aries购买,提供x8(PT5081L)和x16(PT5161L) PCIe 通道配置。如需了解有关PCIe 5.0和CXL 2.0连接解决方案的更多信息,请访问www.AsteraLabs.com或联系info@AsteraLabs.com。

相关资源:

·互操作简讯#4:利用Aries Smart Retimers部署稳健的PCIe 5.0连接(视频)

·利用Astera Labs的专用连接解决方案全面释放CXL的潜力(视频)

·Intel Innovation 2021:Astera Labs、Broadcom、Intel和Samsung PCI Express 5.0演示(视频)

·Aries CXL Smart Retimer演示:CXL生态系统与Intel和Synopsys的互操作(视频)

·适用于PCIe 5.0和CXL的Aries Smart Retimer(视频)

·在系统实施中无缝转换到PCIe 5.0技术(网络研讨会)

Astera Labs将于4月5日至7日在加州圣克拉拉举办的DesignCon 2022(展位#524)上展示其Aries PCIe 5.0 Smart Retimer以及其他专用连接解决方案。预约会面请联系info@AsteraLabs.com。

-

处理器

+关注

关注

68文章

20329浏览量

254866 -

交换机

+关注

关注

23文章

2930浏览量

104860 -

智能系统

+关注

关注

2文章

421浏览量

74346

发布评论请先 登录

FT 5000 Smart Transceiver:下一代智能网络芯片的卓越之选

理想汽车发布下一代自动驾驶基础模型MindVLA-o1

华为在MWC 2026正式发布下一代WAN目标网架构

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能线性转接驱动器

DS320PR410:支持PCIe™ 5.0、CXL 2.0的四通道线性转接驱动器

Amphenol Aerospace高压38999连接器:满足下一代飞机电力需求

Amphenol Multi-Trak™:下一代高速互连解决方案

Amphenol PCI Express® Gen 6 卡边缘连接器:下一代系统的高速解决方案

Amphenol PCIe® Gen 6 Mini Cool Edge IO连接器:下一代高速互连解决方案

Microchip推出下一代Switchtec Gen 6 PCIe交换芯片

适用于下一代 GGE 和 HSPA 手机的多模/多频段 PAM skyworksinc

澜起科技推出CXL® 3.1内存扩展控制器,助力下一代数据中心基础设施性能升级

DS320PR1601 PCIe 5.0 32Gbps线性转接驱动器技术解析与应用指南

Astera Labs全新发布Aries PCIe® 5.0和CXL™2.0 Smart Retimers助力解锁下一代云连接

Astera Labs全新发布Aries PCIe® 5.0和CXL™2.0 Smart Retimers助力解锁下一代云连接

评论