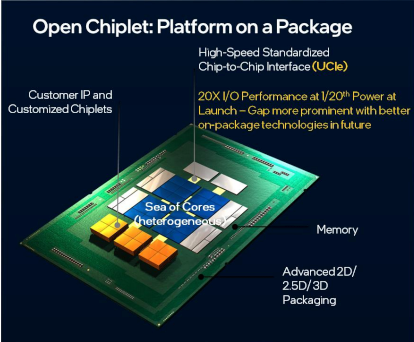

电子发烧友网报道(文/李诚)3月2日,AMD、ARM、英特尔等多家国际半导体巨头联合推出了全新的芯片互联标准UCIe 1.0。UCIe 1.0标准是针对Chiplet技术建立的,致力于推动芯片互联的标准化发展,构建出相互兼容的芯片生态系统,提升芯片与芯片之间的互操性,延续摩尔定律的发展。

图源:UCIe

在UCIe 1.0标准推出之前,众多厂商都是推行自己的互联标准,不同厂商的芯粒由于使用的标准不同,无法实现不同厂商芯粒与芯粒之间的互联。如果没有统一的标准,芯片厂商继续各行其是,将会成为不同厂商芯粒互联之间的一道屏障,限制Chiplet的发展。

什么是Chiplet

Chiplet是目前各大芯片巨头都在推行的一种先进封装技术,该技术可以将不同的工艺节点、不同功能的芯粒通过拼接的方式集成在同一芯片内,而不是与SoC一样采用片上集成的方式。

或者可以这样理解,把每一个要实现的功能想象为一个积木(积木的类型不受工艺节点与功能的制约),在将不同的积木以拼接、堆叠的方式合封起来,构成一个多功能的异构芯片。为保证不同芯片之间互联的高效性,UCIe 1.0标准明确规定了,将会采用PCIe和CXL作为高速互联的媒介。同时UCIe 1.0标准的推出也为Chiplet的发展提供了更多的可能。

摩尔定律发展了50多年,也有人唱衰了50多年,然而在遇到发展瓶颈之际都会有新的技术出现,为摩尔定律“续命”。如今最先进的半导体工艺已发展至3nm这一节点,先进的制程对于手机、平板电脑此类设备而言能够更有效地提升产品的性能并降低系统功耗,但对于台式电脑、汽车电子等大型设备而言,采用先进的工艺只会一味地增加成本,甚至可能得不到相等的商业回报。在摩尔定律放缓、工艺成本增加的背景下,通过标准化的Chiplet技术,将不同工艺节点的Die集成芯片的方式实现性能与成本的权衡,何尝不是一种明智的选择呢?

标准统一后对半导体行业有何影响?

在UCIe 1.0标准与Chiplet技术未出来之前,芯片厂商为提高芯片的整体性能,不得不花重金采用最先进的设计工艺,通过增加晶体管的数量来实现。先刨去成本不说,若想使用最先进的工艺生产芯片,那就需要有生产设备吧?大家都知道生产芯片需要用到***,其中DUV***能够生产28nm到7nm的芯片,EUV***能生产7nm以下的芯片。目前全球最先进的工艺节点也只达到了3nm,这一突破目前只有ASML的EUV***可以实现。但你要知道在全球范围内造***的可不止ASML,还有在光学领域有着不可撼动地位的佳能与尼康。

随着工艺节点的提高,更高工艺节点的***开发难度也越大,在重重困难面前,就连佳能和尼康也只能止步于DUV***,一骑绝尘的ASML成为唯一能够生产EUV***的企业。ASML的EUV***能否继续续写传奇,满足半导体产业的发展需求,一切都还是个未知数。而在UCIe 1.0标准推出之后,不会再因芯粒兼容而困扰,可以将不同厂商的芯粒通过合并封装的方式整合在一起,在相同的面积内提升芯片的晶体管个数,构建出性能更强劲的芯片。

UCIe 1.0标准的推出意味着不同产商芯粒互联标准的统一,半导体IP产业将会迎来新的革命,届时IP将会以硅片的形式体现,真正意义上的实现“即插即用”。其实,Chiplet的优势不止于此,Chiplet还能提高晶圆的良品率,传统的SoC是将所有的功能全部集中在同一晶圆之上,在芯片的光刻过程中,一旦出现任何问题,整颗晶圆都会报废。然而将原本同样大小的晶圆分为若干份,在每片小的晶圆上实现一个或多个功能,再通过Chiplet技术实现各个功能的互联互通,即使在光刻过程中出现错误,也仅仅只是某一片小晶圆的损坏,用一颗功能完整的晶圆代替即可。这一技术的引进不仅能够提高晶圆的良品率,由于每一片晶圆变小,还有利于提升晶圆原片的整体利用率。

结语

随着科技的进步,终端应用对芯片性能的需求也在水涨船高,通过采用先进的工艺节点提高芯片的整体性能是一个不错的选择,但工艺的进步也就意味着设计成本的提升。就拿5nm工艺为例,并不是所有芯片需要使用到5nm工艺,也并不是所有企业都能承担得起5nm工艺带来的设计成本,而chiplet可以针对其功能选择最为合适的制程,不仅能够形成更高效的集成电路,还能节省成本。

通过观察发现,近年来全球半导体产业对chiplet的需求呈井喷式地增长,如今UCIe 1.0标准的推出,将会打通芯粒跨厂商互联的最后一道屏障,助力半导体产业的发展。

-

amd

+关注

关注

25文章

5708浏览量

140417 -

英特尔

+关注

关注

61文章

10324浏览量

181089 -

chiplet

+关注

关注

6文章

499浏览量

13650

发布评论请先 登录

被指存散热硬伤,英特尔代工iPhone芯片几无可能?

英特尔炮轰,AMD回击!掌机市场芯片之争

超越台积电?英特尔首个18A工艺芯片迈向大规模量产

英特尔计划裁员21000人,可能跳过18A工艺

如何进一步从SPI NOR闪存启动电路板?

2026英特尔客户高峰论坛:杰和科技以深度协同收获技术跃迁

伟创力与AMD进一步深化战略合作

高通发布新款PC芯片,直面英特尔、AMD

英特尔、AMD、TI等芯片巨头遭诉讼;OpenAI 发布GPT-5.2

BlackBerry QNX与众森软件进一步深化战略合作

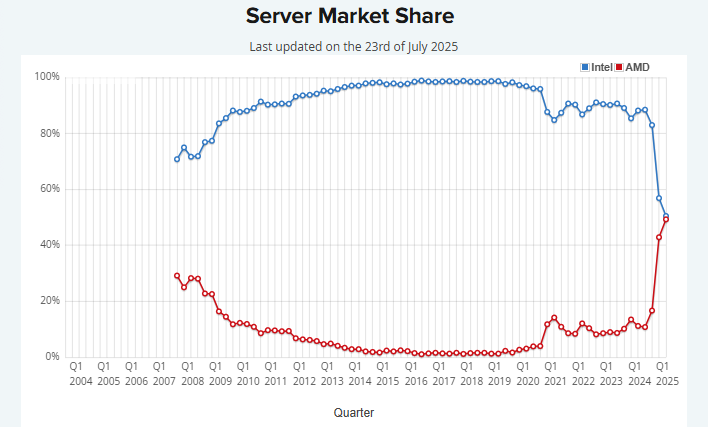

看点:AMD服务器CPU市场份额追上英特尔 华为Mate80主动散热专利曝光

软通动力与中国联通合作关系进一步深化

5G与工业互联网如何进一步融合?

直击Computex2025:英特尔重磅发布新一代GPU,图形和AI性能跃升3.4倍

Chiplet芯片互联再进一步,AMD、ARM、英特尔联手发布UCIe 1.0标准

Chiplet芯片互联再进一步,AMD、ARM、英特尔联手发布UCIe 1.0标准

评论