GTX IP配置完了,你不得搞个回环测试一番?

前言

理解一个IP的用法,最好的办法就是打开官方的Example Design。

所以本文首先介绍Example Design,然后再替换成我们自己的收发测试模块,对比印证学习,差不多就能勉强把GTX给玩起来了。

一、示例工程Example Design

接上一讲(四)GTX IP核的配置:

我们配置GTX为:3.125G , 参考时钟156.25Mhz ,然后生成了GTX的IP。

首先,右键IP打开Example Design。

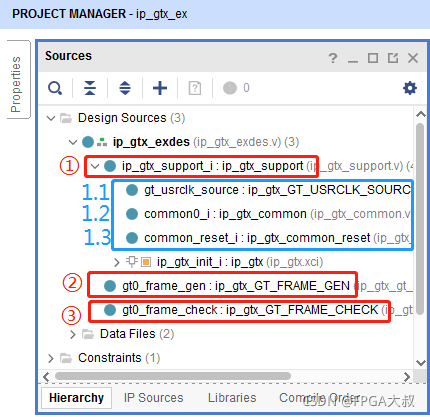

打开示例工程后,看到如下图所示的工程结构:

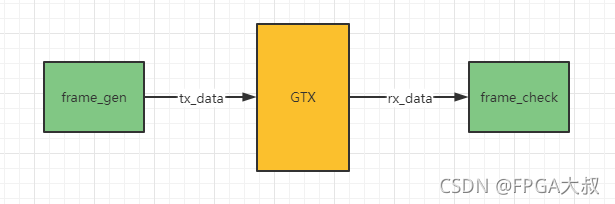

先简单概括下,示例工程的组成结构,如下图所示的拓扑图:

OK,接下来我们对每个子模块进行分别介绍。

1.1 gtx_support模块

support子模块为GTX主要模块。包含GTX的时钟、复位以及对原语/IP的例化使用。

Xilinx为了IP核的通用性,将每个IP的端口设置非常完善也意味着非常复杂。端口信号众多,导致我们一阵头大,不知从何下手,所以这里直接上干货,简要解析各个端口信号,哪些是使用的,哪些是不用的。

PS:很多端口都没有使用,要么置0,要么置1 。

所以,引用B站名言:“消除恐惧的最好办法就是面对恐惧,奥利给!”

直接上代码: 详见后面注释内容!

注:很多功能我们没有用上,所以给的0,实际使用根据具体需求而定。

ip_gtx ip_gtx_init_i

(

.sysclk_in (sysclk_in_i), //系统时钟

.soft_reset_tx_in (soft_reset_tx_in), //0

.soft_reset_rx_in (soft_reset_rx_in), //0

.dont_reset_on_data_error_in (dont_reset_on_data_error_in), //0

.gt0_tx_fsm_reset_done_out (gt0_tx_fsm_reset_done_out), //output

.gt0_rx_fsm_reset_done_out (gt0_rx_fsm_reset_done_out), //output

.gt0_data_valid_in (gt0_data_valid_in), //1

//GT0 (X1Y0)

//------------------------------- CPLL Ports -------------------------------

.gt0_cpllfbclklost_out (gt0_cpllfbclklost_out),

.gt0_cplllock_out (gt0_cplllock_out),

.gt0_cplllockdetclk_in (sysclk_in_i), //系统时钟

.gt0_cpllreset_in (gt0_cpllreset_in), //0

//------------------------ Channel - Clocking Ports ------------------------

.gt0_gtrefclk0_in (tied_to_ground_i), //0

.gt0_gtrefclk1_in (q0_clk1_refclk_i), //参考时钟

//-------------------------- Channel - DRP Ports --------------------------

.gt0_drpaddr_in (gt0_drpaddr_in), //0

.gt0_drpclk_in (sysclk_in_i), //系统时钟

.gt0_drpdi_in (gt0_drpdi_in), //0

.gt0_drpdo_out (gt0_drpdo_out), //0

.gt0_drpen_in (gt0_drpen_in), //0

.gt0_drprdy_out (gt0_drprdy_out), //0

.gt0_drpwe_in (gt0_drpwe_in), //0

//------------------------- Digital Monitor Ports --------------------------

.gt0_dmonitorout_out (gt0_dmonitorout_out), // output

//----------------------------- Loopback Ports -----------------------------

.gt0_loopback_in (gt0_loopback_in), //0

//---------------------------- Power-Down Ports ----------------------------

.gt0_rxpd_in (gt0_rxpd_in), //0

.gt0_txpd_in (gt0_txpd_in), //0

//------------------- RX Initialization and Reset Ports --------------------

.gt0_eyescanreset_in (gt0_eyescanreset_in), //0

.gt0_rxuserrdy_in (gt0_rxuserrdy_in), //1

//------------------------ RX Margin Analysis Ports ------------------------

.gt0_eyescandataerror_out (gt0_eyescandataerror_out), // output

.gt0_eyescantrigger_in (gt0_eyescantrigger_in), //0

//----------------------- Receive Ports - CDR Ports ------------------------

.gt0_rxcdrhold_in (gt0_rxcdrhold_in), //0

//----------------- Receive Ports - Clock Correction Ports -----------------

.gt0_rxclkcorcnt_out (gt0_rxclkcorcnt_out), // output

//---------------- Receive Ports - FPGA RX Interface Ports -----------------

.gt0_rxusrclk_in (gt0_rxusrclk_i), // rxusrclk

.gt0_rxusrclk2_in (gt0_rxusrclk2_i), // rxusrclk2

//---------------- Receive Ports - FPGA RX interface Ports -----------------

.gt0_rxdata_out (gt0_rxdata_out), // 接收数据

//----------------- Receive Ports - Pattern Checker Ports ------------------

.gt0_rxprbserr_out (gt0_rxprbserr_out), // output

.gt0_rxprbssel_in (gt0_rxprbssel_in), // 0

//----------------- Receive Ports - Pattern Checker ports ------------------

.gt0_rxprbscntreset_in (gt0_rxprbscntreset_in), // 0

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

.gt0_rxdisperr_out (gt0_rxdisperr_out), // output

.gt0_rxnotintable_out (gt0_rxnotintable_out), // output

//------------------------- Receive Ports - RX AFE -------------------------

.gt0_gtxrxp_in (gt0_gtxrxp_in), // 管脚RXP

//---------------------- Receive Ports - RX AFE Ports ----------------------

.gt0_gtxrxn_in (gt0_gtxrxn_in), // 管脚RXN

//------------------- Receive Ports - RX Equalizer Ports -------------------

.gt0_rxdfelpmreset_in (gt0_rxdfelpmreset_in), // 0

.gt0_rxmonitorout_out (gt0_rxmonitorout_out), // 0

.gt0_rxmonitorsel_in (gt0_rxmonitorsel_in), // 0

//------------- Receive Ports - RX Fabric Output Control Ports -------------

.gt0_rxoutclkfabric_out (gt0_rxoutclkfabric_out), // output

//----------- Receive Ports - RX Initialization and Reset Ports ------------

.gt0_gtrxreset_in (gt0_gtrxreset_in), // 0

.gt0_rxpmareset_in (gt0_rxpmareset_in), // 0

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

.gt0_rxchariscomma_out (gt0_rxchariscomma_out), // output

.gt0_rxcharisk_out (gt0_rxcharisk_out), // rxcharisk

//------------ Receive Ports -RX Initialization and Reset Ports ------------

.gt0_rxresetdone_out (gt0_rxresetdone_out), // output

//------------------- TX Initialization and Reset Ports --------------------

.gt0_gttxreset_in (gt0_gttxreset_in), // 0

.gt0_txuserrdy_in (gt0_txuserrdy_in), // 1

//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------

.gt0_txchardispmode_in (gt0_txchardispmode_in), // 0

.gt0_txchardispval_in (gt0_txchardispval_in), // 0

//---------------- Transmit Ports - FPGA TX Interface Ports ----------------

.gt0_txusrclk_in (gt0_txusrclk_i), // txusrclk

.gt0_txusrclk2_in (gt0_txusrclk2_i), // txusrclk2

//---------------- Transmit Ports - Pattern Generator Ports ----------------

.gt0_txprbsforceerr_in (gt0_txprbsforceerr_in), // 0

//-------------------- Transmit Ports - TX Buffer Ports --------------------

.gt0_txbufstatus_out (gt0_txbufstatus_out), // output

//---------------- Transmit Ports - TX Data Path interface -----------------

.gt0_txdata_in (gt0_txdata_in), // 发生数据

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

.gt0_gtxtxn_out (gt0_gtxtxn_out), // 管脚TXN

.gt0_gtxtxp_out (gt0_gtxtxp_out), // 管脚TXP

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

.gt0_txoutclk_out (gt0_txoutclk_i), // output

.gt0_txoutclkfabric_out (gt0_txoutclkfabric_out), // output

.gt0_txoutclkpcs_out (gt0_txoutclkpcs_out), // output

//------------------- Transmit Ports - TX Gearbox Ports --------------------

.gt0_txcharisk_in (gt0_txcharisk_in), // txcharisk

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

.gt0_txresetdone_out (gt0_txresetdone_out), // output

//---------------- Transmit Ports - pattern Generator Ports ----------------

.gt0_txprbssel_in (gt0_txprbssel_in), // 0

.gt0_qplloutclk_in (gt0_qplloutclk_i), // from common

.gt0_qplloutrefclk_in (gt0_qplloutrefclk_i) // from common

);

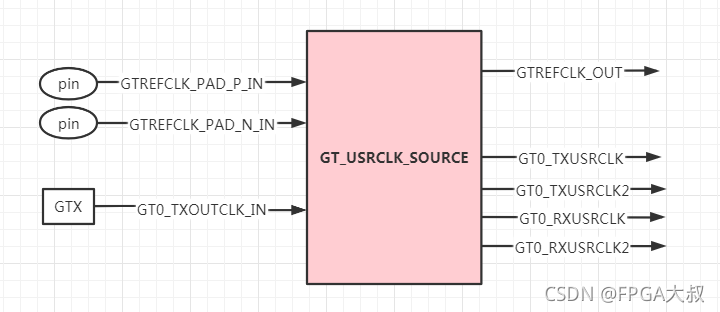

1.1.1 gt_usrclk_source

GTX的时钟子模块。

学习官方例程除了学习IP的用法外,另外一点就是学习官方大佬的代码,学习优秀的代码!包括代码规范、实现方式以及模块划分。

我们自己做项目的时候也要注意这一点,时钟最好单独设计为一个时钟子模块,提供整个工程所需的全部逻辑内部时钟。

用个框图来表示这个模块的功能:

至于具体实现方式,也很简单,用了两个原语:IBUFDS 、BUFG。

后面空了会详细出一个系列专讲Xilinx原语。

想要更多了解GTX的时钟,欢迎翻阅本系列第二篇(二)GTX时钟篇。

Xilinx FPGA平台GTX简易使用教程(二)GTX时钟篇

1.1.2 gt_common

这个模块主要是对GTXE2_COMMON原语的例化。

原语内容较多,这里不进行介绍。保持默认就好。

1.1.3 gt_common_reset

顾名思义,这个模块是对common的复位,也就是对QPLL的复位。保持默认就好。

实际上,我们进一步研究示例就会发现,该复位根本没有使用!为什么呢?不复位也能正常工作?对复位有兴趣的欢迎翻阅系列第三篇(三)GTX复位与初始化。

Xilinx FPGA平台GTX简易使用教程(三)GTX复位与初始化

1.2 frame_gen

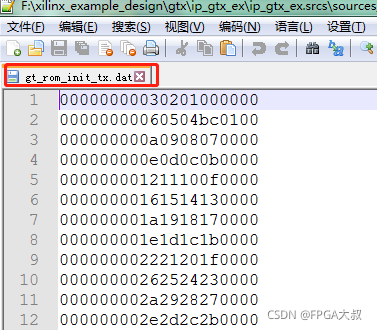

开门见山的说,这就是一个数据产生模块。只用于仿真测试,仔细研究你就发现它数据产生的方式比较有意思:从文件中读取!我们再回到工程结构目录,会看到有两个Data Files:

gt_rom_init_rx.dat、gt_rom_init_tx.dat

一个发送数据的文件,一个接收数据的文件。

再打开发送这个文件,如下图所示:

至于具体怎么实现文件数据读取,后面空了笔者也会出一篇文章,介绍在仿真中,对文件的读和写。

1.3 frame_check

数据检查模块,将接收到的数据和发送的数据进行比对,如果有误,就给error信号。可以学习这种设计思路,保障数据收发的准确性。

二、GTX收发测试

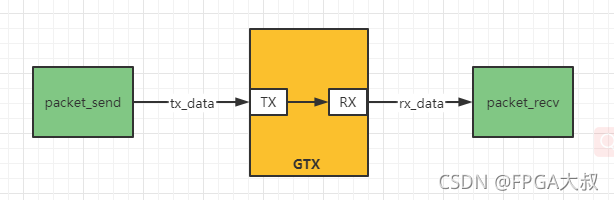

GTX的示例工程基本介绍完毕,但是那毕竟是别人的。如果我们自己想把GTX跑起来呢?很简单,把示例工程的frame_gen数据产生模块删掉,换上我们自己的发送数据模块packet_send;将frame_check数据检查模块删掉,换上我们自己的接收数据模块packet_recv。最后加个TOP顶层,将packet_send、packet_recv、gt_support三个模块连起来就好。

注:测试工程为回环,发送端口直接怼到接收端口。

2.1 对support模块的整合

support模块前面已经介绍过,是使用GTX的核心。所以我们对GTX的使用也是基于该模块。

直接上干货吧,需要做以下改动:

将发送/接收数据端口开放到外层,TOP才能模块连接;包含数据总线tx/rx_data和控制总线tx/rx_charisk;

将gt0_data_valid_in信号直接置1;

2.2发送模块

添加我们需要发送的数据,可以加上帧头(sof)、帧尾(eof)信号便于接收模块判断。

发送模块需要输出两个信号(这里的位宽由GTX IP配置决定):

tx_data[31:0] :需要发送的数据

tx_char[3:0] :K码指示,每1bit对应1个字节的数据;0:表示发送的是数据;1:表示发送的是K码。

需要注意的是,在发送数据之前要先发一个K码,以便接收数据对齐。

2.3接收模块

对GTX接收到的数据进一步处理,可通过检测帧头(sof)、帧尾(eof)信号,来接收一个完整的帧数据。也可以对接收的数据与发送数据比对,检查是否有误。

没什么好讲的,略过吧。

2.4仿真验证

仿真tb文件主要产生时钟激励,和产生需要发送的数据。

因为我们是回环,所以记得tb里面将TX / RX进行短接,注意_N对_N,_P对_P。

另外值得一提的是,我们参考时候为差分输入,这里简单提供一种差分时钟的testbench写法:

wire Q0_CLK1_GTREFCLK_PAD_N_IN;

reg Q0_CLK1_GTREFCLK_PAD_P_IN;

wire DRP_CLK_IN_N;

reg DRP_CLK_IN_P;

initial begin

Q0_CLK1_GTREFCLK_PAD_P_IN = 0;

DRP_CLK_IN_P = 0;

end

always #3.2 Q0_CLK1_GTREFCLK_PAD_P_IN = ~Q0_CLK1_GTREFCLK_PAD_P_IN;

always #5 DRP_CLK_IN_P = ~DRP_CLK_IN_P;

assign Q0_CLK1_GTREFCLK_PAD_N_IN = ~Q0_CLK1_GTREFCLK_PAD_P_IN;

assign DRP_CLK_IN_N = ~DRP_CLK_IN_P;

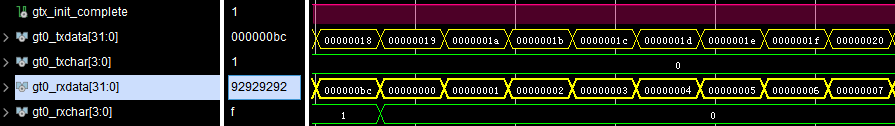

最后,我们来看一下仿真结果:

输入: 0-100的累加数(只截取了0-7)

输出:0-100的累加数(只截取了0-7)

OK,回环完成。

后记

整个GTX的介绍到这里暂告一段落,待笔者对齐有进一步更深的理解时再做补充。补充内容可能包括具体项目应用、GT高速接口的底层原理等。

按照笔者的习惯,基本以原理介绍、系统组成、方案设计为主,而对于具体的代码,笔者是不会在文章中具体写出来的。所以,这些测试工程我后面会以文件的形式放上来。

下一个系列,我们将开始SRIO。

随笔者一起,将接口撸个遍吧!

审核编辑:汤梓红

-

FPGA

+关注

关注

1664文章

22502浏览量

639106 -

GTX

+关注

关注

0文章

36浏览量

11485

发布评论请先 登录

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

青翼基于KU115FPGA 高性能数据预处理载板-PCIe信号处理板-FPGA载板

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

使用Xilinx 7系列FPGA的四位乘法器设计

Xilinx FPGA串行通信协议介绍

请问如何将蜂鸟E203移植到Xilinx NEXYS A7 FPGA 开发板上?

【VPX650 】青翼凌云科技基于 VPX 系统架构的 VU13P FPGA+ZYNQ SOC 超宽带信号处理平台

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX双FMC接口通用信号处理平台

一文详解xilinx 7系列FPGA配置技巧

【TES807】青翼凌云科技基于 XCKU115 FPGA 的双 FMC 接口万兆光纤传输信号处理平台

Xilinx FPGA平台GTX简易使用教程(五)

Xilinx FPGA平台GTX简易使用教程(五)

评论