引言

LED器件发出的光子往往会被氧化铟锡(ITO)透明电极与空气/树脂界面的全内反射(TIR)捕获在LED芯片内,导致光提取效率较低。通过在氧化铟锡电极表面上形成纳米尺度的图案,可以有效地降低该界面处的全内反射,该图案的尺寸小于发射光的波长,以允许更多的光从发光二极管发射出去。

我们提出了一种双层透明氧化铟锡(ITO)顶部电极方案,并演示了GaN基发光二极管光输出功率的提高。所提出的双层结构由具有随机分布的球形纳米图案的层和预退火底层组成,所述随机分布的球形纳米图案仅通过无掩模湿法蚀刻工艺获得,所述预退火底层用于保持电极的电流扩散。观察到表面形貌和光电性能取决于蚀刻持续时间。该电极显著提高了氮化镓基发光二极管的光输出功率,增强因子为2.18在100毫安时,与参考发光二极管相比,电气性能没有下降。

实验

为了比较本方法中的光提取效率,我们制备了具有如下三种类型ITO电极的发光二极管:(1)初始厚度为400纳米的单层电极(表示为SL400);(2)初始厚度为800纳米的单层电极(表示为SL800);(3)双层电极,具有初始厚度为400纳米的顶层和初始厚度为400纳米的底层(表示为DL400(顶部)/400(底部))。双层纳米结构氧化铟锡电极(DL400/400)通过首先沉积400纳米厚的底部氧化铟锡层,然后在空气中于600℃退火1分钟来制造,使得该层能够抵抗后续的湿法蚀刻工艺。厚度为400纳米的第二氧化铟锡层沉积在退火的氧化铟锡层上。纳米结构的氧化铟锡层是通过将沉积的第二氧化铟锡层浸入用去离子水稀释(1∶6)的缓冲氧化物蚀刻剂(BOE)溶液中而形成的。通过在BOE溶液中蚀刻0、20、40、60、90和120秒来控制表面纳米结构,以观察电极形态的演变。蚀刻后,氧化铟锡层在空气中于600℃退火1分钟。对于单层纳米结构的氧化铟锡电极(SL400和SL800),在与双层氧化铟锡顶部电极相同的条件下图案化沉积层和纳米结构表面。

利用金属有机化学气相沉积系统,在蓝宝石衬底上生长了由未掺杂氮化镓、掺硅氮氮化镓、铟镓氮/氮化镓多量子阱有源层和掺镁磷氮化镓组成的蓝色发光二极管外延层。采用电感耦合等离子体台面刻蚀法制作了300×300 μm芯片尺寸的蓝色发光二极管器件。通过电子束蒸发沉积钛/金(厚度为50/200纳米)层作为n型电极。p-GaN层的欧姆接触是通过电子束蒸发将p-接触透明铜铟氧化物(3 nm) /ITO电极沉积到p-GaN上来实现的,并且该膜随后在纯氧环境中在600℃下退火1分钟。通过电子束蒸发在氧化铟锡透明电极上沉积铬/金(50/200纳米)焊盘电极,完成了发光二极管结构。

结果和讨论

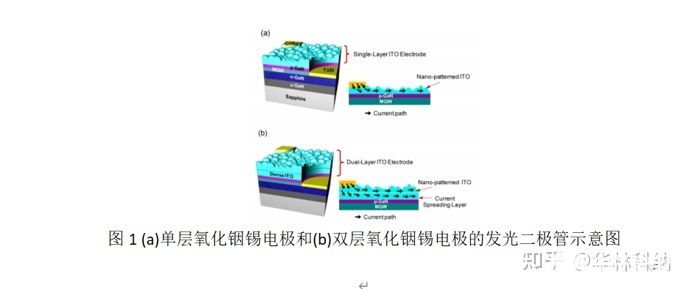

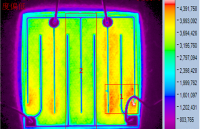

我们已经成功地展示了具有这种双层ITO电极的超高亮度和稳定开启电压的ITO/GaN薄膜LED。图1示出了具有单层(图1(a))和双层(图1(b)) ITO电极的发光二极管的示意图。单层和双层设计都具有纳米结构顶层,该顶层通过浸渍湿法蚀刻工艺图案化,以最小化全内反射的光俘获。对于双层氧化铟锡,额外的致密氧化铟锡层被预沉积并在顶部图案化层下方退火,以保持良好的整体面内电子传导。

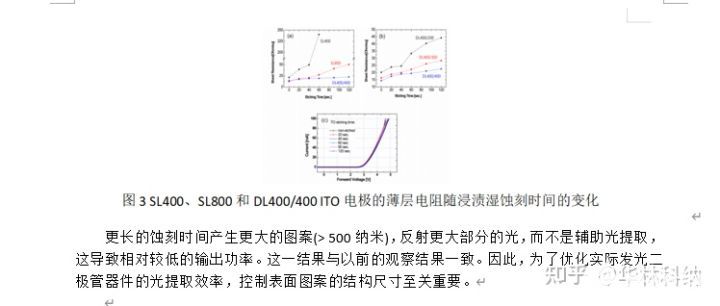

图3(a)示出了具有不同浸蚀时间的SL400、SL800和DL400/400电极的薄层电阻。在60秒的蚀刻时间内,SL400的薄层电阻从20欧姆/平方显著增加到250欧姆/平方。即使在蚀刻120秒后,在SL800中也没有观察到如此巨大的薄层电阻跳跃;薄层电阻保持低至50欧姆/平方。这表明SL400中的大部分400纳米氧化铟锡层在60秒后被蚀刻掉,而在SL800中,有限厚度的氧化铟锡保持未被蚀刻,因此是良好的电流扩散层。另一方面,即使在120秒的最长蚀刻之后,DL400/400 ITO电极的薄层电阻也仅从20欧姆/平方略微增加到22欧姆/平方。这些结果证明了氧化铟锡的薄层电阻很大程度上受蚀刻的影响,并且可以通过额外的预沉积和退火底层成功地保持较低,该底层用作有效的电流扩散层。

为了确定有效电流扩散的最佳厚度,我们还研究了底部氧化铟锡厚度对双层电极整体薄层电阻的影响。

由于BOE溶液在沉积(非晶)的顶部氧化铟锡层和退火的底部氧化铟锡(多晶)[10]之间具有非常好的蚀刻选择性,所以在湿浸蚀刻之后,底部层被期望保持几乎完整。我们通过制造发光二极管器件和增加DL400/400电极上的湿浸蚀刻时间来验证这一点,之后我们测量了它们的伏安特性(图3(c)),具有浸蚀ITO电极的DL400/400发光二极管的I-V曲线与具有未蚀刻ITO的发光二极管保持一致,即使在120秒的最长蚀刻时间之后。这表明退火的底部氧化铟锡在不牺牲器件性能的情况下,对长时间的湿浸蚀具有抵抗力。因此,添加预退火的底部氧化铟锡层是稳定电流扩散的有效方法,并且有助于防止操作期间的电退化。

总结

我们已经展示了双层纳米结构的ITO透明电极的制造,通过简单的无掩模浸渍湿法蚀刻工艺图案化,有效地提高了氮化镓基蓝色发光二极管的光提取效率。双层氧化铟锡电极的特点是具有优化表面纳米图案的纳米结构顶层,以大大减少发光二极管器件中的光截留,以及充当稳定电流扩散层的致密底层。DL400/400 ITO电极发光二极管在100毫安时的光输出功率是参考发光二极管的2.18倍。图案化层下的密集底部电流扩散层的存在稳定了双层电极的导电,并且没有观察到薄层电阻的显著退化。双层氧化铟锡设计和制造工艺可以有效地提高氮化镓蓝色发光二极管的光提取效率,而不牺牲其电性能。纳米图案化通过1至2分钟的可控湿浸蚀时间来完成,并且在高温炉中的退火时间(1分钟)比生长纳米线所需的时间短得多,生长纳米线需要在高温下进行数小时的处理。这种简单、低成本和可控的工艺很容易在大规模生产中应用于高亮度蓝光发光二极管,并有可能促进蓝光发光二极管在市场上的推广。

审核编辑:符乾江

-

led

+关注

关注

243文章

24434浏览量

687347 -

led灯

+关注

关注

22文章

1604浏览量

111096

发布评论请先 登录

湿法蚀刻的最佳刻蚀条件是什么

锂电工艺 |电极制造的高级处理技术:从湿法到干法的革新

半导体湿法腐蚀工艺中,如何选择合适的掩模图形来控制腐蚀区域?

湿法蚀刻工艺与显示检测技术的协同创新

半导体湿法flush是什么意思

晶圆蚀刻后的清洗方法有哪些

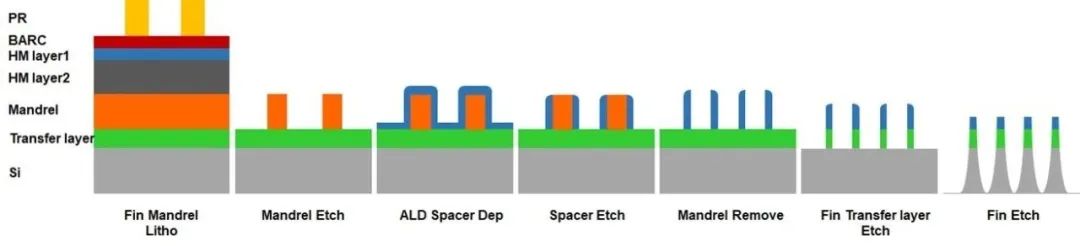

自对准双重图案化技术的优势与步骤

基于激光掺杂与氧化层厚度调控的IBC电池背表面场区图案化技术解析

使用无掩模湿法蚀刻LED的纳米图案双层ITO电极

使用无掩模湿法蚀刻LED的纳米图案双层ITO电极

评论