小芯片(Chiplet)已经成为当今大厂角逐的一大方向,对于小芯片来说,需要一种芯片到芯片的互连/接口技术,现在已有多种Die-to-Die接口可以满足这类需求。其中,基于SerDes的或并行的Die-to-Die接口在数据速率、引脚数量和成本等方面都有其独特的优势。但在设计用于诸如数据中心、人工智能 (AI) 训练或推理、服务器和网络等高性能计算 (HPC) 应用的高端Muiti-die SoC时,为了让不同的供应商开发的Multi-Die SoC实现互操作,业界正着力于建立Multi-Die的互连标准,以维护一个成功的生态系统。

OpenHBI凭借最高边缘密度标准从众多die-to-die标准中突出重围,成为HPC等对小芯片间传输带宽要求极高的系列应用的最佳接口标准。

为何使用并行 Die-to-Die 接口?

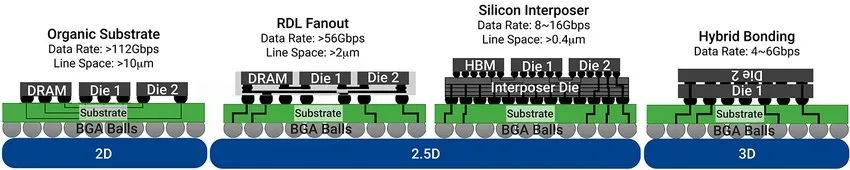

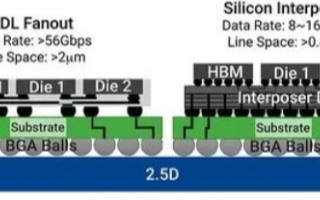

现在多家芯片厂商利用小芯片模型将芯片集成到现有的高级封装类型中,这些裸片可以是不同工艺节点的,裸片可以并排放置,并通过专用die-to-die接口相连接,这是一种普遍且成本较低的方法。如想获得更高的密度,可以将这些组块封装在2.5D或3D设计中。

在此,我们先科普下常见的三种封装形式,一个是2D封装,把各个Chiplet组装在有机基材和层压板上;一个是2.5D封装,它的中介层使用硅或再分配层 (RDL) 扇出,用于在SoC中传递Chiplet间的信号;还有一个是3D封装,它使用混合粘合技术来垂直堆叠Chiplet。

▲ 图1 封装选项

其中2.5D封装由于采用RRL扇出技术,能够桥接2D技术的低成本和硅中介层的密度,又有许多代工厂以及传统的OSAT提供商可提供此类服务,进一步降低了成本,因此成为了一种有吸引力的选择。

对于那些对封装成本和复杂度不敏感的高性能计算 SoC,并行Die-to-Die接口已成为首选技术。这主要是因为,并行Die-to-Die接口基本上都包含了大量的(上千个)IO 引脚,来驱动跨Chiplet的单端信号。由于每个引脚的数据速率仅为几个G字节/秒 (Gbps)(8至16 Gbps),且Chiplet之间的距离仅为几毫米(3至5毫米),因此驱动器和接收器都可以简化,同时实现远低于1e-22至1e-24的系统误码率 (BER)。不需要额外的纠错机制,例如前向纠错 (FEC) 和重试,系统BER就可以满足要求,从而避免增加链路复杂性和延迟。

通过简化IO、消除串并转换 (SerDes) 步骤,并避免超高速信号传输,并行Die-to-Die接口能够实现极高的能效和较低的延迟,同时支持整个链路的极高吞吐量。因此,并行Die-to-Die接口对于不受封装成本和装配限制的高性能计算应用SoC非常有吸引力。

Die-to-Die接口标准应运而生

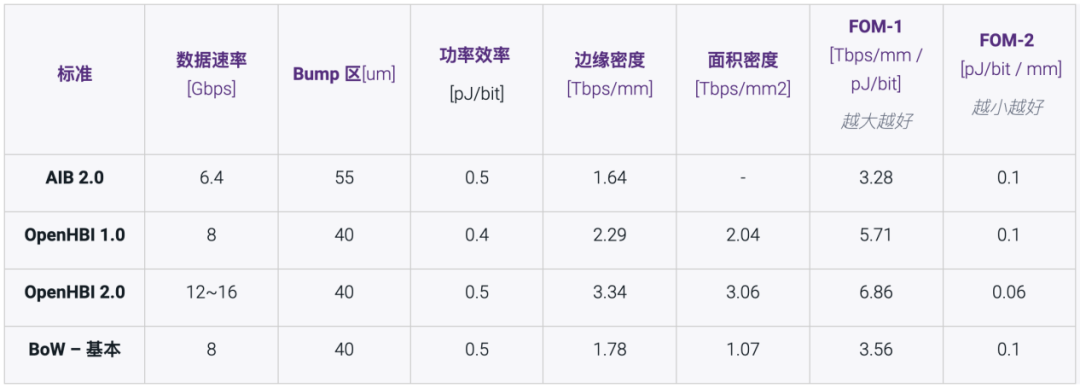

现在的小芯片方案,各家都为并行Die-to-Die接口部署了许多专有架构。为了建立一个稳健的生态系统,让不同的供应商所开发的以及不同功能的Chiplet互联操作,行业开始制定Die-to-Die接口标准,主要包括AIB、OpenHBI、BoW等,为先进封装中的并行Die-to-Die接口提供特性。表1显示了不同标准的主要特性比较。

▲ 表1 先进封装的并行Die-to-Die接口标准 (来源:OCP Tech Week全球技术峰会,2020年11月)

先进封装由于凸块间距大,封装路由密度高,在同等能效的情况下,对外形尺寸和边缘效率的要求更高。在以上这些标准中,OpenHBI能提供最高边缘密度的标准,非常适用于必须在两个Chiplet之间传输极高带宽的应用。它可达到每引脚8Gbps的速度,在最大数据速率下可以达到3mm的最大互连长度并实现小于或等于0.5pJ/bit的功耗目标。

什么是 OpenHBI?

OpenHBI利用JEDEC的HBM3电气特性和IO类型来降低风险。它使用低电压和未端接的单端 DDR 信号来传输Chiplet之间的数据。OpenHBI标准具有许多关键特征:

整合多个OpenHBI兼容的Die-to-Die接口,实现互操作性

利用JEDEC HBM3 IO类型和电气特性

可与支持HBM存储器和OpenHBI标准的双模HBM主机控制器互操作

支持硅中介层和晶圆级集成扇出或同等技术

实现对称Die-to-Die接口

实现目标速度:每引脚 8Gbps,正迈向12-16Gbps

在最高数据传输速率时提供长达3mm的互连距离

实现小于等于0.5pJ/bit的功耗目标

提供大于1.5T位/毫米(包括发射器和接收器)的线性(边缘)带宽密度

定义 PHY 和逻辑 PHY 抽象层,轻松适配上层

支持正常的和旋转的Chiplet方向

可以调整带宽和边缘(DW 数量)以匹配各种用例

支持小芯片 (Chiplet) 配置和测试 (CCT) 接口

支持通道修复,提高制造良率

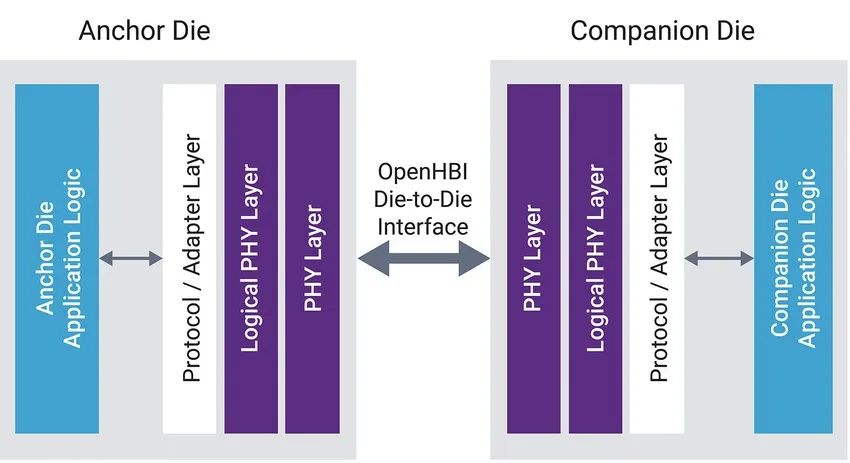

OpenHBI标准主要针对图2所示的下层(PHY和逻辑PHY层),然后将适配器层用于与上层(协议层)进行连接。因此,系统可实现不依赖于各个应用所用的协议。

▲ 图2 OpenHBI 接口逻辑划分

PHY层主要执行提供时钟、变速器(数据速率转换 N:1)、校准和训练、通道修复以及数据传输和恢复的功能。如果需要,逻辑 PHY层将执行以下功能:奇偶校验生成和校验、数据成帧和对齐、数据总线反向、位重新排序。

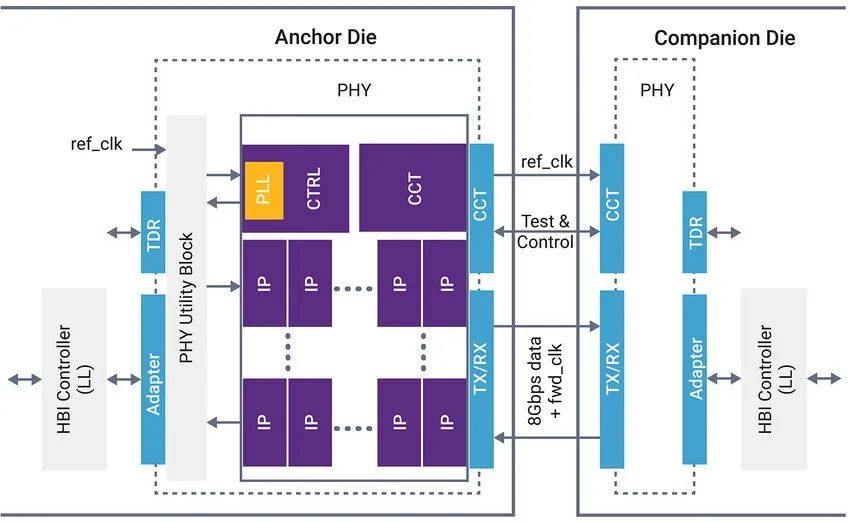

图3展示了一种OpenHBI PHY实现方案,可以将不同的功能分割到不同的实现中。

▲ 图3 OpenHBI PHY IP模块图

PHY使用时钟转发技术,其中传输时钟和数据也在Chiplet之间传输。接收端基于DLL的简单数据恢复电路,可节省功耗和面积。

除了有效载荷数据路径外,PHY还实现低速CCT,可供锚芯片和小芯片用于传达配置和状态参数以及控制DWORD初始化、校准和测试过程。OpenHBI PHY实现I3C、JTAG和供应商自定义信号。此外CCT将参考时钟从锚芯片传播到小芯片Chiplet,以便它们共享相同的时钟参考。

OpenHBI PHY的其他主要功能包括:

带有APB/TDR接口的配置端口,用于访问内部控制和状态寄存器 (CSR)

可配置PHY,支持多种DWORD数量,以适应具体用例

裸片测试(已知良好Chiplet)和封装后测试的综合可测试性,包括关键模块 BIST、各种环回模式、模式生成和匹配能力,以及生成重建的眼图,作为 pass/fail 测试。

新思科技IP助力小芯片的互联

一些芯片设计公司可能拥有开发自己的小芯片和IP的资源,但即使是较大的公司也负担不起内部开发所有IP的费用。他们可能希望采购第三方IP以节省时间和金钱。

在这样的背景下,新思科技可提供一系列Die-to-Die IP,包括高带宽互联 (HBI) 和基于SerDes的PHY和控制器。DesignWare HBI PHY IP支持多种标准,包括AIB、BoW和OpenHBI。该IP实现了一个宽并行和时钟转发的PHY接口,以先进的2.5D封装为目标,以利用基于内插器的技术中更精细的芯片到芯片连接。

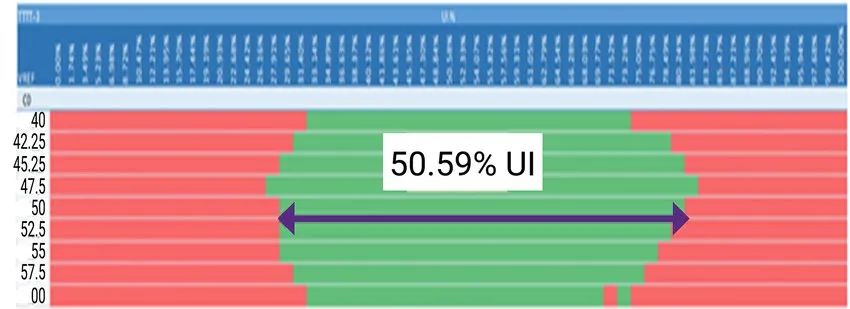

▲ 图4 使用新思科技HBI+PHY Die-to-Die链路的眼图

无疑,小芯片的发展前景广阔,尤其是摩尔定律走到极限的情况下,但是小芯片仍然面临诸多难题,如设计和集成、生态系统复杂性、制造/测试和产量,资质和可靠性、标准等,但业界正在围绕着这些难题逐个攻克,相信,未来会有更多的应用采用小芯片的方案。

原文标题:Chiplet互联难?解决方案在这儿

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

芯片

+关注

关注

462文章

53530浏览量

458837 -

封装

+关注

关注

128文章

9139浏览量

147861 -

服务器

+关注

关注

13文章

10093浏览量

90854

原文标题:Chiplet互联难?解决方案在这儿

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Chiplet成大芯片设计主流方式,开启IP复用新模式

数据中心光互联解决方案

北极雄芯开发的首款基于Chiplet异构集成的智能处理芯片“启明930”

先进封装Chiplet全球格局分析

chiplet和cowos的关系

互联与chiplet,技术与生态同行

奇异摩尔聚焦高速互联:Chiplet互联架构分析及其关键技术

Nordic Chiplet芯片级解决方案助力微型模块收集和传输心电图数据

西门子EDA创新解决方案确保Chiplet设计的成功应用

UCIe规范引领Chiplet技术革新,新思科技发布40G UCIe IP解决方案

最新Chiplet互联案例解析 UCIe 2.0最新标准解读

小芯片(Chiplet)互联解决方案

小芯片(Chiplet)互联解决方案

评论