薄膜集成电路是使用了薄膜工艺在蓝宝石、石英玻璃、陶瓷、覆铜板基片上制作电路元、器件及其接线,最后进行封装而成的。

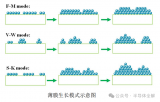

集成电路薄膜沉积工艺可以分为三类,为物理气相沉积(PVD)、化学气相沉积(CVD)和外延。

薄膜混合集成电路需要用的基片有多种,一般用得最多的是玻璃基片,其次是微晶玻璃和被釉陶瓷基片,有时也用蓝宝石和单晶硅基片。

薄膜工艺中包括了蒸发、溅射、化学气相淀积等。特点为电阻、电容数值控制较精确。

在薄膜电路中常见的有导电、电阻、介质和绝缘薄膜四种薄膜,导电薄膜的作用是互连线、焊接区和电容器极板。电阻薄膜的作用是形成微型电阻。介质薄膜的作用是当微型电容器的介质层。绝缘薄膜用作交叉导体的绝缘和薄膜电路的保护层。

本文综合自百度百科、行行查

审核编辑:何安

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54379浏览量

468992 -

半导体

+关注

关注

339文章

31192浏览量

266321

发布评论请先 登录

相关推荐

热点推荐

磁控溅射工艺时间对金属及氧化物靶材溅射速率的影响:基于台阶仪的薄膜厚度表征

监测往往误差较大,工程师们通常采用"以工艺时间换算薄膜厚度"的方法:在短时间内溅射沉积一定厚度的薄膜,经台阶仪测量折算出沉积速率,再按比例推算目标厚度所需的溅射时

NTC热敏芯片的焊接工艺

在不同的应用场景中,爱晟EXSENSE高精度NTC热敏芯片的焊接工艺亦有所不同。为了让大家更充分地了解EXSENSE热敏芯片的焊接工艺,今天为大家介绍一些常见的热敏

厚声贴片电阻的厚膜工艺与薄膜工艺有何区别?

厚声贴片电阻的厚膜工艺与薄膜工艺在 膜层厚度、制造工艺、性能表现、应用场景及成本结构 上存在显著差异,具体分析如下: 一、膜层厚度:物理维度的核心差异 厚膜

集成电路制造中薄膜生长工艺的发展历程和分类

薄膜生长是集成电路制造的核心技术,涵盖PVD、CVD、ALD及外延等路径。随技术节点演进,工艺持续提升薄膜均匀性、纯度与覆盖能力,支撑铜互连、高k栅介质及应变器件发展。未来将聚焦低温沉积、三维结构适配与新材料集成,实现性能与可靠

NTC热敏芯片键合工艺介绍

随着半导体技术的持续创新及进步,NTC热敏芯片键合工艺也不断发展。目前,芯片键合工艺为顺应行业发展需求,正逐步往高度集成、低功耗、高可靠的方向前进。为了让大家更充分地了解NTC

基于光学成像的沉积薄膜均匀性评价方法及其工艺控制应用

静电喷涂沉积(ESD)作为一种经济高效的薄膜制备技术,因其可精确调控薄膜形貌与化学计量比而受到广泛关注。然而,薄膜的厚度均匀性是影响其最终性能与应用可靠性的关键因素,其优劣直接受到电压、流速、针基距

台阶仪精准测量薄膜工艺中的膜厚:制备薄膜理想台阶提高膜厚测量的准确性

固态薄膜因独特的物理化学性质与功能在诸多领域受重视,其厚度作为关键工艺参数,准确测量对真空镀膜工艺控制意义重大,台阶仪法因其能同时测量膜厚与表面粗糙度而被广泛应用于航空航天、半导体等领域。费曼仪器

椭偏仪在半导体薄膜工艺中的应用:膜厚与折射率的测量原理和校准方法

半导体测量设备主要用于监测晶圆上膜厚、线宽、台阶高度、电阻率等工艺参数,实现器件各项参数的准确控制,进而保障器件的整体性能。椭偏仪主要用于薄膜工艺监测,基本原理为利用偏振光在薄膜上、下

在薄膜框架上提供的 PIN 二极管芯片 skyworksinc

电子发烧友网为你提供()在薄膜框架上提供的 PIN 二极管芯片相关产品参数、数据手册,更有在薄膜框架上提供的 PIN 二极管芯片的引脚图、接线图、封装手册、中文资料、英文资料,在

发表于 07-15 18:35

肖特基二极管四通道混频器芯片采用薄膜框架 skyworksinc

电子发烧友网为你提供()肖特基二极管四通道混频器芯片采用薄膜框架相关产品参数、数据手册,更有肖特基二极管四通道混频器芯片采用薄膜框架的引脚图、接线图、封装手册、中文资料、英文资料,肖特

发表于 07-15 18:33

薄膜晶体管技术架构与主流工艺路线

导语薄膜晶体管(TFT)作为平板显示技术的核心驱动元件,通过材料创新与工艺优化,实现了从传统非晶硅向氧化物半导体、柔性电子的技术跨越。本文将聚焦于薄膜晶体管制造技术与前沿发展。

芯片薄膜工艺是什么

芯片薄膜工艺是什么

评论