FIFO 最小深度计算

例子 - 1:f_wr 》 f_rd,连续读写

写时钟80MHz。

读时钟50MHz。

Burst_Len = 120,也就是要求至少安全写入120个数据。

连续写入和连续读取,无空闲时间,写入后立即开始读取 ,读写宽度相同。

Sol:

写速率 》 读速率,FIFO迟早会被写满,但它要求至少写入120个数据后FIFO不满。

写入120个数据耗时 120 * 12.5 ns = 1500 ns。

写入开始后FIFO内数据以 30M/Date 速率增加。

数据增加持续了 1500 ns ,FIFO最小深度:0.0000015 * 30000000 = 45

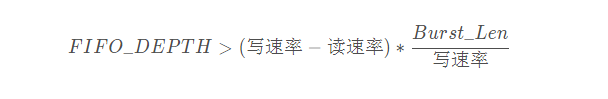

例子-1 总结公式:

例子 - 2 :f_wr 》 f_rd & 写速率 》 读速率,非连续读写

写时钟80MHz。

读时钟50MHz。

Burst_Len = 120,也就是要求至少安全写入120个数据。

写入后立即开始读取 ,读写宽度相同。

2个时钟中有1个数据写入(写速率:80M * 1/2 = 40M)。

4个时钟中有1个数据读出(读速率:50M * 1/4 = 12.5M)。

Sol:

FIFO迟早会被写满 ,但它要求至少写入120个数据后FIFO不满。

写一个数据耗时:2/80MHz = 25ns

需要至少写入120数据,耗时:25 * 120 = 3000ns

例子2只是读写速率和例子1不同,可以直接用的公式(1) :

FIFO_DEPTH 》 (写速率-读速率)* Burst_Len/写速率 = (40M-12.5M)*120/40M = 83

例子 - 3:f_wr 《 f_rd ,连续读写

写时钟30MHz。

读时钟50MHz。

Burst_Len = 120,也就是要求至少安全写入120个数据。

连续写入和连续读取,无空闲时间,写入后立即开始读取 ,读写宽度相同。

Sol:

FIFO_DEPTH 》 1 即可。读速率比写速率快,数据不会滞留。

例子 -4:f_wr 《 f_rd & 写速率 》 读速率,非连续读写

写时钟30MHz。

读时钟50MHz。

Burst_Len = 120,也就是要求至少安全写入120个数据。

2个时钟中有1个数据写入(写速率:30M * 1/2 = 15M)。

4个时钟中有1个数据读出(读速率:50M * 1/4 = 12.5M)。

Sol:

虽然写时钟小于读时钟频率,但是,宏观上写速率大于读速率。可以直接用的公式(1) :

FIFO_DEPTH 》 (写速率-读速率)* Burst_Len/写速率 = (15M-12.5M)*120/15M = 20

例子 1-4总结

当满足以下所有条件时,就可使用公式(1):

写速率 》 读速率时。

读写有效数据占比 《= 0.5,且 有效数据均匀分布在所有时间上。或者说,无论微观时间、还是宏观时间上,读写速率近似于 时钟频率 * 有效数据占比时。

当每100个时钟写80个数据时,微观时间上的写速率与数据排列有关,不能将宏观写速率带入式子(1)

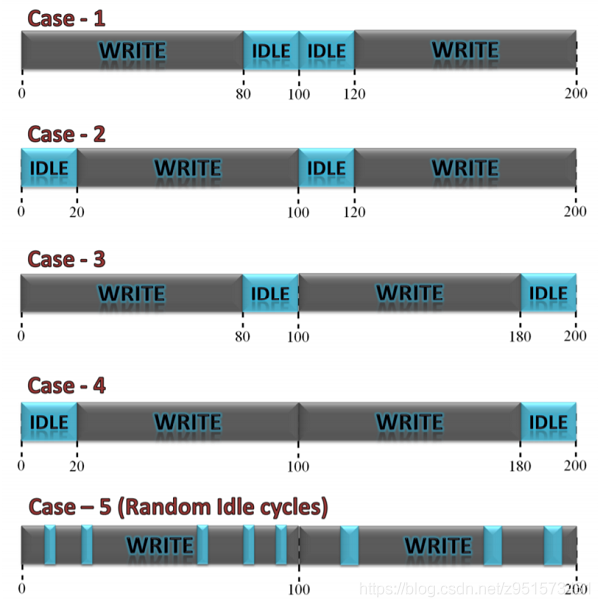

例子 - 5

读写时钟频率相同。

100个时钟有80个数据写入。

10个时钟有8个数据读出。

Burst_Len = 160,也就是要求至少安全写入160个数据 。

Sol:

宏观上,读写速率相同;当FIFO足够深时,FIFO不会溢出。

微观上,写速率有多种情况:

为了求出安全的最小FIFO深度,我们需要考虑最差的情况。

最差的情况下,写入和读出速度应该相差最大。写入要最快,读出要最慢。FIFO内的数据增加最快。

从上表中可得出:最大写入速率是case 4(back to back write,中间没有空闲,速率为时钟频率 f,写入了160个 )。

读出要最慢,在写160个数据期间,读相比于写端可以认为是速率均匀的,速率为 f*8/10,读出了160 * 8 /10 = 128个。

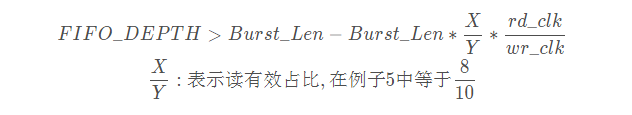

因此 FIFO_DEPTH 》 160 - 128 = 32。用公式(1)也可以得到这个结果,写速率带入f而不是f*8/10。

总结:求解步骤

考虑最差的情况下,写入和读出速度应该相差最大。写入要最快,读出要最慢。FIFO内的数据增加最快。

只考虑宏观上写入速率 》= 读出速率的情况。

确定写入Burst_Len大小。Burst_Len指的是一段连续写入区间,由于没有空隙这段时间写入速率最大最多。一定要对具体的数据分布情况具体分析,Burst_Len一定是最长的一段连续写入区间。

在微观上,确定最大写入速率。Burst_Len足够长时,写入速率 = 写时钟频率(back to back write)。而在例子 - 2中,Burst_Len很短,没有back to back write,写入速率 = 写时钟频率 * 写有效占比。

在微观上,确定最小读出速率。一般认为读出速率是均匀的,读出速率 = 读时钟频率 * 读有效占比。

带入公式(1)计算。

Burst_Len足够长时,将上面读出写入速率带入公式(1),可得到网上讨论最多的FIFO深度求解公式:

不建议直接用公式(2)无脑计算,上式只有Burst_Len足够长,发生back to back write时才适用。建议根据1~6步骤,判断微观写速率是否均匀,带入式子(1)计算。

编辑:jq

-

数据

+关注

关注

8文章

7349浏览量

95024 -

fifo

+关注

关注

3文章

407浏览量

45907 -

计算

+关注

关注

2文章

460浏览量

40129

原文标题:FIFO 最小深度计算

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FT245BQ USB FIFO:实现高效数据传输的利器

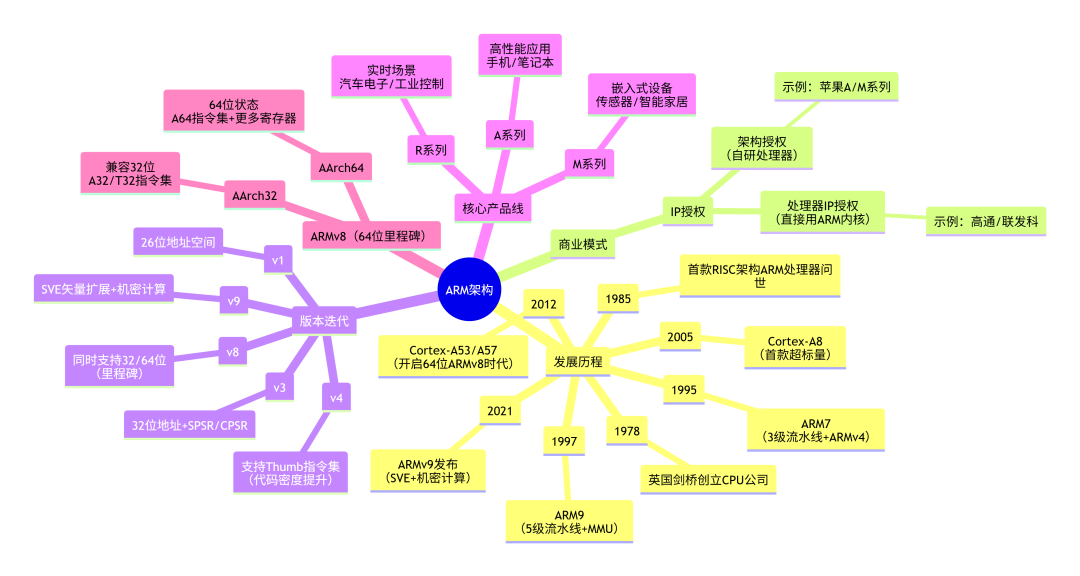

深度解析 ARM 架构:从剑桥车库到未来计算

大神们,想知道你们都用什么ide编程调试器? Arduino IDE?还是 e2studio ?还有其他吗?哪个好用呢

求助,关于串口设备驱动fifo问题

大模型推理显存和计算量估计方法研究

海光DCU率先展开文心系列模型的深度技术合作 FLOPs利用率(MFU)达47%

cy7c68013a异步slave fifo模式,外部mcu无法读写fifo怎么解决?

存储示波器的存储深度对信号分析有什么影响?

跪求各路大神labview如何计算AQI

AN65974示例如何链接fifo_slave_block 和 video_out的IP块?

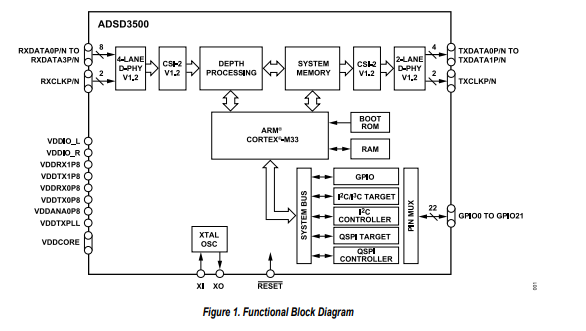

ADSD3500飞行时间深度成像信号处理器技术手册

你们知道FIFO最小深度计算吗

你们知道FIFO最小深度计算吗

评论