下列 时序检查语句 错误的是()

A. $setup(posedge clk, data, tSU)

B. $hold(posedge clk, data, tHLD)

C. $setuphold(posedge clk, data, tSU, tHLD)

答案:A

解析:

在时序检查函数中,$setup 函数比较特殊,格式是:

$setup(data_event, reference_event, limit);

其他常见的检查是:

$.。..。.(reference_event, data_event, limit);

假设信号名称为 data,时钟 clk 的上升沿触发 posedge clk,要求 setup 满足 tSU,则

$setup(data, posedge clk, tSU);

常用的时序检查语句

(1)setup 建立时间检查

$setup(data, posedge clk, tSU);

(2)hold 保持时间检查

$hold(posedge clk, data, tHLD);

(3)setuphold 建立/保持时间检查

$setuphold(posedge clk, data, tSU, tHLD);

(4)width 脉冲宽度检查

$width(posedge clk, 4);

(5)skew 时钟歪斜检查

$skew(posedge clk1, posedge clk2, 4);

(6)period 时钟周期检查

$period(posedge clk, 5);

(7)recovery 复位信号的恢复时间检查

$recovery(posedge rst, posedge clk, 3);

(8)removal 复位信号的移除时间检查

$removal(posedge rst, posedge clk, 3);

(9)recrem 复位信号的恢复/移除时间检查

$recrem(posedge rst, posedge clk, recovery_limit, removal_limit);

四个基础的时序分析

(1)对于时钟和数据信号,分析setup建立时间和hold保持时间

setup 建立时间:在有效的时钟沿来临前,数据需要保持稳定的最短时间,简写为Tsu;

hold 保持时间:在有效的时钟沿来临后,数据需要保持稳定的最短时间,简写为 Th;

(2)对于时钟和异步复位信号,分析recovery恢复时间和removal移除时间

recovery 恢复时间:在有效的时钟沿来临前,异步复位信号保持稳定的最短时间;

removal 移除时间:在有效的时钟沿来临后,异步复位信号保持稳定的最短时间,在这个时间以后,才可以移除复位信号;

责任编辑:haq

-

Verilog

+关注

关注

31文章

1374浏览量

114713 -

时钟

+关注

关注

11文章

1999浏览量

135226

发布评论请先 登录

USB RFID读写器的四个常见应用

PCBA生产过程的四个主要环节?

合科泰MOSFET选型的四个核心步骤

vivado时序分析相关经验

NucleiStudio如何生成.verilog文件和.dasm文件,以及对.dasm文件中自定义指令反汇编结果分析

用于 GSM/ GPRS (824-915 MHz) (1710-1910 MHz) 的 Tx-Rx 四频前端模块,带四个线性 TRx 开关端口 skyworksinc

用于 GSM/GPRS (824-915 MHz) (1710-1910 MHz) 的 Tx-Rx 四频前端模块,带四个线性 TRx 开关端口 skyworksinc

用于四频 GSM / GPRS / EDGE 的 Tx-Rx FEM,具有四个线性 TRx 开关端口和双频 TD-SCDMA skyworksinc

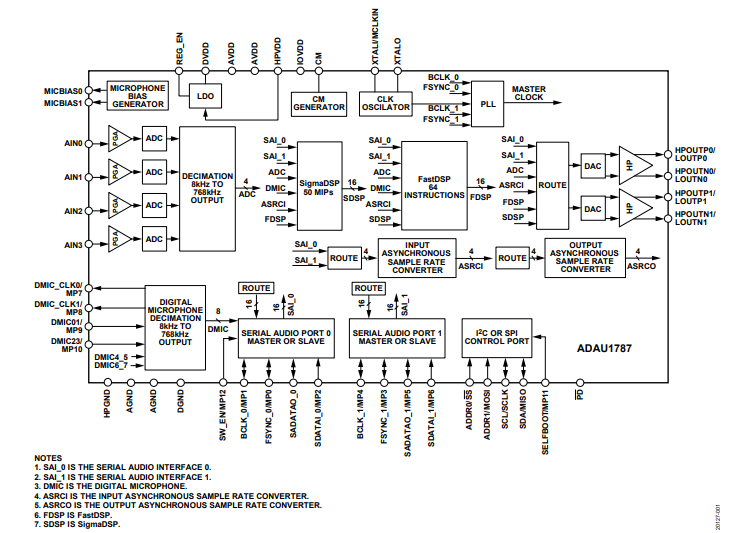

ADAU1787四个ADC、两个DAC、带音频DSP的低功耗编解码器技术手册

PLC产品故障问题测试的四个部分

从四个方面深入剖析富捷电阻的优势

Verilog中四个基础的时序分析

Verilog中四个基础的时序分析

评论