概述

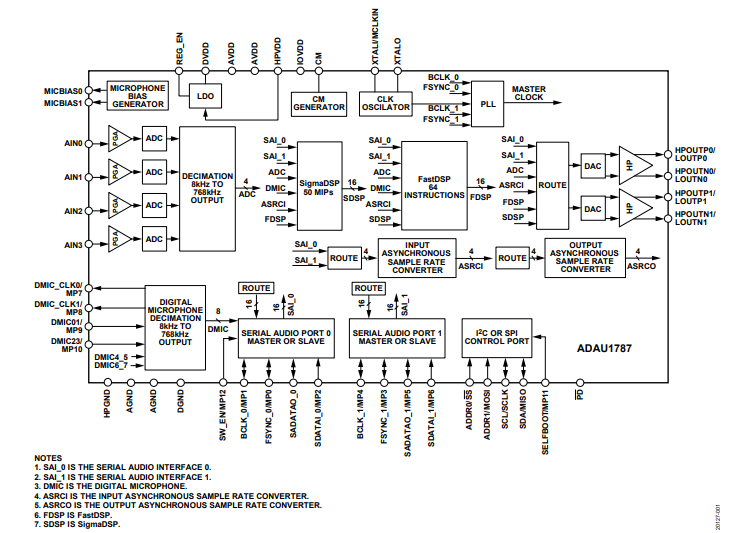

ADAU1787 是一款具有四个输入和两个输出的编解码器,其中整合了两个数字信号处理器 (DSP)。从模拟输入到 DSP 内核再到模拟输出的路径已针对低延迟进行优化,适用于噪声消除耳机。通过加入少量无源组件,ADAU1787 提供了完整的耳机解决方案。

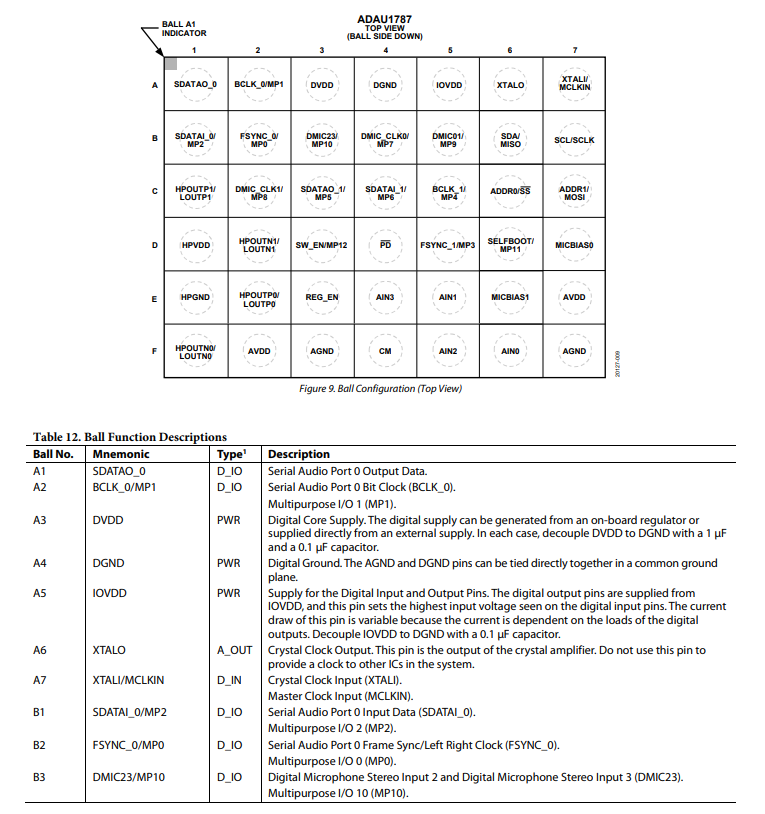

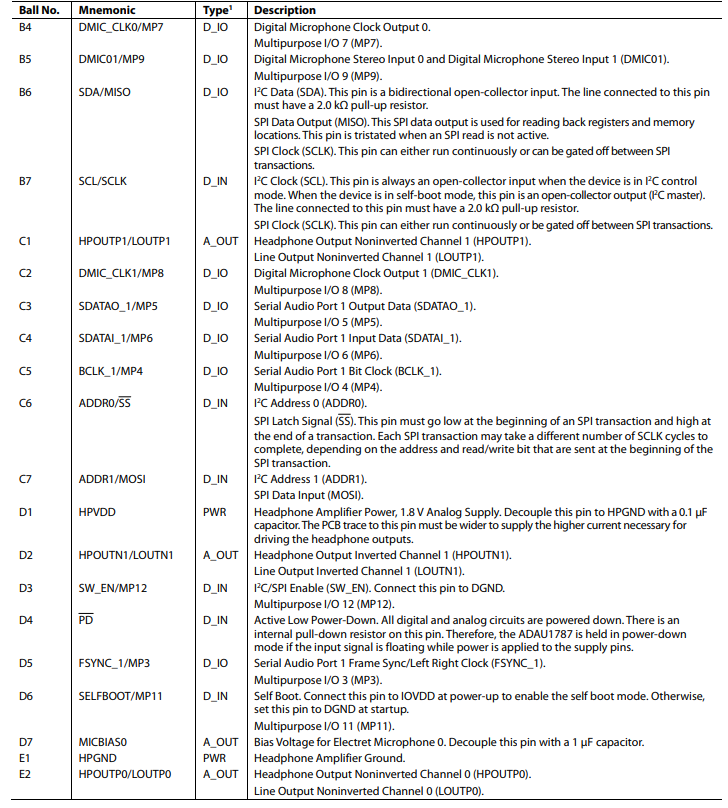

请注意,在整个数据手册中,多功能引脚(例如 BCLK_0/MP1)可能使用引脚全称指代,也可能使用引脚的单一功能指代,例如 BCLK_0(在仅与该功能相关时)。

数据表:*附件:ADAU1787四个ADC、两个DAC、带音频DSP的低功耗编解码器技术手.pdf

应用

特性

- 可编程的 FastDSP 音频处理器

- 高达 768 kHz 的采样率

- 双二阶滤波器、限制器、音量控制、混频

- 28 位 SigmaDSP 音频处理内核

- 可使用 SigmaStudio 进行可视化编程

- 高达 50 MIPS 性能

- 低延迟 24 位 ADC 和 DAC

- 96 dB SNR(信号通过具有 A 加权滤波器的 PGA 和 ADC)

- 105 dB 综合 SNR(信号通过具有 A 加权滤波器的 DAC 和耳机)

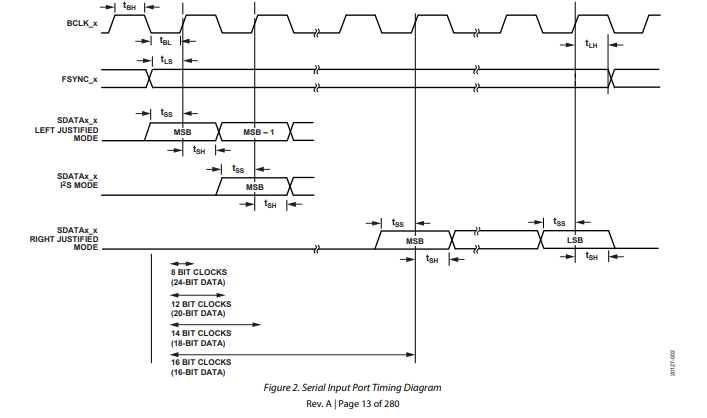

- 串行端口 f

SYNC频率范围为 8 kHz 至 768 kHz - 模拟输入至模拟输出的群延时为 5 μs (f

S= 768 kHz),带 FastDSP 旁路(零指令) - 4 个单端模拟输入,可配置为麦克风或线路输入

- 8 个数字麦克风输入

- 2 个模拟差分音频输出,可配置为线路输出或麦克风驱动器

- 支持 30 kHz 至 27 MHz 范围内任何输入时钟频率的 PLL

- 全双工,4 通道 ASRC

- 2 个 16 通道串行音频端口,支持 I^2^S、左对齐或高达 TDM16

- 8 个内插器和 8 个抽取器,具有灵活路由

- 电源

- 模拟 AVDD 为 1.8 V(典型值)

- 数字 I/O IOVDD 为 1.1 V 至 1.98 V

- 数字 DVDD 为 0.9 V(典型值)

- 低功耗(典型立体声 ANC 设置为 11.079 mW)

- I^2^C 和 SPI 控制接口,从 I^2^C EEPROM 自引导

- 灵活 GPIO

- 42 球 0.35 mm 间距 2.695 mm × 2.320 mm WLCSP

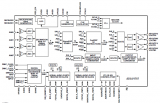

框图

数字时序图

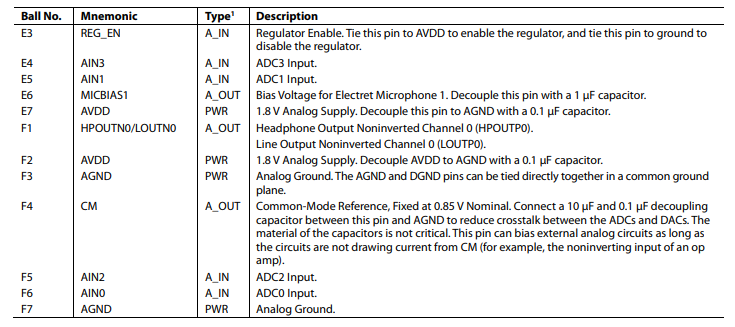

引脚配置描述

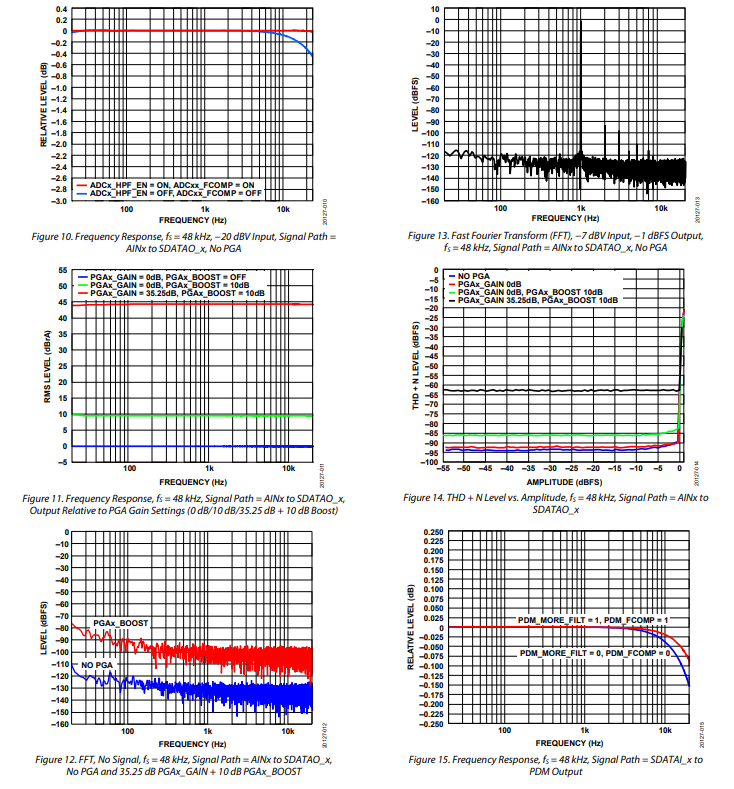

典型性能特征

ADAU1787是一款低功耗音频编解码器,其音频处理内核经过优化,非常适合降噪等对噪声敏感的应用,具备高性能、低功耗、小尺寸和低延迟的特点。四个模数转换器(ADC)通道和两个数模转换器(DAC)通道,每个都具有至少96dB的信噪比(SNR)以及至少88dB的总谐波失真加噪声(THD + N)。支持I²S、左对齐、右对齐和时分复用(TDM)模式,可灵活与数字音频数据进行接口。工作电压为1.8V,板载稳压器可产生数字电源电压。如果不需要,稳压器可以关闭,也可以从外部提供电压。

输入信号路径包含灵活的配置,能够接受单端模拟麦克风输入以及多达八个数字麦克风输入。两个麦克风偏置引脚可实现无缝切换。每个输入信号都有自己的可编程增益放大器(PGA)用于音量调节。

ADC和DAC均为高音质的24位Σ - Δ转换器,工作采样率在12kHz至768kHz之间。ADC和DAC具有可选的高通滤波器,截止频率为1Hz,还有一阶数字软音量控制。

立体声DAC输出能够以差分方式驱动阻抗为16Ω或更高的耳机耳塞扬声器。必要时,也可选择切换为线路输出模式。

SignalDSP内核针对低功耗音频处理进行了优化。该内核由亚德诺半导体的SigmaStudio软件进行图形化编程。利用该软件提供的滤波器、动态处理器、混音器和底层数字信号处理(DSP)功能等音频处理模块库,可快速图形化开发自定义信号流。

FastDSP内核采用精简指令集,优化了该编解码器的降噪功能。程序随机存取存储器(RAM)和参数RAM可通过使用SigmaStudio构建的自定义音频处理信号流进行访问。参数RAM中存储的值控制各个信号处理模块。

ADAU1787还具有自启动功能,可在电源上电时,使用外部电可擦可编程只读存储器(EEPROM),将程序和参数RAM加载到两个内核以及寄存器设置中。

使用SigmaStudio软件对内核进行编程和控制。通过工具端口,可进行设计和测试信号流,还能配置ADAU1787寄存器。SigmaStudio图形用户界面(GUI)使具备数字或模拟音频处理知识的人员,都能为目标应用设计DSP信号流和输出流。该接口还为经验丰富的DSP工程师提供了设计所需的灵活性和可编程性。在SigmaStudio中,用户可以连接图形模块(如双二阶滤波器、音量控制和算术运算),编译设计,并将程序和参数文件加载到ADAU1787的控制端口。SigmaStudio还允许用户下载设计,以进行外部EEPROM自启动操作。

ADAU1787可通过板上可旁路的分数锁相环(PLL),从多种输入时钟生成内部时钟。PLL可接受30kHz至27MHz的输入时钟。对于标准操作,时钟可使用板载晶体振荡器生成。

ADAU1787采用小巧的42引脚、2.695mm×2.320mm晶圆级芯片规模封装(WLCSP)。

-

dsp

+关注

关注

561文章

8276浏览量

368291 -

编解码器

+关注

关注

0文章

291浏览量

25513 -

ADAU1787

+关注

关注

0文章

3浏览量

3564

发布评论请先 登录

ADAU1787具有两个DSP的CODEC音频解决方案

ADAU1701:带两个ADC和四个DAC的SigmaDSP 28/56位音频处理器产品手册

ADAU1401A:带两个ADC和四个DAC的SigmaDSP 28/56位音频处理器产品手册

ADAU1328:带PLL的2个ADC/8个DAC,192 kHz,24位编解码器数据表

UG-807:评估ADAU1372四路ADC、双DAC、低延迟、低功耗编解码器

ADAU1787四个ADC、两个DAC、带音频DSP的低功耗编解码器技术手册

ADAU1787四个ADC、两个DAC、带音频DSP的低功耗编解码器技术手册

评论