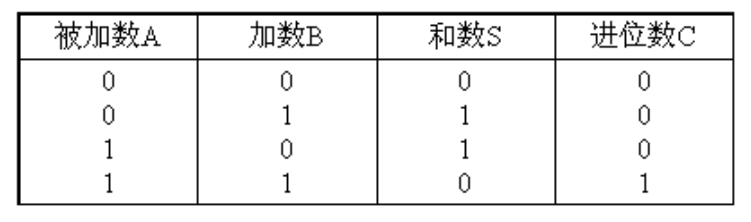

半加器半加器真值表

半加器是实现两个一位二进制数加法运算的电子器件,具有被加数A和加数B两个输入端、输出端Y,经常被应用在算数运算电路中,用于计算两个一位二进制相加,不考虑低位进位。

半加器可以实现两个1位的二进制数字相加,并输出结果和进位。半加器不考虑低位向本位的进位,所以半加器不属于时序逻辑电路,具有两个输入端和两个输出。

半加器的真值表如下:

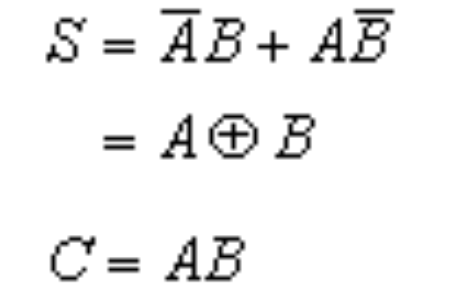

根据真值表可得出:

由此可得出半加器可用一个集成异或门和与门来实现。

半加器与全加器的区别在于半加器没有接收进位的输入端,全加器有进位输入端。

本文整合自百度百科、雅乐网、CSDN

图片来源自电子发烧友

责编AJX

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半加器

+关注

关注

1文章

29浏览量

9141

发布评论请先 登录

相关推荐

热点推荐

LT1160:高效半/全桥N沟道功率MOSFET驱动器的设计与应用

LT1160/LT1162:高效半/全桥N沟道功率MOSFET驱动器的设计与应用 在电子工程师的日常工作中,功率MOSFET驱动器的选择和应用至关重要。今天,我们就来深入探讨一下Linear

ADuM4223:隔离式精密半桥驱动器的卓越之选

ADuM3223/ADuM4223:隔离式精密半桥驱动器的卓越之选 在电子设计领域,半桥驱动器是许多应用中不可或缺的关键组件。今天,我们来深入探讨Analog Devices公司的AD

深度剖析L6599:谐振半桥拓扑的理想控制器

深度剖析L6599:谐振半桥拓扑的理想控制器 在电子工程师的日常工作中,为合适的应用场景挑选恰当的控制器是一项至关重要的工作。对于谐振半桥拓扑而言,L6599是一款被广泛使用的理想控制

UCC27212 半桥驱动器技术详解

UCC27212 半桥驱动器技术详解 在电子工程领域,功率转换和控制电路对于各种应用至关重要。而驱动器作为其中的关键组件,其性能直接影响着整个系统的效率和稳定性。今天,我们就来深入了解一款高性能的

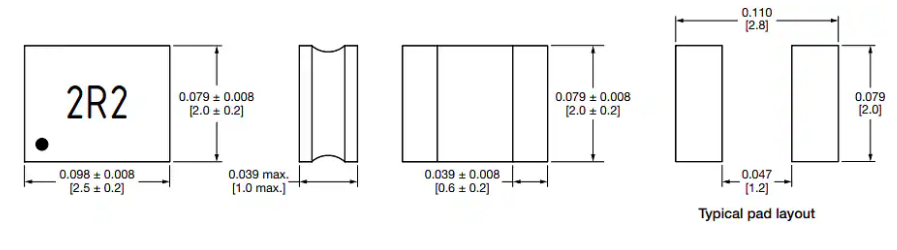

SRN6028C系列半屏蔽功率电感器技术解析

SRN6028C系列半屏蔽功率电感器技术解析 在电子电路设计中,功率电感器是至关重要的元件之一,其性能直接影响着整个电路的稳定性和效率。今天我们就来详细了解一下BOURNS的SRN6028C系列

SRN8040HA系列半屏蔽功率电感器:特性、参数与应用考量

SRN8040HA系列半屏蔽功率电感器:特性、参数与应用考量 在电子工程师的日常工作中,功率电感器是电路设计里的常用元件。今天,我们来深入探讨一下Bourns的SRN8040HA系列半

SRN2010BTA系列半屏蔽功率电感器:特性与应用解析

SRN2010BTA系列半屏蔽功率电感器:特性与应用解析 在电子设备的设计中,功率电感器是不可或缺的元件,它在电源管理、信号处理等方面发挥着重要作用。今天,我们就来详细探讨一下SRN2010BTA

Vishay Dale IFSC-3232DB-01 半屏蔽SMD功率电感器技术解析

Vishay/Dale IFSC-3232DB-01半屏蔽SMD功率电感器采用半屏蔽绕线铁氧体结构,采用SMD封装,外形尺寸为8mm x 8mm x 4.2mm。 这些电感器在0A时的

Vishay Dale IMSC1008AZ半屏蔽SMD功率电感器技术解析与应用指南

Vishay/Dale IMSC1008AZ半屏蔽SMD功率电感器采用薄型封装,最大尺寸为2.5mmx2mmx1mm。这些表面贴装电感器采用半屏蔽、金属基结构,实现稳定的饱和。该系列还

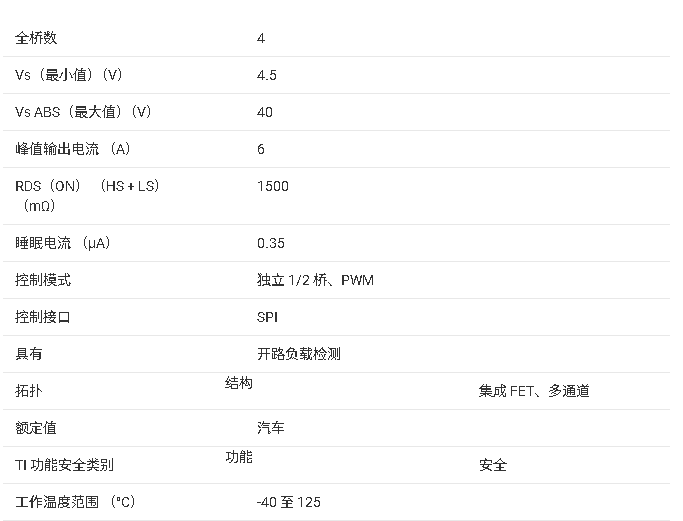

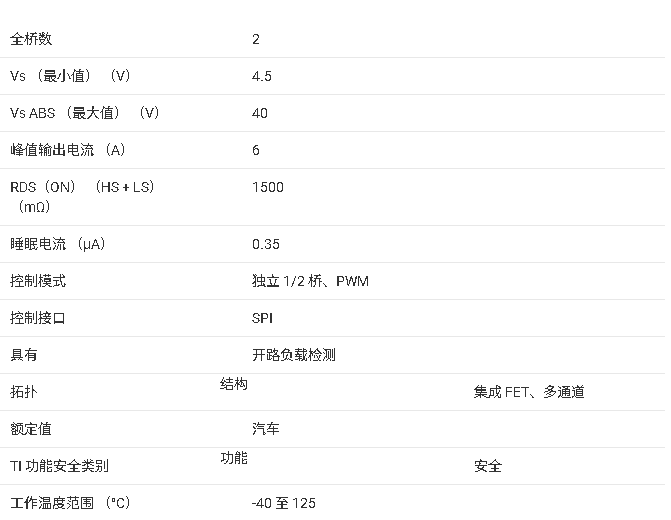

DRV8908-Q1汽车多通道半桥驱动器技术文档总结

DRV89xx-Q1 是引脚兼容的集成多通道半桥驱动器系列,具有 4 至 12 个半桥。该器件系列具有低导通电阻 (R ~DS(开)~ )以提高大电流工作期间的热性能。

这些器件可以以独立

DRV8904-Q1 多通道半桥驱动器技术文档总结

DRV89xx-Q1 是引脚兼容的集成多通道半桥驱动器系列,具有 4 至 12 个半桥。该器件系列具有低导通电阻 (R ~DS(开)~ )以提高大电流工作期间的热性能。

这些器件可以以独立

LM2103 107V半桥驱动器技术解析与应用指南

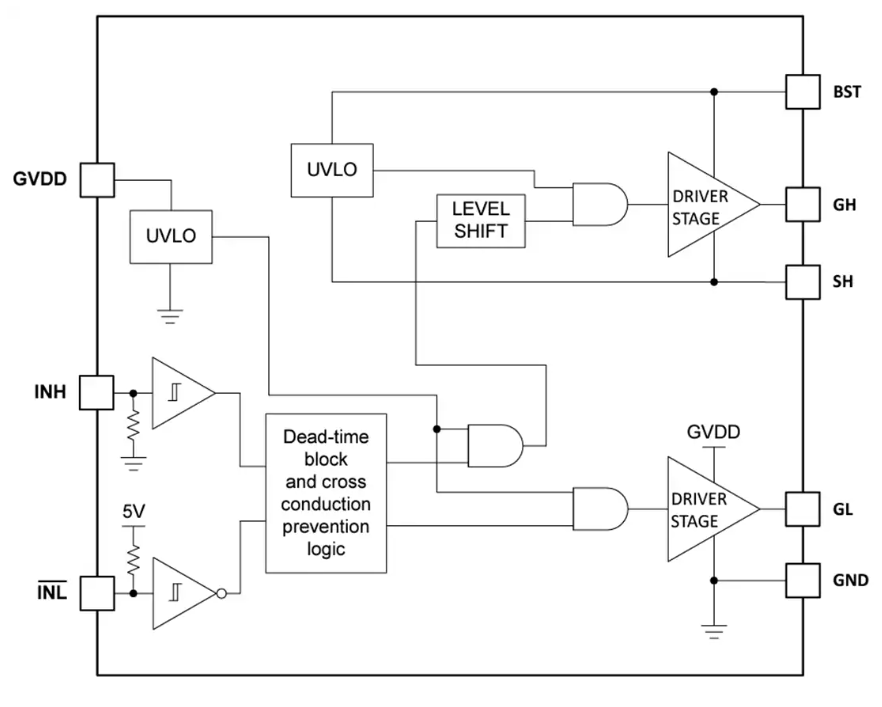

Texas Instruments LM2103半桥驱动器是一款紧凑型高压栅极驱动器,设计用于驱动半桥或同步降压配置中的高侧和低侧N沟道MOSFET。INL反相输入允许驱动器用于双或单

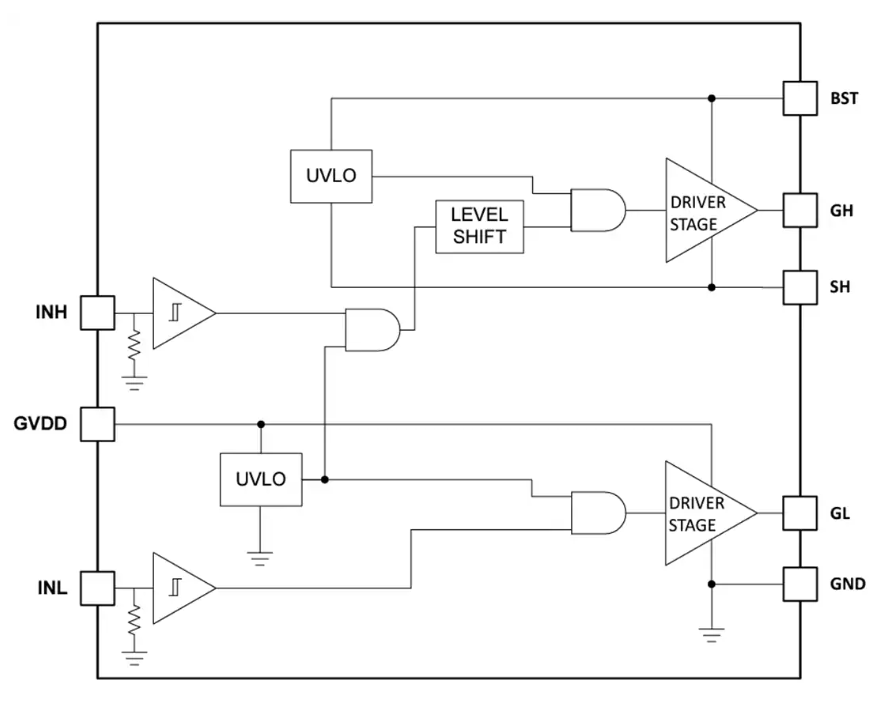

LM2101 107V半桥栅极驱动器技术解析与应用指南

Texas Instrument LM2101半桥栅极驱动器是一款紧凑型高压栅极驱动器,设计用于驱动同步降压或半桥配置中的高侧和低侧N沟道MOSFET。SH 引脚上的 – 1V DC和

半绝缘一次消谐器为啥加一个放电管,起什么作用?

半绝缘一次消谐器加装放电管的主要目的是增强过电压防护能力,确保系统安全稳定运行。放电管可快速响应雷击、操作过电压等瞬态高压,在纳秒级时间内击穿导通,泄放异常能量,避免消谐器核心元件受损。消谐器

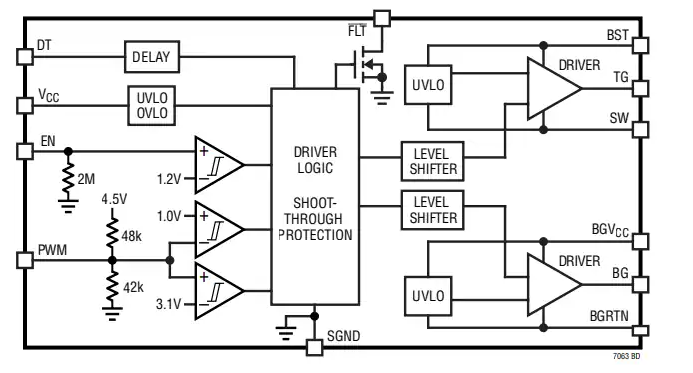

Analog Devices Inc. LTC7063半桥驱动器数据手册

Analog Devices Inc. LTC7063半桥驱动器驱动两个采用半桥配置的N沟道MOSFET,供电电压高达140V。高侧和低侧驱动器可以通过提供瞬态抗扰度和噪声来驱动具

半加器 半加器真值表

半加器 半加器真值表

评论