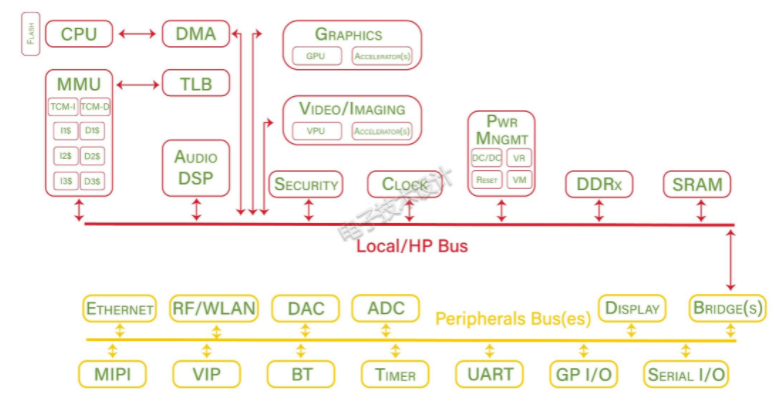

尽管过去十年人们担心摩尔定律最终走到了尽头,但微电子行业通过持续创新和创造力继续适应了新的物理限制和产品要求。这种创造力的主要部分已用于开发模拟、RF和混合信号模块而作为可嵌入的IP(图1)。

图1:此框图突出显示了多媒体SoC设计。(图片来源:P2F Semi)

现在可供选择的模拟/射频/混合信号IP既广泛又深入。人们可以在以下主要类别中找到大量7nm(在某些情况下甚至是5nm)的硬件模块:

-

PLL和DLL:提供各种速度、抖动和功率规格;

-

DAC和ADC:提供8位至24位分辨率,以及高达300MSPS的采样率;

-

PHY和SerDes:针对广泛的市场选择,例如无线(Wi-Fi和5G)、网络(LAN、WAN和外存)、计算(USB、PCIe、MIPI)和内存(DDR,包括G和LP两个版本,以及HBM等);

-

可将较小的元器件组装成个性化的模拟前端(AFE)、电源管理功能和RF模块。

业界已实现源源不断的工艺技术进步,从而对更多门数、更低功耗、更高性能和更多功能等永无止境的需求提供支持。这包括三阱隔离、绝缘硅、P+保护环、FinFET和沟槽隔离。许多这些特性促成了我们今天看到的模拟、RF和混合信号IP的激增。这些衬底的添加还降低了设计人员在超深亚微米领域所面临的一些复杂问题的严重程度——例如隐藏在压摆率中的模拟噪声源、阻抗匹配和端接复杂性,以及支持巨大带宽的电路。

然而,在面对16nm及以下SoC设计中与模拟电路并排放置的大量门数时,即使是新颖的工艺改进也无法实现。事实上,靠近模拟/射频宏的大型高性能数字模块所带来的信号完整性和电源完整性挑战,正从芯片扩展到封装和PCB,两者都在努力跟上硅片技术的进步。SoC设计人员越来越发现他们不得不将其工作范围扩展到这两个其他领域,从而确保其芯片设计能够按预期运行。

这一由多个部分组成的系列文章,探讨了嵌入式模拟和RF IP核如何对芯片、封装和PCB功能产生负面影响——其影响多种多样。我们还将讨论在所有三个层面上可以采取哪些措施来防止这些问题,以及这些解决方案如何相互促进。

硅片实践

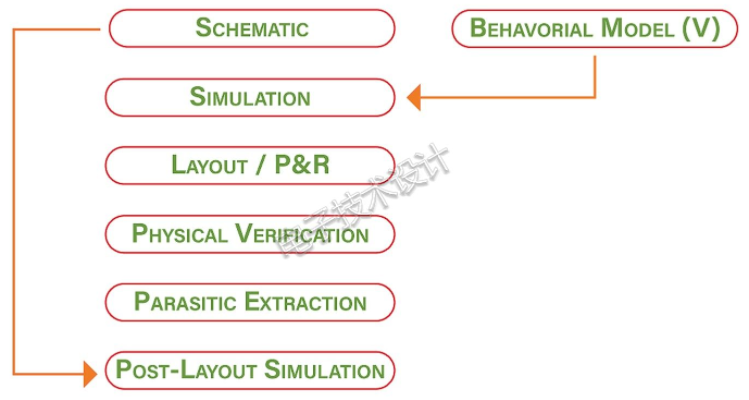

在过去的二十年里,为模拟和数字电路设计创建统一工具和方法流程的尝试,迄今已被证明是徒劳的。然而,模拟流程的基本轮廓却获得普遍同意,如图2所示。

图2:此图显示了基本的模拟设计流程。(图片来源:P2F Semi)

尽管流程可能看起来相当简单,但问题在于细节。

模拟电路对电路的布局和布线方式非常敏感。走线和过孔间距、差分信号和额外地引脚等设计规则,有助于避免或至少减少导致EMI问题的衬底耦合和邻近效应。这就是为什么设计规则检查(DRC)是版图后物理验证工作的一部分。版图与原理图一致性检查(LVS)也是验证预期连接性的相同步骤的一部分。

寄生提取会直接影响潜在耦合源的识别,寄生的反向注释通常会导致原理图和版图发生更改。不幸的是,这会影响时序、动态范围、负载、增益和功率,并产生一组全新的寄生效应。因此,返回到设计流程开始这样的迭代循环是一种悲剧性的必然,这就是为什么模拟设计被认为更像是一门技术而不是一门科学。

模拟模块的集成

因此,将生成的模拟模块集成到整个ASIC/SoC设计中会带来一系列全新的问题。对于数字和模拟两种电路模块,芯片布局规划都将受到每个模块的最佳位置、引脚布局、I/O位置、关键路径、电源和信号分布,以及芯片尺寸及其纵横比的约束。模拟IP对这些问题中的大多数都特别敏感,而模拟模块也是硬MAC,这就使上述所有问题变得复杂。

一旦放置了芯片模块,无论是模拟还是数字,最佳布线实践都包括首先实现所有关键路径。但是,当涉及非关键路径时,模拟信号应优先。此外,无论给定的模拟信号是否重要,所有模拟布线都需要在匹配寄生、最小化耦合效应和避免过度的IR压降方面进行特殊考虑。这是通过对模拟信号布线采用各种屏蔽技术、保持走线短、通过最直接的路线设置返回信号路径,以及使用差分信号等来实现的。

除了上述在片上集成模拟内容的广泛方法之外,不同类别的模拟电路也可能需要特别注意。DAC和ADC就是一个很好的例子。

使用DAC或ADC时,除了其分辨率和采样率外,还需要考虑其他一些设计注意事项,即其指定的信噪比(SNR)、有效位数(ENOB)额定值和功耗。遵循奈奎斯特采样定理(该定理指出,使模拟信号获得充分数字再现,需要以2倍以上的模拟fmax进行采样)可能本身会给非常高性能的应用带来带宽、功率和位同步上的挑战。

从采样的角度来看,无线尤其成问题,而音频则通常对分辨率的要求最高。这就是ENOB等参数具有特别意义的地方。无论给定DAC或ADC所标榜的分辨率是多少,迫使此类模块超过其ENOB都会使其SNR性能下降,并有可能对模块的真正实用性产生重大影响。

最重要的是,将模拟模块设计和集成到SoC或ASIC的环境中,根本不会像芯片的数字部分那样“干净”并且其工程工作可预测。经验、灵活性和适应性是成功的决定性因素。

传统上,芯片设计团队认为,在将数字和模拟/RF/混合信号模块正确集成到SoC设计中所需关心的事情不外乎这些。但正如我们将在本系列即将发布的文章中所说明的那样,情况不再如此。SoC设计工作的规模正在不断扩大,因此设计团队需要大幅提高其技能和实践才能在这个变革时期生存下来。

文章来源:ednchina Kedar Patankar

编辑:ymf

-

芯片

+关注

关注

462文章

53574浏览量

459413 -

pcb

+关注

关注

4391文章

23746浏览量

420909 -

封装

+关注

关注

128文章

9149浏览量

147917

发布评论请先 登录

DIY 流体模拟吊坠(二):第二个、第三个、更多的吊坠......

PCB中的数字地和模拟地

【「芯片通识课:一本书读懂芯片技术」阅读体验】芯片如何设计

高密度互连:BGA封装中的PCB设计要点

Linux系统中最重要的三个命令

ADS828的GND引脚有三个,这三个引脚的接地是哪个接数字地,哪个接模拟地?

选择ADS1253 ADC芯片时,产生了三个疑问,求解答

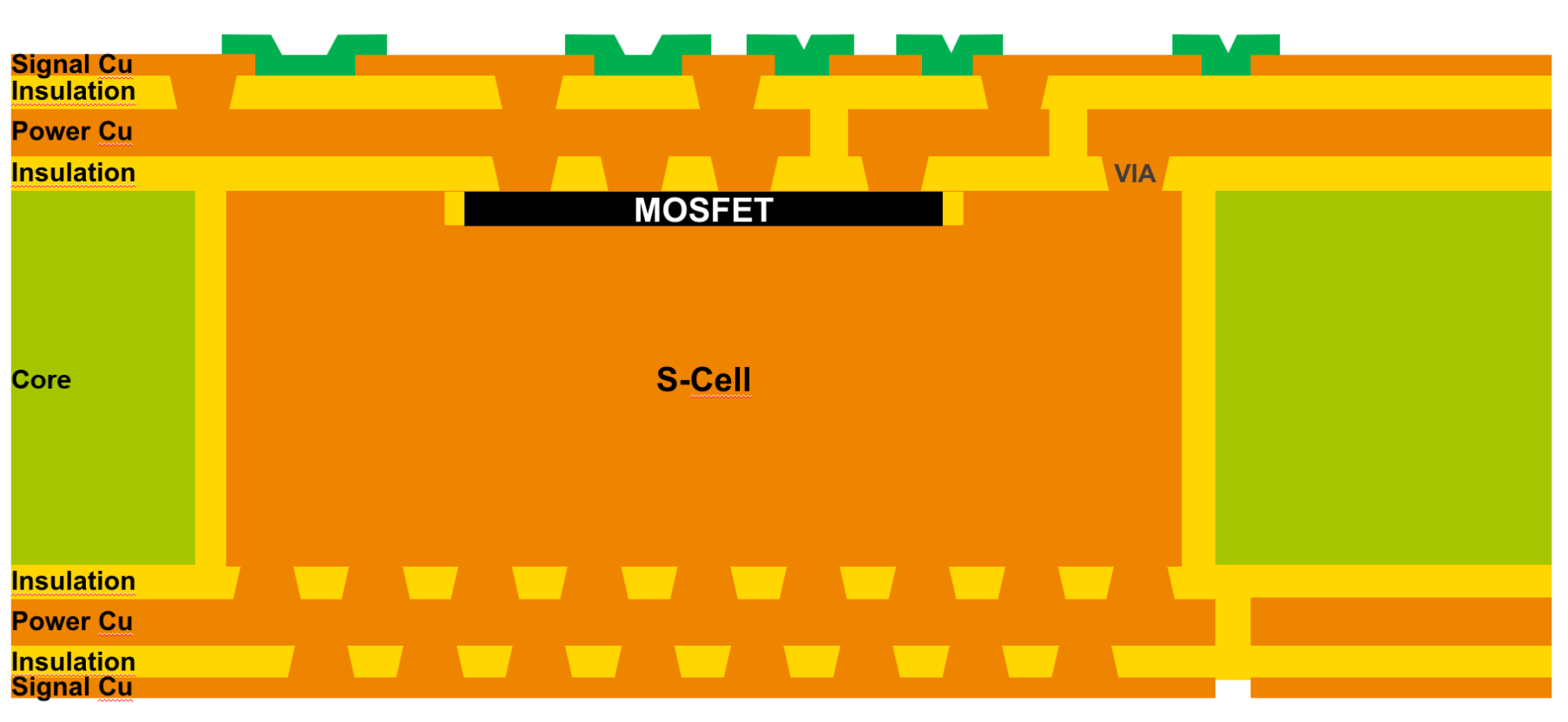

PCB嵌入式功率芯片封装,从48V到1200V

浅谈瑞盟科技·MS8313——三个半 H 桥驱动器集成电路

从芯片、封装和PCB三个层面了解模拟IP集成中的各种问题

从芯片、封装和PCB三个层面了解模拟IP集成中的各种问题

评论