1开发NVME Host IP难在哪?

这里强调的是做商用IP,而不是只是以功能或性能验证为目的。

它主要由以下两大因素困扰:

1)协议复杂性:NVMe协议相对复杂,过程调试不尽如意。

2)开发周期长:即使有xilinx开发板,但是采用开发板上机调试,首先是编译时间长,增加调试时间;其次是不清楚如何排查问题,种种原因导致目前开发NVMe IP成为难点。

2 基于UVM的Xilinx PCIE4 NVMe IP开发工具

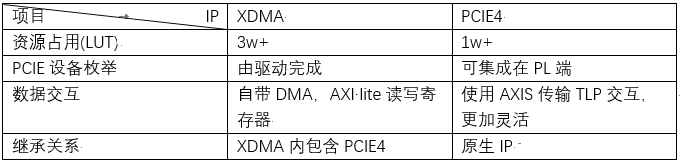

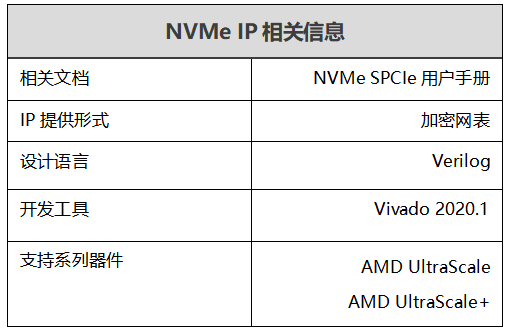

目前应用NVMe IP主流器件大都采用xilinx的ultrascale或ultrascale+系列,如V,K和Zynq系列。虽然PC端已经支持PCIe5,但是FPGA端还停留在PCIe3.0或PCIe4.0.而PCIE4提供向下兼容,故推出配套的UVM验证工具选用支持PCIe4系列是符合目前开发需求。

3什么是Xilinx PCIE4

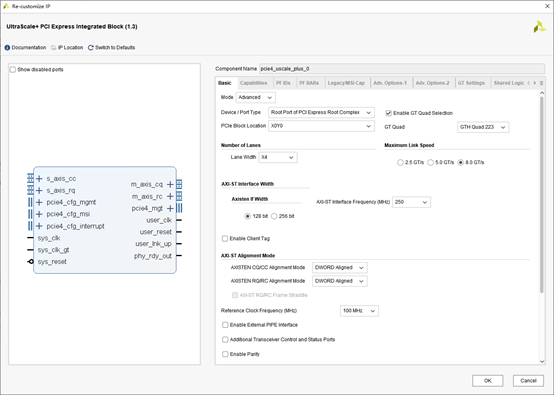

Xilinx PCIE4是Xilinx公司开发的AMD UltraScale+™ 设备集成块,全程为AMD UltraScale+™ Devices Integrated Block for PCI Express® (PCIe®) solution IP core, 此IP是一种高带宽、可扩展且可靠的串行互连构建模块,适用于 UltraScale+ 设备。AMD 在 UltraScale+ 架构中提供了两种 PCIe 集成块:PCIE4 集成块和 PCIE4C 集成块。PCIE4 块是 UltraScale+ 设备中使用的,支持 PCIe IP。配备高带宽存储器 (HBM) 的 AMD Virtex™ UltraScale+™ 设备包含 PCIE4 块和增强型 PCIE4C 块的混合配置。

PCIE4 块支持 1-lane、2-lane、4-lane、8-lane 和 16-lane 配置,包括 Gen1 (2.5 GT/s)、Gen2 (5.0 GT/s) 和 Gen3 (8 GT/s) 的速度,符合 PCI Express 基本规范 3.1 版。PCIE4C 块在功能上等同于 PCIE4 块,并且额外支持 Gen4 (16 GT/s) 的速度,支持 1-lane、2-lane、4-lane 和 8-lane 配置,符合 PCI Express 基本规范 4.0 版。该解决方案支持 AXI4-Stream 接口作为用户接口。

PCIe调用示意图

4 为什么么要在PCIE4上开发NVMe IP

1. 高带宽和高性能

支持 Gen1 (2.5 GT/s)、Gen2 (5.0 GT/s)、Gen3 (8 GT/s) 和 Gen4 (16 GT/s) 的不同速率。

可以根据实际需求选择不同的带宽和速率,满足不同应用对性能的要求。

2. 灵活的配置选项

提供 1-lane、2-lane、4-lane、8-lane 和 16-lane 配置选项,可以根据需要进行扩展,提供灵活的设计空间。

支持多种配置选项,可以根据系统的需求来平衡带宽和硬件资源。

3. 兼容性和标准化

PCIe 4.0 版本(PCIE4C块)支持 16 GT/s 速度,并与 PCI Express Base Specification, Revision 4.0 兼容。这样可以确保设备在未来的系统中保持兼容性,支持最新的高速传输标准。

PCIe 3.1 版本(PCIE4块)与 PCI Express Base Specification, Revision 3.1 兼容,确保它与现有设备和平台的兼容性。

4. 扩展性和可定制性

提供多个数据通道配置,支持 AXI4-Stream 接口,使得设计者可以根据具体应用需求灵活调整系统架构,进行扩展。

支持与多个设备之间的高效通信,增强了数据传输的灵活性和可定制性。

5. 为何需要基于UVM 的NVMe IP开发工具

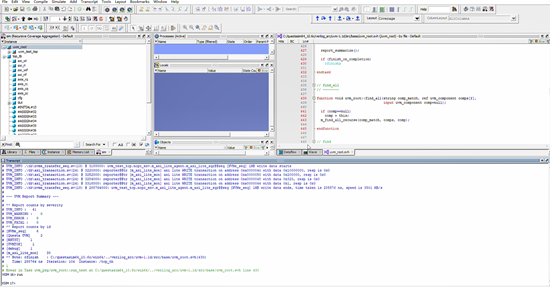

作为NVMe IP开发者,在构建IP时总是需要不断修改,然后编译上板测试,每一次编译,少则20分钟,多则两三个小时,对IP的热情总是在满怀期待的希望等待中磨灭,NVMe IP开发工具作为一个仿真验证环境,有以下特点

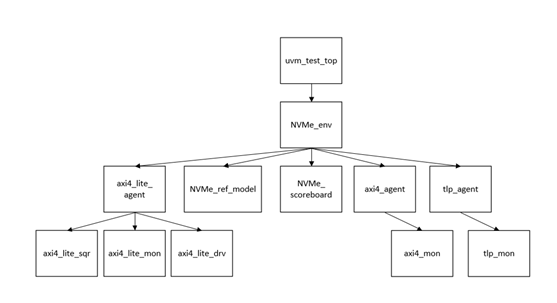

1)基于UVM验证环境,对熟悉UVM的伙伴非常友好,便于后续特定测试用例的编写与修改

架构图

2) 提供完整的NVMe测试用例,包括PCIE初始化,枚举,NVME初始化,NVMe读写事务一目了然。

3) 提供基于三星980pro编写的Refence Model,可模拟全场景下的NVMe设备行为。极大提高上板成功概率,在上板前解决各种疑难问题

4) 极大缩短验证所需的时间,根据传输的数据量不同,在1-5分钟即可完成波形仿真。

5) 可做仿真极限压力测试,经测试,在128位AXIS,时钟频率250MHz下,NVMe读写峰值可达到3500 MB/s

感兴趣的可以看B站视频:

https://www.bilibili.com/video/BV1SnzGYsEh8/?spm_id_from=333.337.search-card.all.click&vd_source=c355545d27a44fe96188b7caefeda6e7

或者B站搜用户名: 专注与守望 上面有更多相关视频

或CSDN: https://mp.csdn.net/mp_blog/manage/article?spm=1011.2124.3001.5298

审核编辑 黄宇

-

FPGA

+关注

关注

1655文章

22288浏览量

630340 -

IP

+关注

关注

5文章

1849浏览量

154929 -

nvme

+关注

关注

0文章

287浏览量

23721

发布评论请先 登录

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

资本狂潮涌向XR:10家企业3个月狂吸金,最高拿下6亿巨资

NVMe IP高速传输却不依赖XDMA设计之三:系统架构

NVMe IP高速传输却不依赖便利的XDMA设计之三:系统架构

NVMe协议研究扫盲

NVMe IP之AXI4总线分析

充电桩出海,缩短三个月项目周期,竟是因为它?

NVMe IP开发速成: 三个月不是梦

NVMe IP开发速成: 三个月不是梦

评论