作为Xilinx 7nm芯片,Versal在架构上与前一代芯片UltraScale相比有诸多不同,这里我们就来看看都有哪些不同。

时钟资源

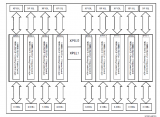

从时钟Buffer角度看,多了一种BUFG_FABRIC,专门用于驱动高扇出网线,从而降低了BUFG的利用率,缓解了布线资源的压力,其在芯片中的位置如图中红色标记所示。

可配置逻辑模块

再看CLB,Versal中一个CLB规模相当于UltraScale中的两个CLB,故其包含16个触发器和64个LUT。同时,这64个LUT中有32个LUT可配置为RAM/ROM/或移位寄存器。这意味着,Versal中的CLB不再有CLB_LL和CLB_LM之分。此外,CLB内部列方向相邻的LUT是可级联的,这对于缓解CLB外部的布线压力是有益的。

CLB内部还增加了Inverse Multipliexer Register (Imux Register),用于改善Fmax、解决保持时间违例。另一方面,CLB内部不再包含F7/8/9MUX,改由LUT实现相应的功能。

DSP58

Versal中的乘法器为DSP58,可支持27x24有符号数乘法,与UltraScale中的27x18相比有所提升。同时,就复数乘法而言,对于18-bit复数,只需要消耗2个DSP58。在UltraScale中,则要消耗3个DSP48。DSP58的另一亮点是可支持向量乘,也就是说27x24的乘法器可分解为3个9x8的乘法器,从而可方便地实现两个长度为3的向量乘法,这对于快速实现矩阵乘法是很有利的。此外,DSP58还支持浮点乘法和浮点加法。DSP48则需要额外的资源实现浮点运算。

URAM288

在UltraScale中,URAM288可支持的位宽是固定的72位,且初始值只能为0。但在Versal中,URAM288可支持4中位宽,分别为9/18/36/72,同时,初始值是用户可定义的。

Block RAM

在UltraScale中,一个RAMB36可配置的位宽为1/2/4/9/18/36/72,但在Versal中,1/2/4这些位宽不再支持。

复位

从复位角度看,Versal中的BRAM和DSP内部寄存器既支持同步复位又支持异步复位,而UltraScale中的BRAM和DSP仅支持同步复位。

编辑:jq

-

dsp

+关注

关注

561文章

8271浏览量

368196 -

驱动

+关注

关注

12文章

1990浏览量

88696 -

Xilinx

+关注

关注

73文章

2205浏览量

131848 -

7nm芯片

+关注

关注

0文章

24浏览量

7373

原文标题:与UltraScale相比,Versal有哪些不同?

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

探索AMD XILINX Versal Prime Series VMK180评估套件,开启硬件创新之旅

AMD UltraScale架构:高性能FPGA与SoC的技术剖析

AMD Versal自适应SoC内置自校准的工作原理

AMD Vivado IP integrator的基本功能特性

AMD 7nm Versal系列器件NoC的使用及注意事项

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

一文详解Advanced IO wizard异步模式

AMD Power Design Manager 2025.1现已推出

基于AMD Versal器件实现PCIe5 DMA功能

AMD Vivado Design Suite 2025.1现已推出

AMD第二代Versal AI Edge和Versal Prime系列加速量产 为嵌入式系统实现单芯片智能

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

第二代AMD Versal Premium系列SoC满足各种CXL应用需求

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

UltraScale和Versal之间有哪些不同?

UltraScale和Versal之间有哪些不同?

评论