一。 Sobel简介

一句话可以概况为,分别求水平与竖直梯度,然后求平方和再开方(近似的话就直接求绝对值之和),最后与设定的阈值进行比较,大于的话就赋值为0,小于的话就赋值为255

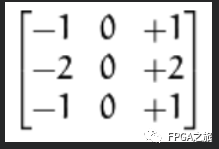

x方向梯度dx的求法:3*3的图像矩阵与下面的矩阵在对应位置相乘然后相加

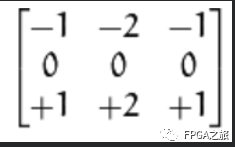

y方向梯度dy的求法:同上

二。 代码实现

这里采用近似计算G = |dx| + |dy|,正负号分开计算,然后用大的数减去小的数

reg[10:0] Sobel_px ,Sobel_nx;reg[10:0] Sobel_py ,Sobel_ny;

wire[10:0] Sobel_x;wire[10:0] Sobel_y;

wire[7:0] Sobel_data;

//x方向的梯度assign Sobel_x = (Sobel_px 》 Sobel_nx) ? (Sobel_px - Sobel_nx) : (Sobel_nx - Sobel_px);//y方向的梯度assign Sobel_y = (Sobel_py 》 Sobel_ny) ? (Sobel_py - Sobel_ny) : (Sobel_ny - Sobel_py);assign Sobel_data = (Sobel_x + Sobel_y 》 ‘d135) ? ’d0 : ‘d255;

always@(posedge clk_9M or negedge rst)begin if(rst == 1’b0) begin Sobel_px 《= ‘d0; Sobel_nx 《= ’d0; end else if(cur_x 》= ‘d100 && cur_x 《= ’d199 && cur_y 》= ‘d50) begin Sobel_nx 《= data_line_11 + data_line_21 + data_line_21 + data_line_31; Sobel_px 《= data_line_13 + data_line_23 + data_line_23 + data_line_33; end else begin Sobel_nx 《= ’d0; Sobel_px 《= ‘d0; endend

always@(posedge clk_9M or negedge rst)begin if(rst == 1’b0) begin Sobel_py 《= ‘d0; Sobel_ny 《= ’d0; end else if(cur_x 》= ‘d100 && cur_x 《= ’d199 && cur_y 》= ‘d50) begin Sobel_py 《= data_line_11 + data_line_12 + data_line_12 + data_line_13; Sobel_ny 《= data_line_31 + data_line_32 + data_line_32+ data_line_33; end else begin Sobel_ny 《= ’d0; Sobel_py 《= ‘d0; endend

编辑:lyn

-

FPGA

+关注

关注

1664文章

22502浏览量

639139 -

sobel

+关注

关注

0文章

12浏览量

8235

原文标题:FPGA实现Sobel边缘检测

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera Agilex FPGA与SoC实现更智能的AI

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

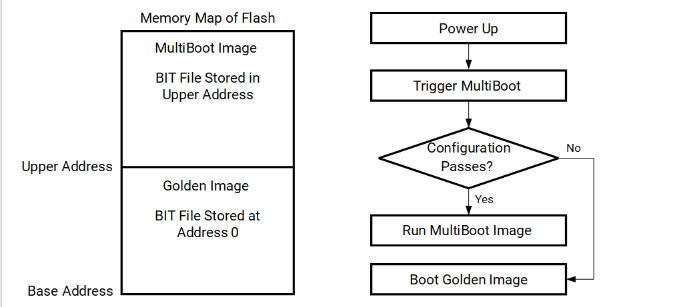

【ALINX 教程】FPGA Multiboot 功能实现——基于 ALINX Artix US+ AXAU25 开发板

如何使用FPGA实现SRIO通信协议

基于FPGA的肤色检测方案简介

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

AI狂飙, FPGA会掉队吗? (中)

FPGA利用DMA IP核实现ADC数据采集

基于Matlab与FPGA的双边滤波算法实现

基于FPGA的压缩算法加速实现

开源FPGA硬件,核心开发者招募中......

关于FPGA中Sobel的简介与实现

关于FPGA中Sobel的简介与实现

评论