1).在走线的Via孔附近加接地Via孔的作用及原理是什么?

=====================================

pcb板的过孔,按其作用分类,可以分为以下几种:

1、信号过孔 (过孔结构要求对信号影响最小)

2、电源、地过孔 (过孔结构要求过孔的分布电感最小)

3、散热过孔 (过孔结构要求过孔的热阻最小)

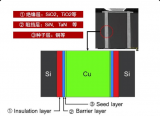

上面所说的过孔属于接地类型的过孔,在走线的Via孔附近加接地Via孔的作用是给信号提供一个最短的回流路径。注意:信号在换层的过孔,就是一个阻抗的不连续点,信号的回流路径将从这里断开,为了减小信号的回流路径所包围的面积,必须在信号过孔的周围打一些地过孔提供最短的信号回流路径,减小信号的 EMI辐射。这种辐射随之信号频率的提高而明显增加。

2).请问在哪些情况下应该多打地孔?有一种说法:多打地孔,会破坏地层的连续和完整。效果反而适得其反

=====================================

首先,如果多打过孔,造成了电源层、地层的连续和完整,这种情况使用坚决避免的。这些过孔将影响到电源完整性,从而导致信号完整性问题,危害很大。打地孔,通常发生在如下的三种情况:

1、打地孔用于散热;

2、打地孔用于连接多层板的地层;

3、打地孔用于高速信号的换层的过孔的位置;

3).但所有的这些情况,应该是在保证电源完整性的情况下进行的。那就是说,只要控制好地孔的间隔,多打地孔是允许的吗?在五分之一的波长为间隔打地孔没有问题吗?

假如我为了保证多层板的地的连接,多打地孔,虽然没有隔断,那会不会影响地层和电源层的完整呢?

=====================================

如果电源层和地层的铜皮没有被隔断影响是不大的。在目前的电子产品中,一般EMI的测试范围最高为1Ghz。那么1Ghz信号的波长为30cm,1Ghz 信号1/4 波长为7.5cm=2952mil。也即过孔的间隔如果能够小于2952mil 的间隔打,就可以很好的满足地层的连接,起到良好的屏蔽作用。一般我们推荐每1000mil打地过孔就足够了。

责任编辑:lq

-

阻抗

+关注

关注

17文章

993浏览量

49499 -

信号

+关注

关注

12文章

2930浏览量

80405 -

Via

+关注

关注

0文章

44浏览量

19754

原文标题:过孔的作用和原理问答

文章出处:【微信号:pcbgood,微信公众号:奈因PCB电路板设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB设计避坑指南——孔/槽篇

端子观察孔有什么作用?

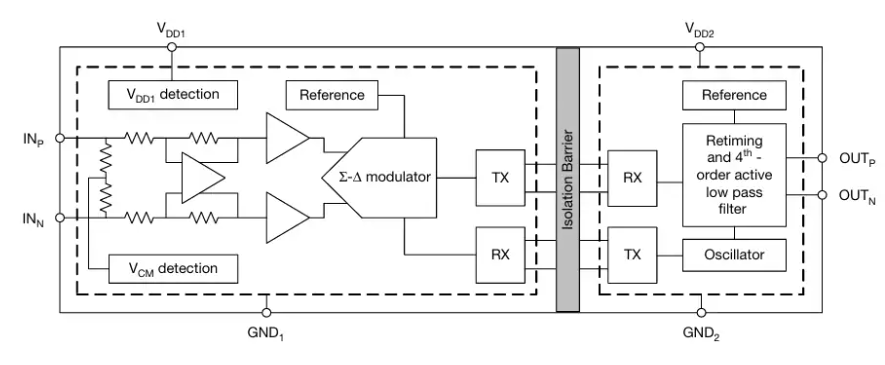

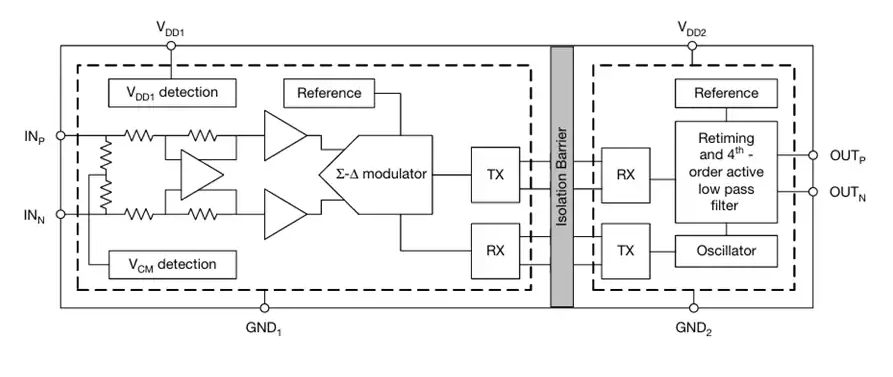

高性能隔离放大器技术解析:Vishay VIA0050DD在电流检测中的应用

Vishay VIA0250DD隔离放大器技术解析与应用指南

技术资讯 I Allegro 设计中的走线约束设计

多层PCB盲孔与埋孔工艺详解

PCB板中塞孔和埋孔的区别

高密PCB设计秘籍:BB Via制作流程全解析

在走线的Via孔附近加接地Via孔的作用及原理是什么?

在走线的Via孔附近加接地Via孔的作用及原理是什么?

评论