近日有消息称,苹果已着手进行新一代A15系列处理器开发,预期会采用台积电5nm加强版N5P制程,明年第三季开始投片。

据传苹果将在A15芯片中使用台积电的5纳米技术

晶圆代工龙头台积电及微影设备大厂ASML于上周法人说明会透露了更多3纳米细节,台积电3纳米采用鳍式场效电晶体FinFET架构及极紫外光EUV微影技术,逻辑密度与5纳米相较将大幅增加70%,且EUV光罩层数将倍增且超过20层。

为此,台积电积极采购EUV曝光机设备,未来三到五年仍将是拥有全球最大EUV产能的半导体厂,包括家登及崇越等供应商可望受惠。

台积电EUV微影技术已进入量产且制程涵盖7+纳米、6纳米、5纳米,据设备业者消息,台积电7+纳米采用EUV光罩层最多达四层,超微新一代 Zen 3 架构处理器预期是采用该制程量产。

6纳米已在第四季进入量产,EUV光罩层数较7+纳米增加一层,包括联发科、辉达、英特尔等大厂都将采用6纳米生产新一代产品。

台积电下半年开始量产5纳米制程,主要为苹果量产A14及A14X处理器,包括超微、高通、辉达、英特尔、博通、迈威尔等都会在明年之后导入5纳米制程量产新一代产品。

5纳米EUV光罩层数最多可达14层,所以Fab 18厂第一期至第三期已建置庞大EUV曝光机台设备因应强劲需求,台积电明年将推出5纳米加强版N5P制程并导入量产,后年将推出5纳米优化后的4纳米制程,设备业者预期N5P及4纳米的EUV光罩层数会较5纳米增加。

台积电在日前的法说会中宣布,3纳米研发进度符合预期且会是另一个重大制程节点,与5纳米制程相较,3纳米的逻辑密度可增加70%,在同一功耗下可提升15%的运算效能,在同一运算效能下可减少30%功耗。

3纳米制程采用的EUV光罩层数首度突破20层,业界预估最多可达24层。

ASML执行长Peter Wennink在日前法说会中指出,5纳米逻辑制程采用的EUV光罩层数将超过10层,3纳米制程采用的EUV光罩层数会超过20层,随着制程微缩EUV光罩层数会明显增加,并取代深紫外光DUV多重曝光制程。

台积电5纳米及3纳米的EUV光罩层数倍数增加,提供EUV光罩盒EUV Pod的家登受惠最大,今、明两年产能均已被大客户预订一空。

至于EUV产能大幅提高,代理EUV光阻液的崇越接单畅旺,订单同样排到明年下半年。

责任编辑:tzh

-

处理器

+关注

关注

68文章

20332浏览量

254980 -

芯片

+关注

关注

463文章

54425浏览量

469325 -

半导体

+关注

关注

339文章

31238浏览量

266562 -

晶圆

+关注

关注

53文章

5449浏览量

132759

发布评论请先 登录

LT1580/LT1580 - 2.5:新一代微处理器的理想电源解决方案

LT1581/LT1581 - 2.5:新一代微处理器的理想低 dropout 稳压器

马斯克宣布: A15完成设计,未来芯片迭代快过AMD和英伟达

Cortex-M0 处理器介绍

【内测活动同步开启】这么小?这么强?新一代大模型MCP开发板来啦!

广芯微推出新一代2x520W并网型微型逆变器参考开发平台

龙芯发布国产自研新一代处理器 龙芯中科新一代处理器3C6000/2K3000/3B6000M芯片面世 瞄准服务器和AI处理器

芯来科技新一代RISC-V高性能处理器IP UX1030H 全面支持RVA23

米尔NXP i.MX 91核心板发布,助力新一代入门级Linux应用开发

nRF54系列新一代无线 SoC

Nordic新一代旗舰芯片nRF54H20深度解析

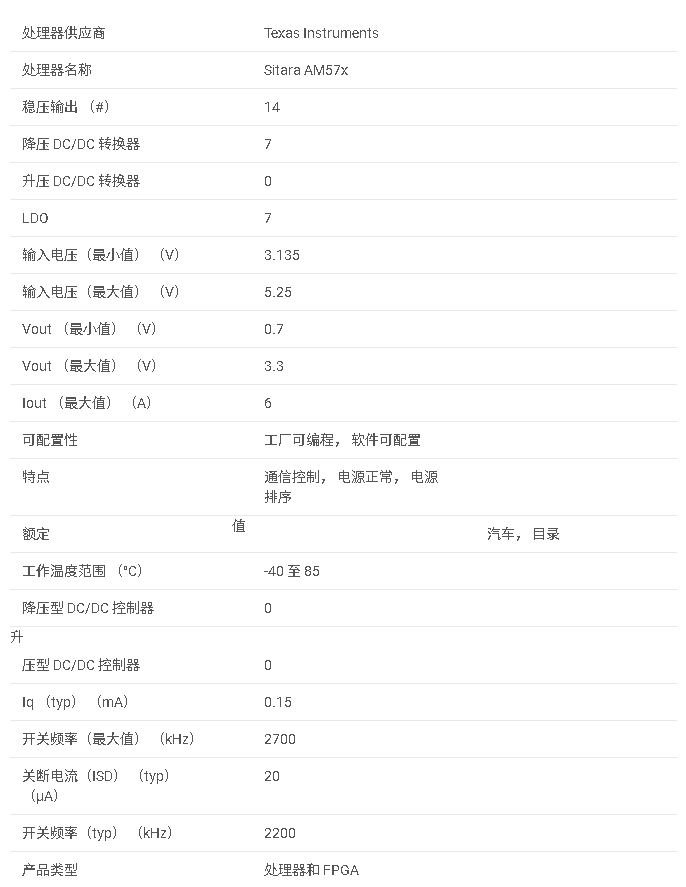

TPS659037 用于 ARM Cortex A15 处理器的电源管理 IC (PMIC)数据手册

苹果已着手进行新一代A15系列处理器开发

苹果已着手进行新一代A15系列处理器开发

评论