作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

不同使用场景,对芯片的性能和功耗要求不一样。为了测试Xilinx MPSoC PS侧的最低功耗,基于ZCU106单板做了功耗优化。为了方便,使用最简单的软硬件环境。软件使用死循环做串口打印,硬件保留了如下模块。

A. A53 0

B. QSPI flash Dual Parallel

C. I2C 0/1

D. PMU

E. UART 0

F. GPIO MIO

G. SWDT 0/1

H. TTC 0/1/2/3

I. DDR 16-bit

J. DPLL/RPLL

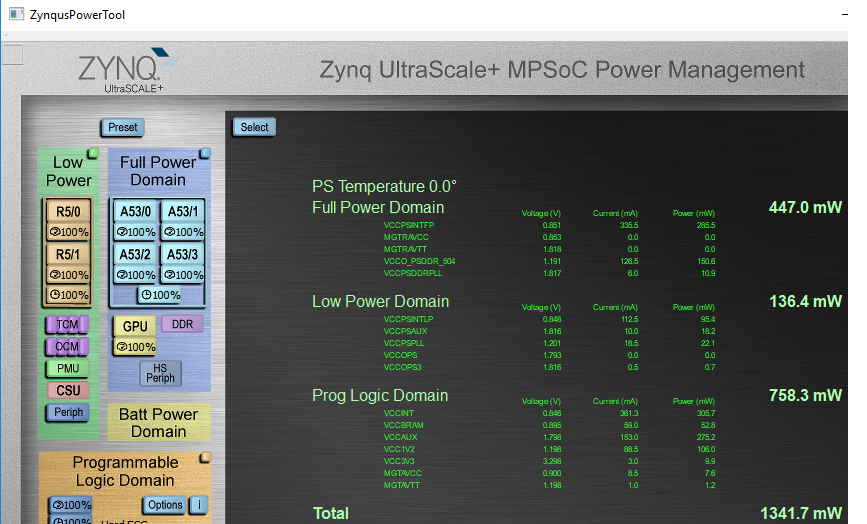

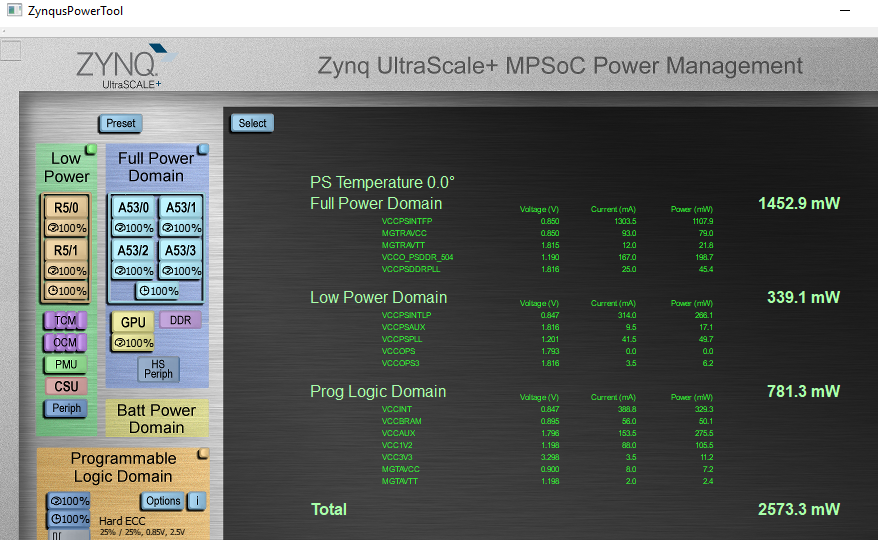

在关闭其他外设,尽可能降低各个模块的频率后,FPD功耗是447mw,LPD是136mw。作为对比,Vivado使用ZCU106单板建立工程,使用默认设置,FPD功耗是1452mw,LPD是339mw。可以看到,新设计节省了相当大的功耗。当然,具体的产品使用场景,可能有性能和功能要求。能达到什么效果,还需要根据产品要求再做评估。

优化后的功耗

优化前的功耗

责任编辑:xj

原文标题:【资深工程师分享】ZCU106 MPSoC 功耗优化

文章出处:【微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

-

Xilinx

+关注

关注

73文章

2208浏览量

131960 -

单板

+关注

关注

0文章

34浏览量

11204 -

MPSoC

+关注

关注

0文章

203浏览量

25231

原文标题:【资深工程师分享】ZCU106 MPSoC 功耗优化

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

从翻转率入手优化FPGA功耗

ZCU重磅登场!ST携手利尔达定义汽车电子区域控制新标杆

ZCU一体化测试解决方案

PCBA单板工艺概述

基于AMD FPGA的HDMI2.1接口实现

请问如何优化芯片的功耗管理?

MCU时钟管理对功耗优化方向

NVMe高速传输之摆脱XDMA设计45:上板资源占用率分析

NVMe高速传输之摆脱XDMA设计44:工程设计考量?

NVMe高速传输之摆脱XDMA设计43:如何上板验证?

MDD 逻辑IC的功耗管理与优化策略

Microchip SHA106加密认证芯片技术解析与应用指南

基于ZCU106单板的功耗优化

基于ZCU106单板的功耗优化

评论