当我们启动Flex Logix时,eFPGA面临的挑战是有许多客户和应用程序,他们似乎都希望eFPGA位于不同的代工厂,不同的节点和不同的阵列大小。每个人都希望eFPGA与在同一节点上的FPGA领导者一样快且密度高。哦,客户似乎要等到最后一刻,才需要尽快使用eFPGA。

Xilinx和Altera(现在为Intel PSG)需要大约3年的时间,需要数十或数百个人才能在新的工艺节点中推出新的FPGA系列。Flex Logix如何以更少的团队开发不到一年的速度和密度的eFPGA?

革命性的FPGA互连

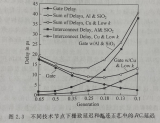

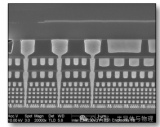

Flex Logix联合创始人兼高级副总裁程望(Cheng Wang)在加州大学洛杉矶分校(UCLA)攻读博士学位期间设计了多个复杂度不断提高的FPGA芯片。在此过程中,他意识到FPGA中使用的传统网状互连占据了80%的面积:可编程逻辑仅占20%。因此,他发明了一种新型互连,该互连与网状结构一样好,但可以使用一半的晶体管和一半的金属层来实现!

Cheng,UCLA的Dejan Markovic教授和其他人在ISSCC上发表了有关在他们最终的FPGA项目中使用的这种新互连的论文,并获得了享有盛誉的杰出论文奖。今天,其中四分之三与Flex Logix有关。

UCLA在互连上申请了专利:Flex Logix是唯一的被许可人。自创立Flex Logix以来,Cheng对互连进行了大量改进,Flex Logix专利涵盖了这些互连。Flex Logix现在拥有20多项美国已发布专利,这是我们在中国的第一项专利。

我们如何使用专利互连来设计eFPGA

FPGA公司拥有非常庞大的设计团队,并且需要花费数年的时间,因为他们进行的是全定制设计,这通常保留给包括微处理器在内的超大批量产品使用。

跨多个代工厂和数十个节点需要eFPGA。如果我们每个版本必须雇用50多人,那么eFPGA永远不会变得经济或及时可用。

如今,大多数ASIC设计都是使用标准单元完成的:铸造厂通常免费提供简单的构建块,并且已经在工艺,电压和温度范围内进行了表征。可以按照逻辑设计规则组装标准单元设计,并保证其能正常工作。

但是标准单元设计通常是优化的全定制设计面积的2倍。

FPGA是80%的互连,而Cheng的互连需要½个晶体管。因此,与其使我们的eFPGA变小,不如让我们的eFPGA全部来自标准单元:使用标准单元增加2倍的面积可以抵消Cheng互连的面积减少50%的影响。因此,在给定的过程节点中,我们最终得到与FPGA领导者相同的密度和性能。

但是,因为我们使用标准单元进行设计,所以从开始之日起不到一年就可以进入市场。并且拥有更小的设计团队。

因此,如果客户想要从180nm到5nm的代工厂/节点所需的eFPGA,我们可以在他们的设计进度约束内快速交付。

结论

eFPGA对于加速关键工作量并使SoC适应不断变化的算法和协议非常有价值。借助Flex Logix革命性的互连技术和设计方法,我们可以在不到一年的时间内经济性地在任何铸造工艺节点上使用它。

责任编辑:tzh

-

FPGA

+关注

关注

1656文章

22299浏览量

630597 -

芯片

+关注

关注

462文章

53581浏览量

459612 -

asic

+关注

关注

34文章

1271浏览量

124075 -

晶体管

+关注

关注

78文章

10282浏览量

146407

发布评论请先 登录

没有专利的opencv-python 版本

易飞扬获得一项有源电缆系统的关键发明专利

开源FPGA硬件,核心开发者招募中......

轮边驱动电机专利技术发展

拥抱开源!一起来做FPGA开发板啦!

XSR芯片间互连技术的定义和优势

互连层RC延迟的降低方法

半导体芯片中的互连层次

新能源汽车驱动电机专利信息分析

fpga和cpu的区别 芯片是gpu还是CPU

基于微软专利的带蝴蝶出瞳扩展的光波导结构

华进半导体荣获中国专利优秀奖

研究透视:芯片-互连材料

我们如何使用专利互连来设计eFPGA?

我们如何使用专利互连来设计eFPGA?

评论