本篇主要介绍常用的差分逻辑电平,包括LVDS、xECL、CML、HCSL/LPHCSL、TMDS等。

1、LVDS电平

LVDS器件是近年来National Semiconductor公司发展的一种高速传输芯片,它的传输机制是把TTL逻辑电平转换成低电压差分信号,以便于高速传输。与传统的ECL逻辑相比,它采用CMOS工艺,它的电压摆幅更低,只有400mV,ECL为800mV,动态功耗更小,(输出电流3~5mA)只有ECL电路的1/7(相同的数据传输量),低EMI,价格更低,因而具有很大的优势,从97-98年首先在欧洲开始得到应用。

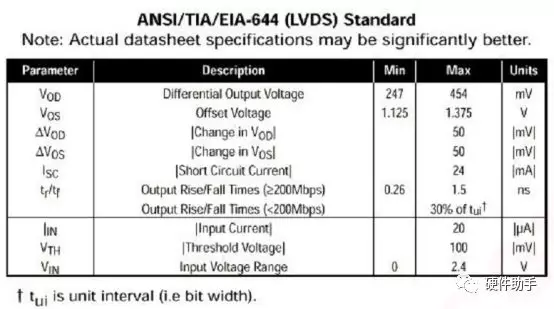

ANSI/TIA/EIA-644是由TR30.2制定的,这个标准定义了收发器的输入输出阻抗,但是这仅仅是一个电气特性标准。其并不包括功能性和协议规格,完全是应用独立的。

ANSI/TIA/EIA-644打算通过使用别的协议来完善整个接口功能。这使的这个标准在很多方面便于实现。在标准中推荐的最大操作速率是655Mbps,理论最大使用速率是1.923Gbps。传输速率与使用的介质损耗有关。这个标准同时也说明了最低的介质要求、接收端的fail-safe电路、多路操作等。

IEEE 1596.3 SCI-LVDS被定义为SCI的一个子集,在IEEE 1596.3中有详细说明。SCI-LVDS说明了应用于高速/低功耗物理接口的电气规范,同时也定义了用于SCI数据传输的包交换的编码格式。SCI-LVDS在特定的条件下也支持高速的RAMLINK传输。

SCI-LVDS同TIA除了在一些电气要求和负载条件有差别,在别的方面十分相似。两个标准支持相似的驱动输出电平,接收门限电平,数据传输速率。在两个标准中TIA的应用更为普遍,同时TIA也支持多负载情况。

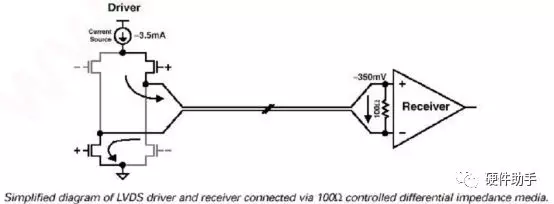

其中发送端是一个约为3.5mA的电流源,产生的3.5mA的电流通过差分线的其中一路到接收端。接收端输入阻抗很高(对于直流表现为高阻),因此驱动器输出的大部分电流通过接收端的100欧姆的匹配电阻产生350mA的电压(100欧姆端接电阻有两个作用:一是用于实现电流向电压的转化,二是用于实现阻抗匹配),同时电流经过差分线的另一条流回发送端。当发送端进行状态变化时它通过改变流经电阻的电流的方向产生有效的‘0’和‘1’态。

LVDS的主要特性如下:

低摆幅:约为350mV,低电流驱动模式意味着可以实现高速传输,ANSI/TIA/EIA-644标准中推荐的最大操作速率是655Mbps,理论最大使用速率是1.923Gbps。

低功耗:恒流源电流驱动,把输出电流限制到约3.5mA左右,使跳变期间的尖峰干扰最小,因而产生的功耗非常小。

具有相对较慢的边沿速率(dV/dt约为0.3V/0.3ns,即1V/ns),同时采用差分传输形式,使其信号噪声和EMI都大为减少,同时具有较强的抗干扰能力。

LVDS的应用模式主要有以下四种:

单向点对点。

双向点对点,通过一对双绞线实现双向的半双工通信,可以由标准的LVDS驱动器和接收器构成,但更好的办法是采用总线LVDS驱动,即BLVDS,是为总线两端都接负载设计的。

多分支形式,即一个驱动器连接多个接收器。当有相同的数据要传给多个负载时,可以采用该种形式。

多点结构,此时多点总线支持多个驱动器,也可以采用BLVDS驱动器,它可以提供双向的半双工通信,但是在任一时刻只能有一个驱动器工作。因而发送的优先权和总线的仲裁权都需要根据不同的应用场合,选用不同的软件协议和硬件方案。为了支持LVDS的多点应用,即多分支结构和多点结构,2001年推出了MLVDS(Multipoint LVDS)标准ANSI/TIA/EIA 899-2001。

LVDS的应用需关注一下几点:

由于输入信号电平范围为0~2.4V,而差分对摆幅最大值为454mV,因此输入端允许信号上携带的直流偏置电平范围为0.227~2.173V,当不满足此要求时,应采取交流耦合。

接收端对输入差分对信号摆幅的要求时100mV。

100Ω端接电阻的作用:一是用于实现电流向电压的转化,二是用于实现阻抗匹配。如果接收端内置端接则不需要。

空闲输入引脚应悬空,以防引入噪声;空闲输出引脚应悬空,以减小功耗。

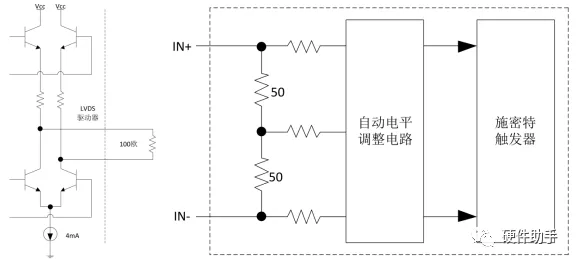

1.1、LVDS接口输入原理

LVDS输入结构如下图所示,输入差分阻抗为100Ω,为适应共模电压宽范围内的变化,输入级还包括一个自动电平调整电路,该电路将共模电压调整为一固定值,该电路后面是一个SCHMITT触发器。SCHMITT触发器为防止不稳定,设计有一定的回滞特性,SCHMITT后级是差分放大器。

LVDS的输入门与其他输入门有一个显著的特点,前面有一个类似于直流电平漂移适配电路(adaptive level shifter),这个电路能够适应直流电平(common-mode voltage)的变化的,使得输入直流电平变化范围可以很宽(0.2V~2.2V,一般为1.2V)。也正因为这样,LVDS比其他信号有更强的共模抗干扰能力。

LVDS输入结构

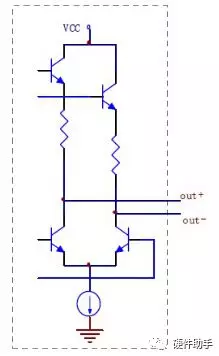

1.2、LVDS接口输出原理

LVDS输出结构如下图所示。电路差分输出阻抗为100Ω。

LVDS输出结构

2、xECL电平

ECL电路(Emitter Coupled Logic,即发射极耦合逻辑电路)是一种非饱和型的数字逻辑电路。与DTL、TTL、S-TTL等逻辑电路不同,ECL电路内部的晶体管工作在非饱和状态(线性区或截止区),从根本上消除了限制速度提高的少数载流子的“存储时间”。因此,它是现有各种逻辑电路中速度最快的一种电路形式,也是目前唯一能够提供亚毫微秒开关时间的实用电路。由于开关管对是轮流导通的,始终有电流流过三极管,所以电路的功耗较大。

典型的ECL基本门电路的结构由三部分组成:差分放大器输入电路,温度-电压补偿(跟踪)偏压网络(参考源)和射极跟随器输出电路。

ECL电路是采用-5.2V电源供电,Vcc是接地的,这样做虽有一些优点,但负电源还是很麻烦。PECL由ECL标准发展而来,采用+5V供电,可以和系统内其他电路共用一个正电源供电。PECL信号的摆幅相对ECL要略小些。+3.3V供电系统的PECL即LVPECL。

LVPECL的主要特点如下:

与LVDS相比,LVPECL的功耗更大,匹配电路更复杂,但支持更高的速率,抗抖动性能更好。在高速设计中,LVPECL常被用做高速时钟和数据的电平,如百兆、千兆PHY芯片的MDI接口,PLL时钟信号等。但由于外部端接电路较复杂,会造成高速信号线上的分叉(stub),因此不适用于要求极高的高速信号,如10Gbps以太网的MDI接口(一般采用CML电平)。

PECL信号的回流是依靠高电平平面(即VCC)回流的,而不是低电平平面回流。所以,为了尽可能的避免信号被干扰,要求电源平面干扰比较小。也就是说,如果电源平面干扰很大,很可能会干扰PECL信号的信号质量。但由于采用电流驱动模式,电源VCC的作用只是提供电流通路和外部偏置电平,电源纹波对信号的影响相对较小。但当LVPECL作为时钟信号的电平时,为防止电源纹波耦合到时钟信号上,仍应该提高电源的质量。

对于输出门来说,OUT+/-两个管脚不管输出是高还是低,输出的电流总和是一定的(即恒流输出)。恒流输出的特性应该说是所有的差分高速信号的共同特点(LVDS/CML电平也是如此)。这样的输出对电源的干扰很小,因为不存在电流的忽大忽小的变化,这样对电源的干扰自然就比较小。

PECL的直流电流能达到14mA,而交流电流的幅度大约为8mA(800mV/100Ω),也就是说PECL的输出门无论是输出高电平还是低电平,都有直流电流流过,换句话说PECL的输出门(三极管)始终工作在放大区,没有进入饱和区和截至区,这样门的传输延时极小,切换速度就可以做得比较快,也就是输出的频率能达到比较高的原因之一。同时,由于始终存在一条VCC到GND的电流通路,因此功耗较大,但工作速率和功耗基本无关。

要判断一个PECL/LVPECL电平输入能否被正常接收,不仅要看交流幅度能否满足输入管脚灵敏度的要求,而且要判断直流幅度是否在正常范围之内(即在VCC-1.3V左右,不能偏得太大,否则输入门将不能正常接收)。在这一点上与LVDS有很大的差别,务必引起注意。

2.1、PECL接口输入原理

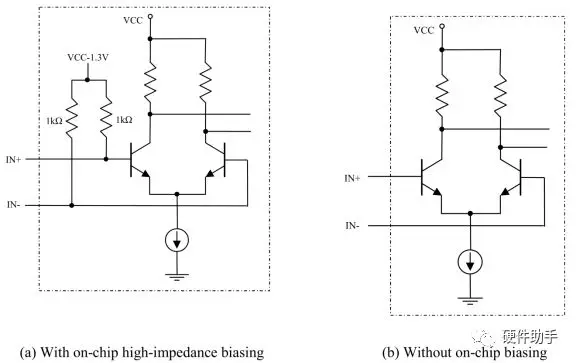

PECL输入是一个具有高输入阻抗的差分对。该差分对共模输入电压需偏置到VCC-1.3V,这样允许的输入信号电平动态最大。MAXIM公司的PECL接口有两种形式的输入结构,一种是在芯片上已加有偏置电路,如MAX3867、MAX3675,另一种则需要外加直流偏置。

PECL输入电路结构

2.2、PECL接口输出原理

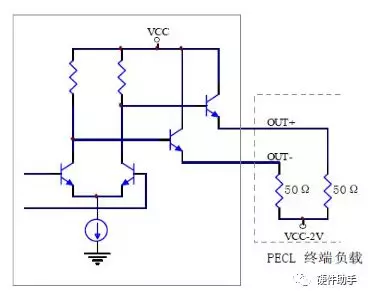

PECL电路的输出包含一个差分对和一对射随器。输出射随器工作在正电源范围内,其电流始终存在,这样有利于提高开关速度。标准的输出负载是接50Ω至VCC-2V的电平上,在这种负载条件下,OUT+与OUT-输出电流为14mA,OUT+与OUT-的静态电平典型值为VCC-1.3V(VCC-2V+14mA×50Ω)。PECL结构的输出阻抗很低,典型值为4~5Ω,这表明它有很强的驱动能力,但当负载与PECL的输出端之间有一段传输线时,低的阻抗造成的失配将导致信号时域波形的振铃现象。

PECL/LVPECL输出结构

3、CML电平

CML即Current Mode Logic,主要靠电流驱动,它的输入和输出是匹配好的,从而减少了外围器件,使用时直接连接就可以,是高速数据接口形式中最简单的一种。如XAUI、10G XFI接口均采用CML电平。

CML电平的特点如下:

CML电平是一种比较简洁的电平,它内置匹配电阻(输入输出都有50欧姆的电阻),这样用户使用的时候特别简单,不需要象ECL电平一样加一堆的偏置电阻和匹配电阻。

由于输出门也有50欧姆的匹配电阻,使得二次反射信号也能被这个电阻匹配掉,这样就避免了多次反射导致的信号劣化(振铃现象)。在这一点,与ECL电平相比有很大的改进,所以CML电平所能支持的速率比较高。

从光口的抖动指标来看,CML电平具有抖动指标小的特性。对比3种电平抖动方面的性能:CML最优、ECL次之、LVDS比较差。这就是一般情况下LVDS信号很少做为光接口驱动信号的原因之一(当然,输出信号幅度比较小、电流驱动能力比较弱应该也是原因之一吧)。

CML电平也是采用恒流驱动方式。

CML电平的输出AC摆幅能达到800mV。一般情况下,CML电平可以是直流耦合方式对接,也可以是交流耦合方式对接。

3.1、CML接口输入原理

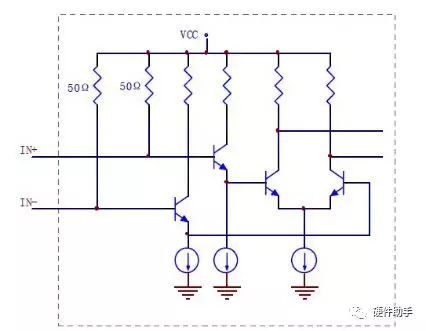

CML输入结构有几个重要特点,这也使它在高速数据传输中成为常用的方式,如下图,MAXIM公司的CML输入阻抗为50Ω,容易使用。输入晶体管作为射随器,后面驱动一差分放大器。

CML输入电路结构

3.2、CML接口输出原理

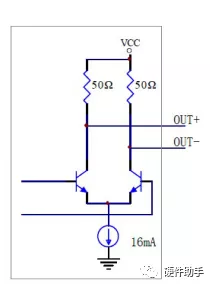

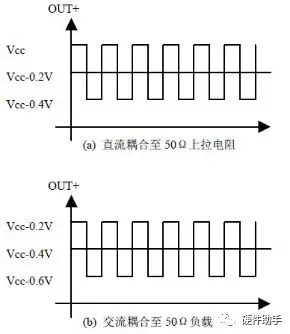

CML接口的输出电路形式是一个差分对,该差分对的集电极电阻为50Ω,输出信号的高低电平切换是靠共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为16mA,假定CML输出负载为一50Ω上拉电阻,则单端CML输出信号的摆幅为Vcc-0.4V~Vcc。在这种情况下,差分输出信号摆幅为800mV,共模电压为Vcc-0.2V。若CML输出采用交流耦合至50Ω负载,这时的直流阻抗由集电极电阻决定,为50Ω,CML输出共模电压变为Vcc-0.4V,差分信号摆幅仍为800mV。在交流和直流耦合情况下输出波形见下图。

CML输出结构

CML在不同耦合方式时的输出波形

4、LVDS、LVPECL、CML比较

三种电平都是高速设计中常用的电平,但各有特色:

驱动模式:都属于电流驱动。

外部端接:CML最简单,一般无需外部端接,直接连接即可;LVDS次之,需在接收端增加一个100Ω的终结电阻(内置的不需要);LVPECL最复杂,其输出端需偏置到VCC-2V,输入端需偏置到VCC-1.3V。

功耗:LVDS差分对摆幅最小,因此功耗也最小,在相同工作速率下,功耗不到LVPECL的三分之一;CML和LVPECL差分对摆幅相对较大,且内部三极管工作于非饱和状态,功耗较大,基于结构上的差异,CML的功耗低于LVPECL。

工作速率:由于CML和LVPECL内部三极管工作于非饱和状态,逻辑翻转速率高,能支持更高的数据速率;同时,由于LVDS差分对的输入摆幅较小(LVDS为100mV,LVPECL为310mV,CML为400mV;输出摆幅:LVDS为350mV,LVPECL为800mV,CML为800mV),噪声容限较小,不利于高速传输。

耦合方式:都支持直流耦合和交流耦合。

5、HCSL/LPHCSL

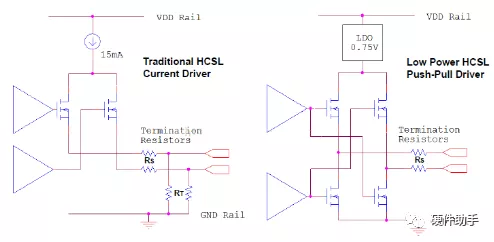

HCSL即High-speed Current Steering Logic。

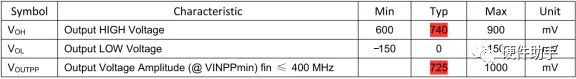

LPHCSL(Low-Power HCSL)是为了降低传统的HCSL驱动器的功耗而开发的。LPHCSL的主要优点包括更好的驱动长线的性能,易于AC耦合,减少PCB板子面积,易于布线,降低材料成本,重要的是要注意HCSL驱动器与LPHCSL驱动器对HCSL接收器来说都是一样的。

HCSL和LPHCSL输出电路结构

HCSL的输出是通过控制正负输出差分对中的15mA电流,电源功耗为15mA×3.3V约50mW。而LPHCSL不是采用传统的HCSL的电流驱动,而是采用推挽电压驱动,电流消耗大约4~5mA。

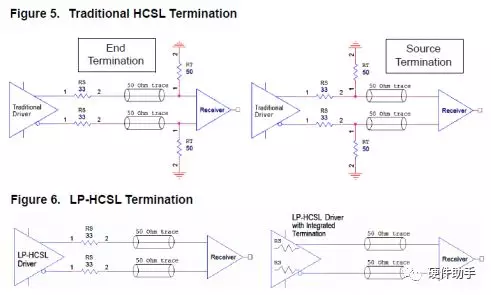

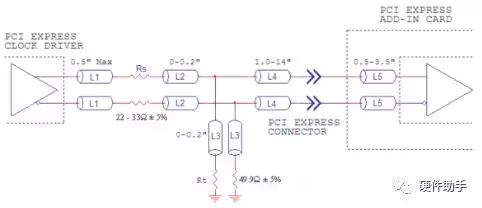

驱动器本身具有17欧姆的输出阻抗(CMOS的输出阻抗),所以,需要串联一个33欧姆的电阻,以获得与50欧姆传输线的匹配。对于传统的HCSL,为了避免出现过度的振铃,串联电阻RS是必须要的。

某些接收器片内可能有一个100欧姆的差分终端,这样的接收器通常更常见,因为可以处理比较宽范围的幅度和共模电压,以及可能要去AC耦合的时钟信号,LPHCSL驱动器可以稳定驱动双终端(在源和接收处都有终端电阻)。

LPHCSL并不需要对地的终端电阻。而由于功耗的原因,传统的HCSL驱动器不可能就将终端电阻集成到内部,尤其是芯片有许多输出的时候。很显然,LPHCSL相对于传统HCSL使用了更少的元件,降低了板子面积和材料成本。

从原理上,传统的HCSL要求DC耦合,而LPHCSL并不要求DC耦合。我们可以将AC耦合电容串接到线路上,这样做并不会影响信号的摆幅和终端属性。而传统的HCSL使用AC耦合时,必须仔细考虑对地的DC路径,还可能需要额外增加元件。

PCIe的REFCLK+/-使用的就是LPHCSL电平。

PCIe时钟要求的上升速率为0.6V/ns到4.0V/ns,LPHCSL在驱动长线时能提供更高的上升速率。而传统的HCSL驱动取决于外部50欧姆终端来产生时钟的下降沿,这使得上升/下降匹配非常困难,因为仅时钟的上升沿受传统HCSL输出控制,而LPHCSL输出控制时钟的上升沿和下降沿,LPHCSL更快的上升速率对驱动长线是非常重要的。

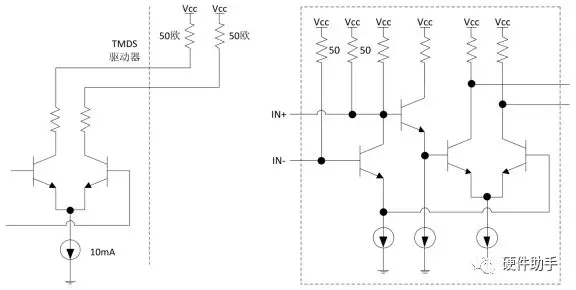

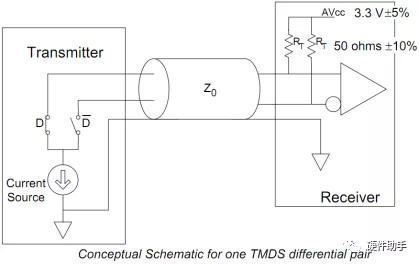

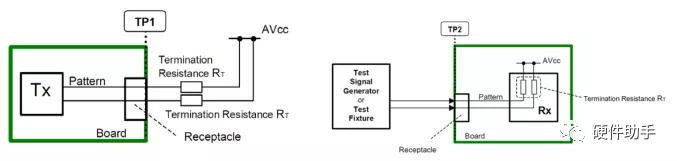

6、TMDS

TMDS(Transition-Minimized Differential Signaling,最小化传输差分信号)是HDMI、DP协议中定义的电平,下图是TMDS的接口输入输出框图,详细的特性可参考HDMI标准。

除此之外,还有像差分HSTL、PPDS(Point-to-Point Differential Signaling)、RSDS(Reduced Swing Differential Signaling)之类的差分逻辑电平,由于使用较少,暂不做详细介绍。

编辑:hfy

-

CMOS

+关注

关注

58文章

6236浏览量

243428 -

lvds

+关注

关注

2文章

1244浏览量

70250 -

PCIe

+关注

关注

16文章

1483浏览量

88944 -

差分信号

+关注

关注

4文章

411浏览量

29080 -

schmitt触发器

+关注

关注

0文章

2浏览量

4739

发布评论请先 登录

快点PCB原创∣详解信号逻辑电平标准

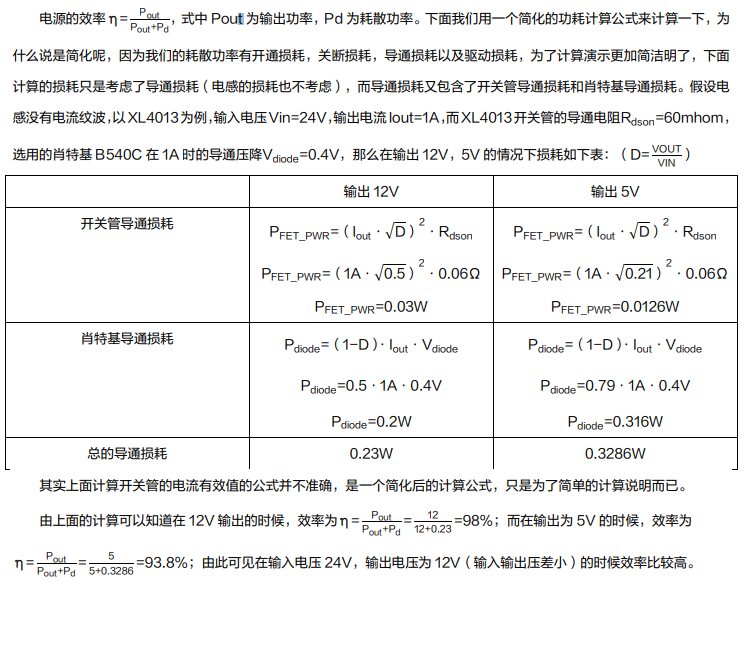

输入输出电压差与效率的关系

常见差分逻辑电平和相关输入输出原理

常见差分逻辑电平和相关输入输出原理

评论