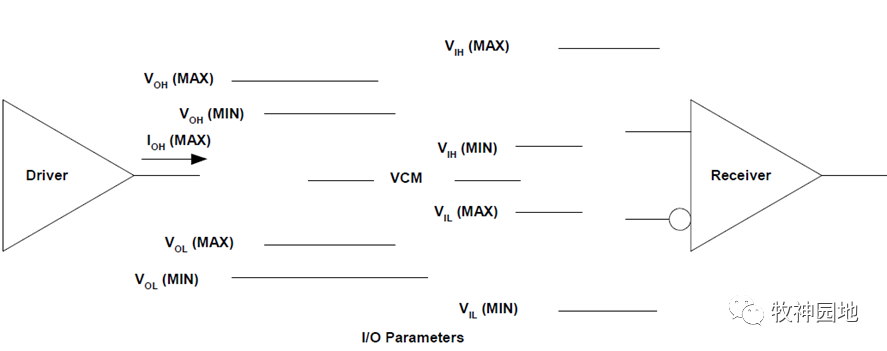

由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑电平能够安全、可靠地连接,逻辑电平匹配将是电路设计中必须考虑的问题。

一、逻辑电平匹配原则

1.1、电平关系,驱动器件的输出电压必须处在负载器件所要求的输入电压范围之内,并保证一定的噪声容限(Vohmin-Vihmin≥0.4V,Vilmax-Volmax≥0.4V)。

1.2、驱动能力,驱动器件必须能满足负载器件对灌电流、拉电流最大需求。

1.3、时延特性,设计中要充分考虑逻辑电平转换带来的延时,保证数据传输能满足负载器件的时序容限,特别是高速信号。

1.4、上升/下降时间特性,应保证Tplh和Tphl满足电路时序关系的要求和EMC的要求。

1.5、电压过冲要求,过冲不应超出器件允许的电压绝对最大值,否则有可能导致器件损坏。

二、匹配电路分析

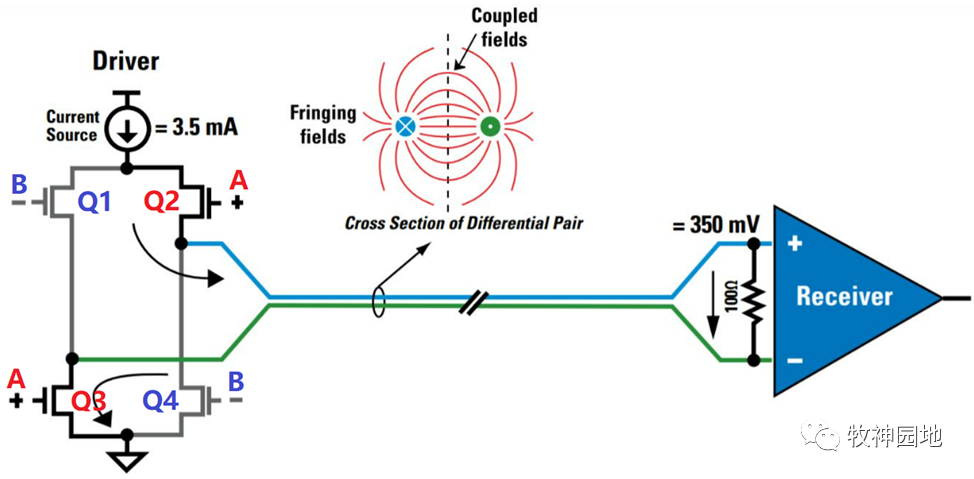

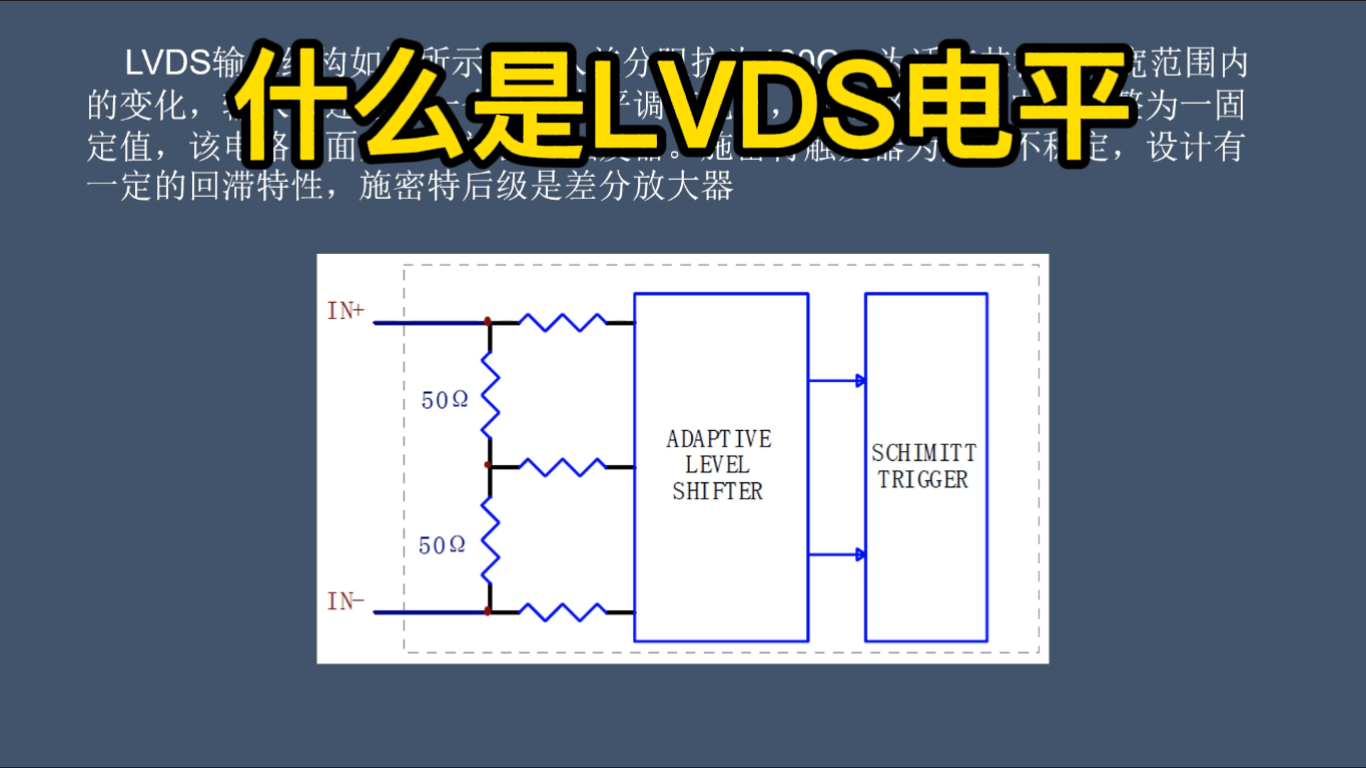

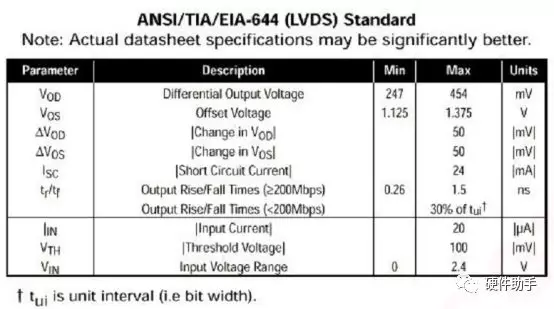

2.1、LVDS到LVDS的连接

LVDS的输入与输出都是内匹配的,所以LVDS之间可以直接连接,具体可参考:硬件设计:逻辑电平--LVDS。

2.2、PECL到PECL的连接

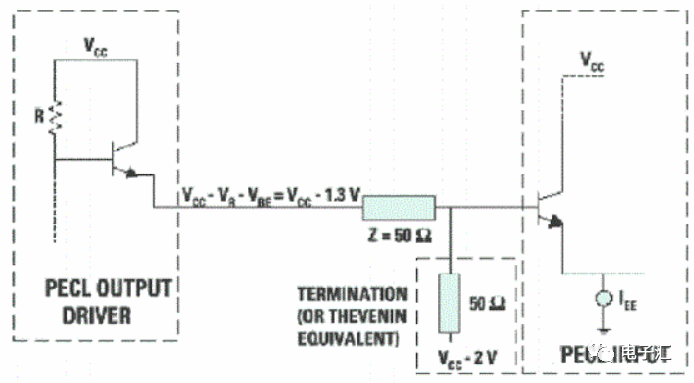

PECL电平的直流偏置电路要求是戴维南等效终端电路为输出负载通过50Ω电阻接到VCC-2V的电源上,如图1所示。在这种负载条件下,OUT+与OUT-的静态电平典型值为VCC-1.3V,输出电流典型值为14mA。

图1 标准PECL终端

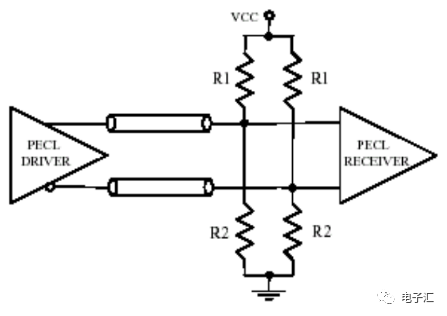

PECL到PECL的连接包括直流耦合和交流耦合两种方式;

图2PECL直流耦合匹配电路

直流耦合的电路连接如图2所示,差分单端线对交流信号的等效电路为连接50Ω阻抗到地;直流偏置的等效电路为连接50Ω电阻到VCC-2V,且通过50Ω电阻的电流为14mA。所以R1、R2满足的公式为:

R1//R2=50交流等效:电压源短路,电流源开路

R2/(R1+R2)=(VCC-2V)/VCC直流等效:14mA电流源与VCC电压源共同作用,使线上电压为VCC-1.3V;当只考虑14mA电流源时,负载为R1//R2,所以输出线路上的电压为0.7V;为满足要求,需要电阻分压为VCC-2V。

综合上面两式:

3.3V情况下:R1=130ΩR2=82Ω;

5V情况下:R1=82Ω R2=130Ω;

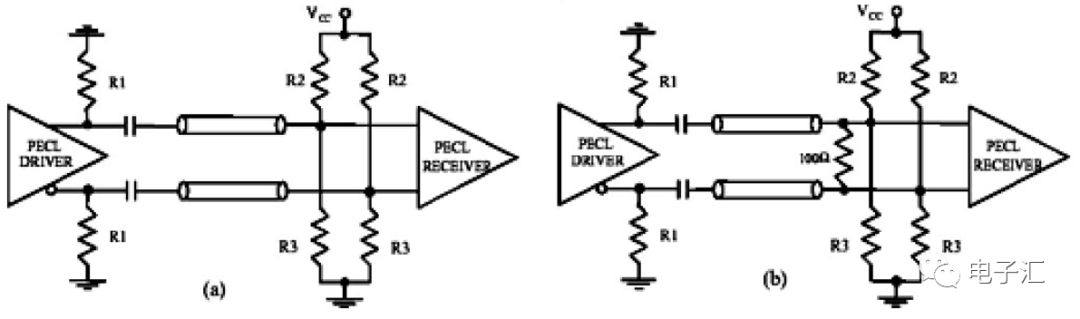

图3 PECL交流耦合匹配电路

交流耦合的电路连接如图3所示,有a和b两种匹配方式;对于图a的匹配电路分析如下:

1.驱动端

交流:交流信号直接通过电容耦合至后级电路,耦合电容和电阻R1靠近输出端;

直流:R1提供14mA到地的通路,且信号线上的等效电压为VCC-1.3V,即R1=(VCC-1.3V)/14mA;(电源为3.3V时,R1=142Ω(一般取142Ω~200Ω);电源为5V时,R1=270Ω)

2.接收端

交流:R2//R3的等效电阻为50Ω;

直流:分压电路使线上电压偏压到VCC-1.3V,即R3*VCC/(R2+R3)=VCC-1.3V;

计算得:R2=50VCC/(VCC-1.3V)R3=50VCC/1.3V;

3.3V情况下:R2=82ΩR3=130Ω;

5V情况下:R2=68ΩR3=180Ω;

图b的匹配电路分析如下:

1.驱动端

交流:交流信号直接通过电容耦合至后级电路,耦合电容和电阻R1靠近输出端;

直流:R1提供14mA到地的通路,且信号线上的等效电压为VCC-1.3V,即R1=(VCC-1.3V)/14mA;(电源为3.3V时,R1=142Ω(一般取142Ω~200Ω);电源为5V时,R1=270Ω)

2.接收端

交流:R2//R3//50的等效电阻约为50Ω;

直流:分压电路使线上电压偏压到VCC-1.3V,即R3*VCC/(R2+R3)=VCC-1.3V;

所以R2和R3通常选如下值:3.3V情况下:R2=2.7KR3=4.3K;

5V情况下:R2=2.7KR3=7.8K;

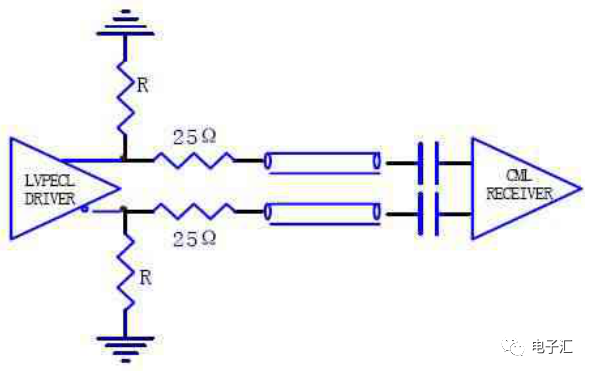

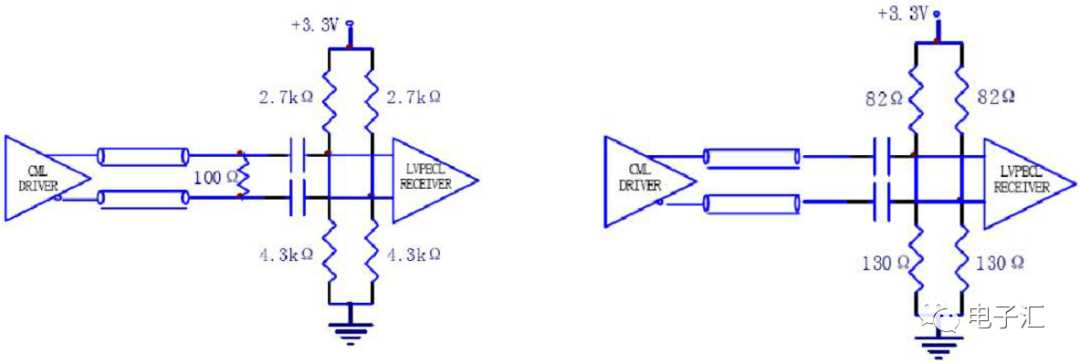

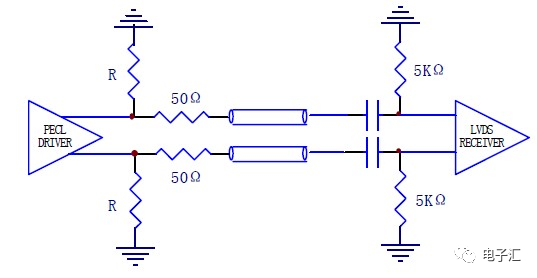

2.3、LVPECL到CML的连接

LVPECL到CML的连接包括直流耦合和交流耦合两种方式,交流耦合的方式如图4所示;

图4 LVPECL到CML的交流耦合方式

1.驱动端

驱动端的直流偏置电路和PECL和PECL的交流耦合情况一样,所以R的取值为142Ω~200Ω;

如果LVPECL的输出信号摆幅大于CML的接收范围(LVPECL输出摆幅为600~1000mV,CML输入摆幅为400~1000mV),可以在信号通道上串一个25Ω的电阻,这时CML输入端的电压摆幅变为原来的0.67倍,比例关系计算可参考硬件设计--阻抗匹配。

2.接收端

由于CML接收器内部一般包含50Ω的匹配电阻,所以耦合电容输出端直连CML接收器。

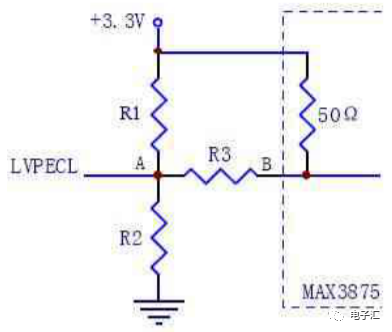

图5 LVPECL到CML直流耦合电平转换网络

LVPECL到CML的直流耦合方式如图5所示,在LVPECL到CML的直流耦合方式中需要一个电平转换网络,该电平转换网络的作用是匹配LVPECL的输出与CML的输入共模电压。一般要求该电平转换网络引入的损耗要小,以保证LVPECL的输出经过衰减后仍能满足CML的输入灵敏度的要求;另外还要求自LVPECL端看到的负载阻抗近似50Ω,所以有以下方程式:

计算结果为:R1=170ΩR2=82.5RR3=450Ω;

增益要求取决于芯片,当芯片输入灵敏度要求为20mV时,20mV/400mV=0.05;

2.4、CML到LVPECL的连接

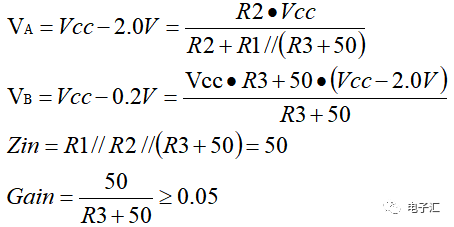

CML到LVPECL的连接基本上都是采用交流耦合的方式,如图6所示,电阻网络计算方式可参考2.2小节。

图6 CML到LVPECL交流耦合方式

当LVPECL有内部偏置时,匹配电路可设计如图7所示。

图7 CML到LVPECL交流耦合方式(LVPECL带内部偏置)

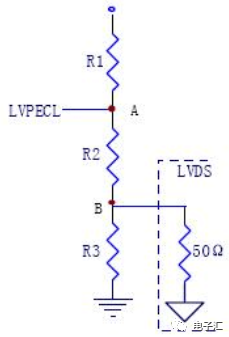

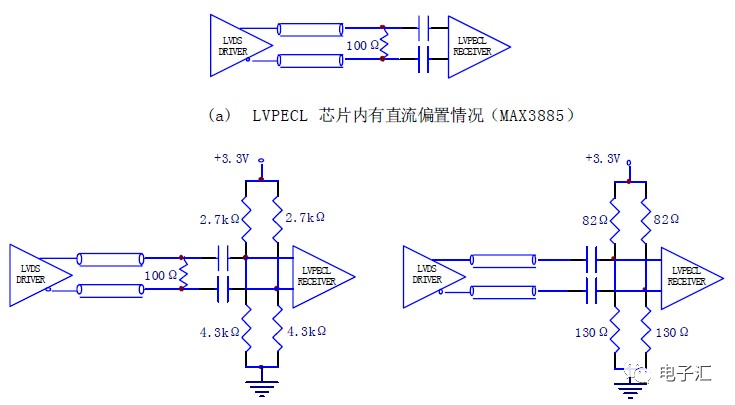

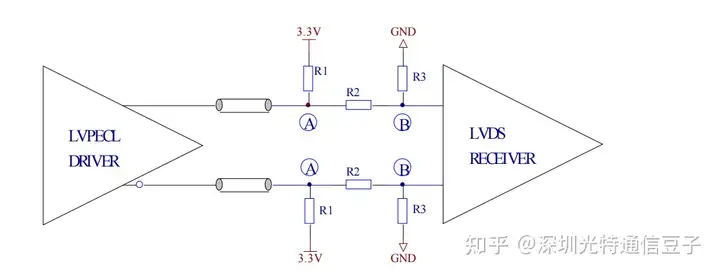

2.5、LVPECL到LVDS的连接

LVPECL到LVDS的连接方式有直流耦合和交流耦合两种方式,其中LVPECL到LVDS的直流耦合方式需要一个电阻网络,如图8所示,设计该网络时需考虑:

1.LVPECL的最优输出负载为50Ω接到VCC-2V;

2.电阻网络引入的衰减不应太大,LVPECL输出信号经衰减后仍能落在LVDS的有效范围内;

3.LVDS的输入差分阻抗为100Ω,或者单端到虚拟地为50Ω(该阻抗不提供直流通路);

图8 LVPECL到LVDS直流耦合电平转换网络

要完成LVPECL到LVDS的逻辑转换,需要满足如下方程式:

计算结果得:R1=182ΩR2=48ΩR3=48ΩVA=1.14VRAC=51.8ΩRDC=62.8ΩGain=0.337;

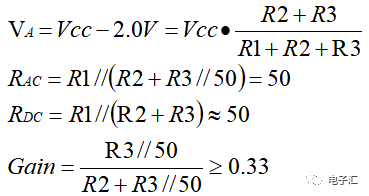

所以得到LVPECL到LVDS直流耦合连接如图9所示。

图9 LVPECL到LVDS的连接

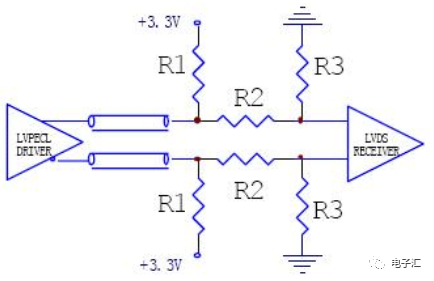

LVPECL到LVDS的交流耦合如图10所示,LVPECL的输出端到地需加直流偏置电阻(142Ω~200Ω),同时信号通道上一定要串接50Ω的电阻,以提供一定衰减。LVDS的输入端到地需加5K的电阻,以提供近似0.86V的共模电压(LVDS输入端并联100Ω电阻,对于交流来说没有地电平,只有虚拟地电平,所以加5K电阻到地,确定实际地电平)。

图10 LVPECL到LVDS交流耦合方式

2.6、LVDS到LVPECL的连接

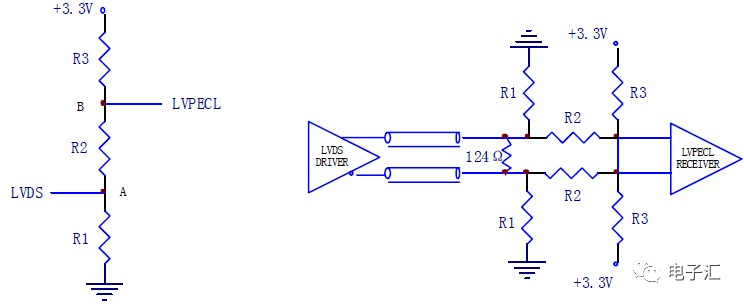

LVDS到LVPECL的连接方式有直流耦合和交流耦合两种方式,当采用直流耦合方式时,需要增加一个电阻网络,用于完成直流电平的转换,如图11所示,设计该网络时需考虑:

1.LVDS输出电平为1.2V,LVPECL的输入电平为Vcc-1.3V;

2.LVDS的输出是以地为基准,而LVPECL的输入是以电源为基准,这要求考虑电阻网络时应注意LVDS的输出电位不应对供电电源敏感;

3.需要折中考虑功耗和速度,如果电阻值取的较小,可以允许电路在更高的速度下工作,但功耗较大,LVDS的输出性能容易受电源的波动影响;

4.考虑电阻网络与传输线的阻抗匹配问题;

图11 LVDS到LVPECL直流耦合方式

要完成LVDS到LVPECL的逻辑转换,需要满足如下方程式:

计算结果得:R1=406ΩR2=270ΩR3=440ΩRIN=50ΩGain=0.62;

但考虑到避免非常用料的使用,所以最终取值可选择:R1=402ΩR2=270ΩR3=442ΩRIN=49.9ΩGain=0.62;

LVDS的最小差分输出信号摆幅为500mV,而经过上述转换网络后加到LVPECL输入端的信号摆幅变为310mV,虽然该幅度低于LVPECL的输入标准,但是对于绝大数LVPECL电路来说,该幅度是足够的。

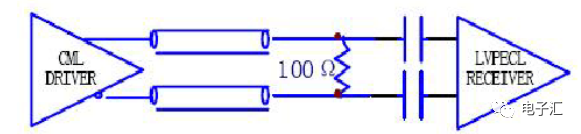

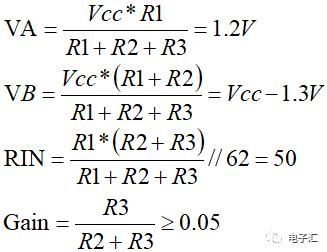

LVDS到LVPECL的交流耦合方式主要有图12中三种方式,在耦合电容前完成阻抗匹配然后给LVPECL增加直流偏置,或者直流偏置和阻抗匹配在一起,具体计算方式可参考2.2小节。

图12 LVDS到LVPECL交流耦合方式

2.7、CML到LVDS的连接

一般情况下,在光传输系统中没有CML和LVDS的互连问题,因为LVDS通常是作并联数据的传输,数据速率为155MHz,622MHz或1.25GHz;而CML常用来做串行数据的传输,数据速率为2.5GHz或10GHz。

-

lvds

+关注

关注

2文章

1216浏览量

69119 -

逻辑电平

+关注

关注

0文章

203浏览量

15001 -

差分信号

+关注

关注

4文章

405浏览量

28872 -

PECL

+关注

关注

0文章

327浏览量

14601

原文标题:逻辑电平--差分信号(PECL、LVDS、CML)电平匹配

文章出处:【微信号:电子汇,微信公众号:电子汇】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

LVDS&CML电平设计基础知识

快点PCB原创∣详解信号逻辑电平标准

差分逻辑电平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

LVDS和CML与LVPECL的同种差分逻辑电平之间的互连教程

详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载

逻辑电平--差分信号(PECL、LVDS、CML)电平匹配

逻辑电平--差分信号(PECL、LVDS、CML)电平匹配

评论