对于FPGA开发而言,仿真是开发流程中必不可少的一步,也是非常重要的一步,仿真是将RTL代码模拟运行,得到module中信号波形,再进行功能分析的过程。强大的功能与速度兼具的modelsim仿真就是你开发过程的最合适的选择了,下面我以简单的24进制计数器带各位熟悉modelsim仿真流程及波形。

一、新建工作库Library

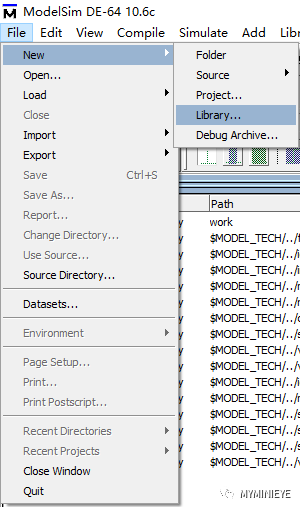

1、点击File>New>Library

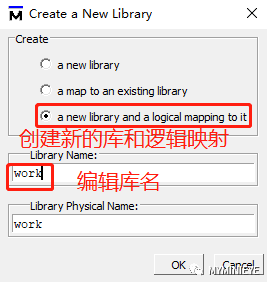

创建新的库和逻辑映射,编辑库名,点击ok确定

如果已经建立过work库可以跳过该步骤

2、库的其他功能

由于modelsim无法识别其他厂商器件的IPcore,所以如果需要用到综合器对应厂商如Xilinx或Gowin芯片的功能,则需对modelsim添加厂商提供的库相关文件,并编译库,从而达到调用库的功能,进而对 VIVADO或Gowin软件进行设置,最后进行联合仿真。

二、新建工程Project

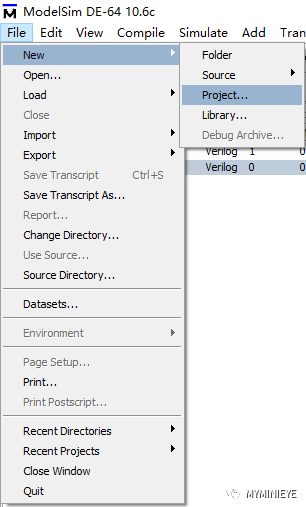

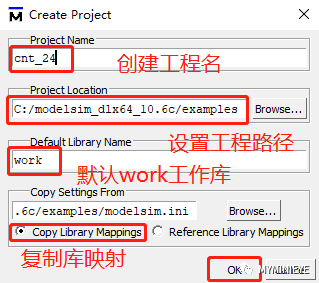

点击File>New>Project

创建工程名、设置工程路径、确定默认工作库

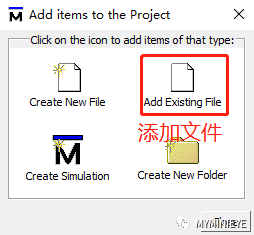

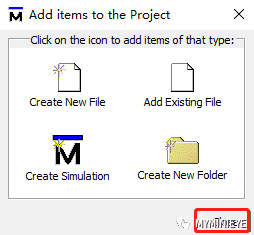

三、添加仿真源文件

仿真源文件包含功能源文件与测试激励源文件;

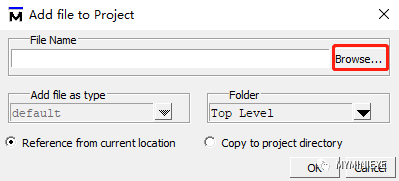

点击Browse,浏览文件

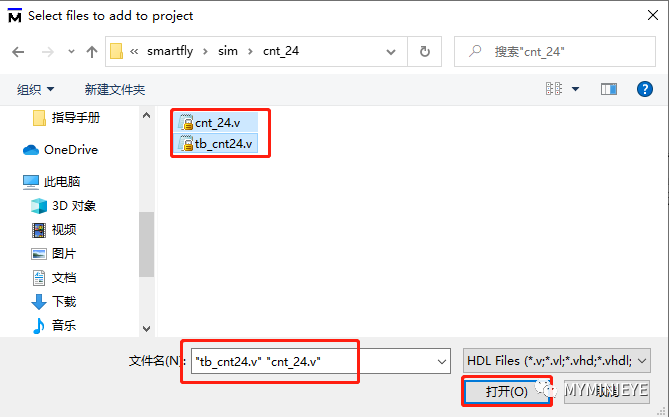

选择两个文件并打开

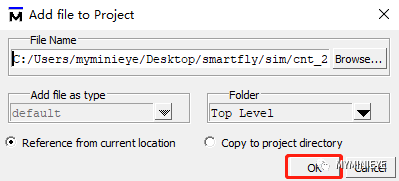

添加文件到工程,点击OK

点击close关闭

如有不清楚testbench编写,可以参考myminieye公益课堂系列教程第18集;仿真基础篇1FPGA_simulation_testbench,

连接:https://www.bilibili.com/video/BV1EE411475Z?p=18

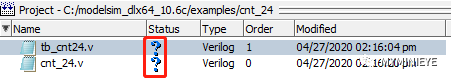

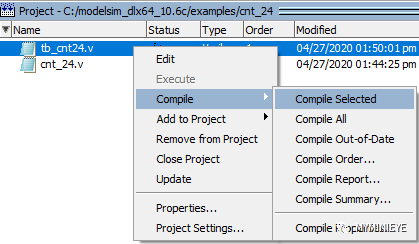

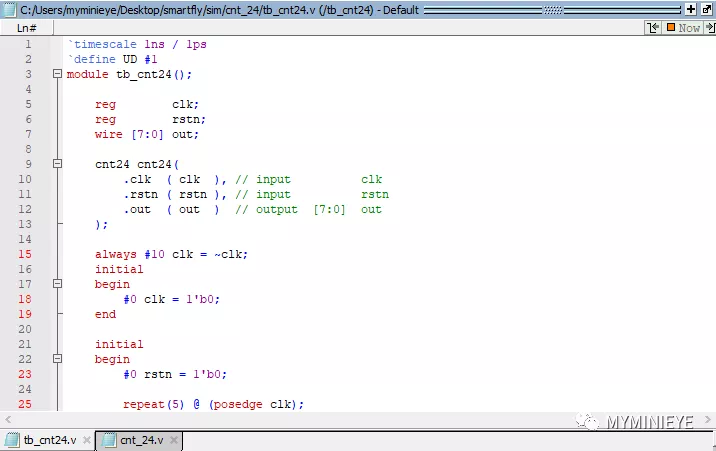

四、仿真源文件编译

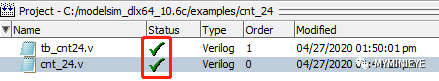

若状态Status显示“?”为文件未编译

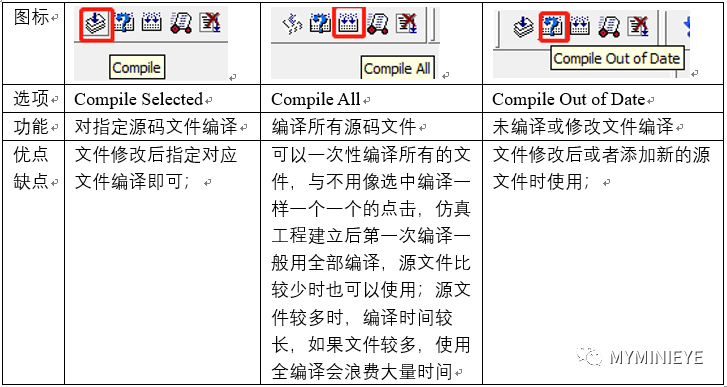

常用有3种编译方式:编译选中文件、编译所有文件、编译未编译文件;对应操作方式如下:

菜单栏: 右击菜单

图标:

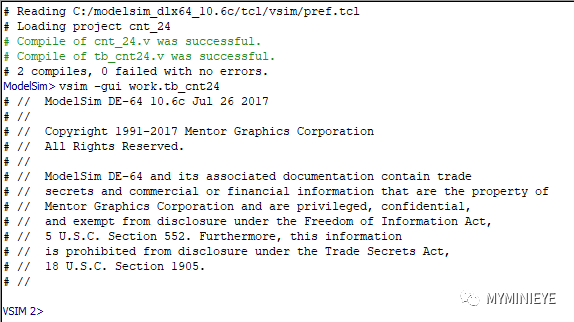

若状态Status显示“√”则为编译成功,也可从下方Transcript看出文件编译成功

若状态Status并未显示“√“,或者下方Transcript显示编译不成功,则需修改对应的源文件。

修改后重新编译,可从Transcript检查是否有语法错误等,直至显示编译成功。

五、仿真运行

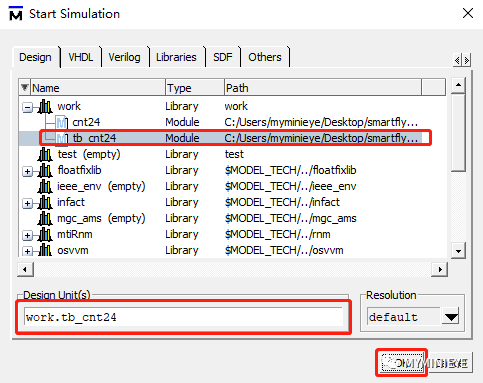

编译成功后即可运行仿真了;

开始仿真:Simulation>Start Simulation;或者点击下图中的小图标

此时记得要选中tb测试激励文件(testbench文件)进行仿真,点击ok确定

如果Transcript显示无报错则可以进行下一步操作

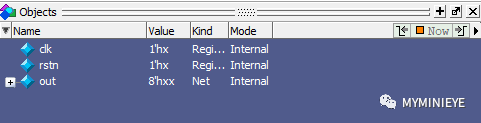

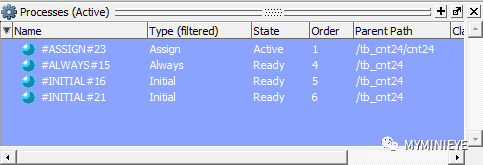

端口类型

激励类型

2.添加波形文件

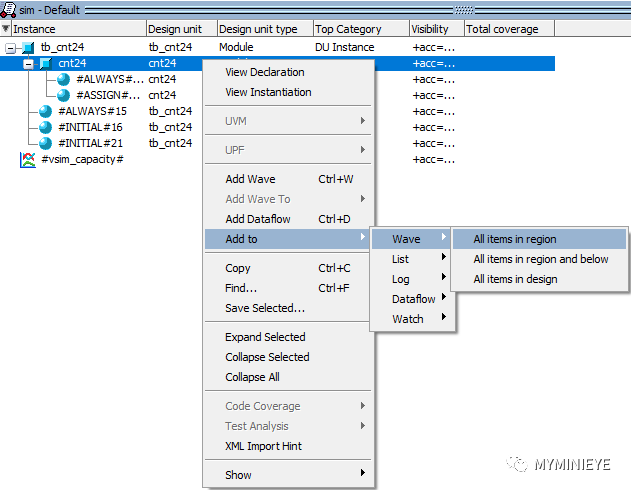

Sim:选择下图所示的sim,右键点击选中tb测试文件>addto>wave>all items in region

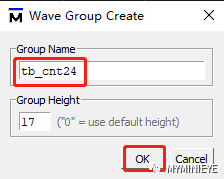

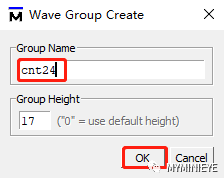

为了便于观察波形,进行分组并命名,点击ok确定;

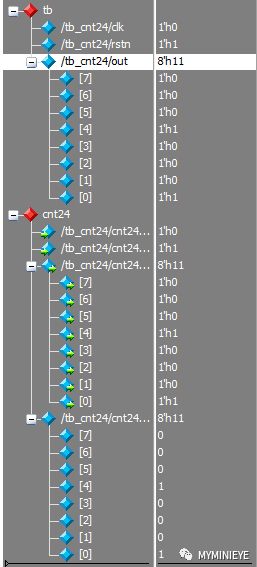

为了与tb测试文件仿真波形进行对比,同理可添加源文件波形;

同样为了便于观察波形,进行分组并命名;

信号位置移动方便多个信号同时分析:分组后,可以上下拖拽所需要分析的信号,方便且清晰的上下对比所需波形之间的差异,此时分组的目的就是能与拖拽前后波形信号对比区分,不至于搞混;

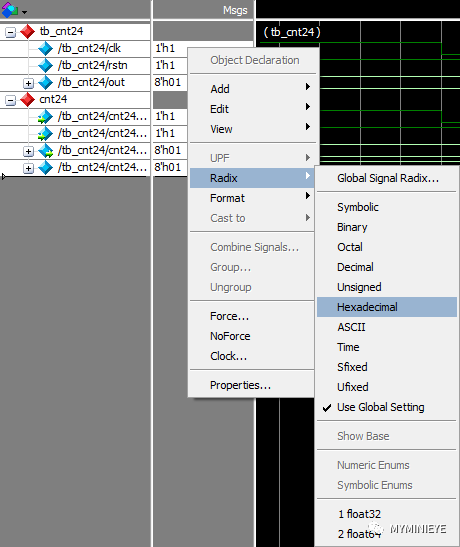

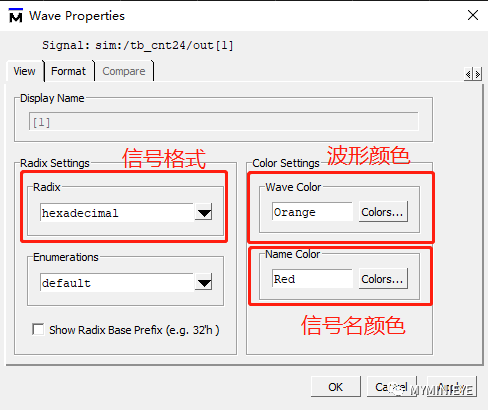

信号显示属性设置,选择合适的显示方式便于功能分析更好的找到信号并确定结果是否符合预期;

信号显示进制设置:

例:选择十六进制的信号格式:选中对应信号右键>Radix>hexadecimal

可修改为常用的信号格式:二进制Binary、八进制 Octal、十进制Decimal、无符号型Unsigned、十六进制Hexadecimal等;

也可在属性Properties中修改信号格式,修改波形颜色,信号名颜色;

也可选择需要修改的信号波形颜色及信号名颜色,这样在仿真波形图中能更容易分辨;

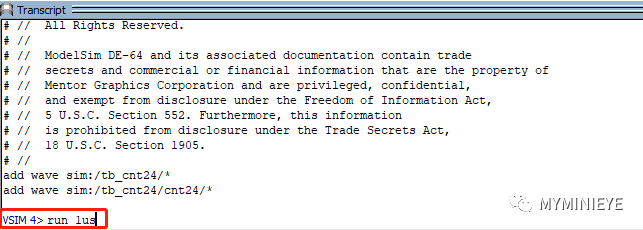

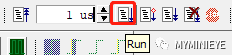

3、 运行仿真工程,并设置运行时间

可在Transcript命令行输入run 1us命令,运行 1us 时间,也可运行其他时间

也可点击下图中输入需要运行波形的时间,然后点击图中的小图标。

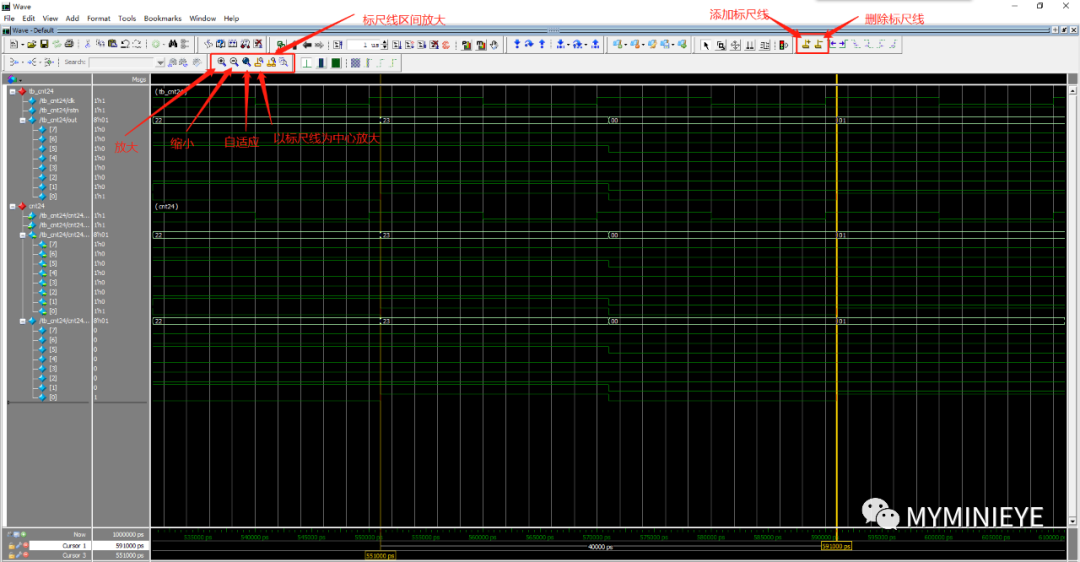

4波形界面调整

下图为波形界面常用的控制图标解析;

自此Modelsim将RTL代码转化为波形的功能完成,仿真后续内容需要自行根据实际module功能进行波形分析。

编辑:hfy

-

FPGA

+关注

关注

1664文章

22502浏览量

639165 -

仿真

+关注

关注

55文章

4535浏览量

138659 -

波形

+关注

关注

3文章

407浏览量

33201 -

ModelSim

+关注

关注

5文章

175浏览量

49476

发布评论请先 登录

赛目科技Sim Pro工具助力国标仿真测试流程规范落地

如何使用Modelsim仿真I2C控制器

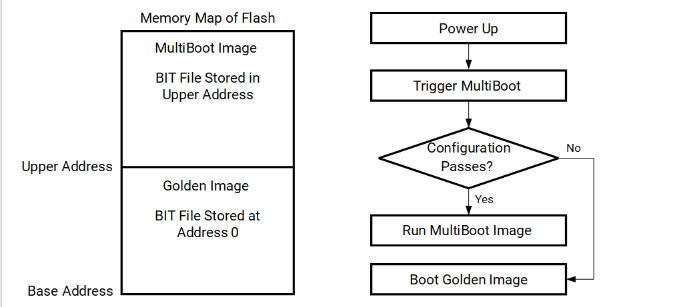

【ALINX 教程】FPGA Multiboot 功能实现——基于 ALINX Artix US+ AXAU25 开发板

电能质量在线监测装置历史波形回放的操作流程是怎样的

FPGA板下载运行调试流程

FPGA板下载调试流程

ModelSim仿真蜂鸟E203 / 200 教程【功能验证】

eVTOL舱内噪声响应分析的仿真流程

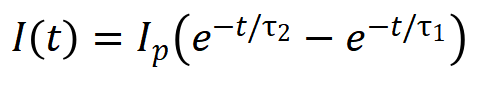

8/20浪涌测试波形时域转频域的解释及仿真思路(基于Python)

拥抱开源!一起来做FPGA开发板啦!

基于 FPGA 的任意波形发生器+低通滤波器系统设计

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

FPGA开发:modelsim仿真流程及波形

FPGA开发:modelsim仿真流程及波形

评论