各位工程师朋友,同学们大家好!我是本期“来实战”项目《运动目标追踪系统》的执行官。本项目由电路城发起,由ALINX赞助的黑金国产FPGA板卡Logos系列PGL22G学习板实现。

我是一个热爱技术的在校学生。希望可以通过本次的项目来帮助更多的同学,给予一个机会来了解什么是真正的实战项目,也让之前没有竞赛经验的朋友了解一下,竞赛对于我们学生来说并没有那么远。帮助更多的电子专业的同学找到学习的方向,更顺利的进入这个行业,为电子行业做出一份自己的贡献。许多同学在学校期间不去做项目的原因并不是不愿意去做,而是没有方向。其实大项目就可以通过竞赛来获得,竞赛中的一些命题项目可以给予你很多灵感,有了方向之后,即使是个大项目,他也是由一个一个小部分组成的,一步一步完成一个个小项目,自己的大工程不久也就成功了。项目本身的意义可能是在做保护区的摄像头,捕捉动态视频;也可以在监控中做一些应用。更重要的意义就是给广大同学们一个学习视频处理的机会,让想学而不知道怎么去学的同学一个模板。

很多在最初接触FPGA的同学都有这个问题,甚至以为FPGA和单片机一样下板子烧代码。其实不是这样的,FPGA不是单片机,首先FPGA和单片机的区别,本质上是软件和硬件的区别,FPGA更偏向于硬件电路,而单片机更偏于软件。单片机是一种微处理器,类似于电脑CPU的,它一般采用的是哈佛总线结构,或者冯诺依曼结构,对单片机的编程很大程度上要考虑到它的结构和各个寄存器的作用,而FPGA 它的结构是查找表结构,其程序不用去太考虑芯片的结构,要注意的是时序上问题,它的结构比较复杂,功能也很强大,一般应用在通信领域等比较高端的场合,单片机是一个微控制器,通过加载模块软件来实现某种功能,是成型的芯片;FPGA是用来设计芯片的芯片。FPGA由于是硬件电路,运行速度直接取决于晶振速度,系统稳定,特别适合高速接口电路。单片机由于是单线程,哪怕是常用的M3系列流水线也是单线程执行,程序语句需要等待单片机周期才能执行。单片机设计属软件范畴;它的硬件(单片机芯片)是固定的,通过软件编程语言描述软件指令在硬件芯片上的执行;

FPGA开发的语言是Verilog HDL。HDL代表的就是硬件描述语言,描述就代表他并不是一个开发性的语言。相比C语言开发,Verilog更像是你先设计好电路,再用Verilog描述出来你的设计。而对于一个完整的FPGA工程应包含以下几个步骤:算法实现,模块化,模块的硬件电路设计,硬件描述语言书写,小模块进行仿真,总模块的连接,总体工程的仿真,板级验证。下面我们就进入正题......

项目设计

步骤一:FPGA硬件资源与算法设计

1.FPGA硬件资源介绍

首先感谢黑金ALINX提供的开发板对本项目的大力支持,期望以后能有更多的机会合作。对于黑金国产FPGA板卡Logos系列PGL22G学习板,它配备了以下资源:

系统逻辑部分由ov5640驱动模块、RGB转Ycbcr模块、存储控制模块、HDMI驱动模块、图像处理模块、追踪控制模块、sim900a驱动模块共同组成。由OV5640摄像头采集图像,经过RGB转YCbCr模块完成颜色空间转换,为了配合帧差法的数据,将数据进行掩码然后经由DDR3控制器模块控制存入DDR3中,通过HDMI时序从DDR3中取出数据,此时取出的每个16bit数据同时包含了相邻两幅图像的灰度信息,高8位为第n帧图像的某个像素点灰度值,低8位为第n+1帧图像对应像素点的灰度值。图像处理模块将取出的数据进行预处理和帧差法计算得到运动目标的位置信息,追踪控制模块根据运动目标的位置相对于图像中心的偏移通过控制舵机转动来调整OV5640摄像头的方向完成追踪。摄像头使用黑金ALINX视频套餐中的OV5640摄像头;同套餐的还赠送一个屏幕,也非常适合学习视频处理的工程。舵机模块是使用的SC90,来完成摄像头的转动的,该模块看上去很简单,但是他和摄像头一起组合使用就非常炫酷!

2.算法设计

(一)项目简介与项目难点

首先FPGA的基础操作,以及Verilog基础语法就不再赘述。

项目简介在前面也已经讲说,这里只放一个整体框图来表现。这个框图为了便于大家理解已经进行了简化,大抵说白了就是将摄像头采集到的数据存起来,再把图像处理清晰,去除噪声。最后识别出在动的东西,把采集到的图像放在显示屏上,并标明哪个部分是正在运动的。

项目的难点:项目本身的难点在于驱动起来摄像头,一个类IIC协议接口的书写,以及对摄像头寄存器的配置。驱动SDRAM/DDR,将采集到的数据写进存储单元中。实现简单的图像处理算法来优化采集到的图像,识别物体的边缘。最后抓捕再显示出来,驱动VGA或HDMI接口将数据传输至显示屏上显示出来。

(二)整体流程

首先上电之后对各个模块的寄存器堆进行配置,计数器进行初始化。之后由OV5640摄像头采集图像,经过RGB转YCbCr模块完成颜色空间转换,为了配合帧差法的数据,将数据进行掩码然后经由DDR3控制器模块控制存入DDR3中,通过HDMI时序从DDR3中取出数据,此时取出的每个16bit数据同时包含了相邻两幅图像的灰度信息,高8位为第n帧图像的某个像素点灰度值,低8位为第n+1帧图像对应像素点的灰度值。图像处理模块将取出的数据进行预处理和帧差法计算得到运动目标的位置信息,追踪控制模块根据运动目标的位置相对于图像中心的偏移通过控制舵机转动来调整OV5640摄像头的方向完成追踪。

(三)算法基础

由于我们做的是一个图像,所以要对基础的图像算法进行简单学习。我们使用的算法主要有均值滤波,中值滤波,Sobel边缘检测及RGB转YCbCr。

1.均值滤波与中值滤波

首先何谓滤波?图像滤波,即在尽量保留图像细节特征的条件下对目标图像的噪声进行抑制,是图像预处理中不可缺少的操作,其处理效果的好坏将直接影响到后续图像处理和分析的有效性和可靠性。消除图像中的噪声成分叫作图像的平滑化或滤波操作。信号或图像的能量大部分集中在幅度谱的低频和中频段是很常见的,而在较高频段,感兴趣的信息经常被噪声淹没。因此一个能降低高频成分幅度的滤波器就能够减弱噪声的影响。

图像滤波的目的有两个:一是抽出对象的特征作为图像识别的特征模式;另一个是为适应图像处理的要求,消除图像数字化时所混入的噪声。

而对滤波处理的要求也有两条:一是不能损坏图像的轮廓及边缘等重要信息;二是使图像清晰视觉效果好。

而我们今天面对的主要为椒盐噪声,椒盐噪声是数字图像的一个常见噪声,就是在图像上随机出现黑色白色的像素。椒盐噪声是一种因为信号脉冲强度引起的噪声。RGB图像上,每一个像素点都是三段数字,分别对应R,G,B三种颜色在灰白图像中,椒盐噪声若果是黑点的话,就是指这一点的像素值明显低于周围像素点的值,而白点就是明显高于周围的像素值。而对于这种噪声,只要让他与周围的值相持平皆可以消除。中值滤波和均值滤波就是根据这种方法来消除,每个像素点周围都有8个像素,如果使用周围8个像素的平均值来代替这个像素点的像素值,就是均值滤波的基本方法;如果使用8个像素点的中值来代替这个像素点的像素值,就是中值滤波的基本方法。

要做这个处理,核心就是要搭建3x3矩阵。如何搭建3x3矩阵呢?我们有三种方法:

1.通过2个或者3个RAM的存储来实现3X3像素窗口;

2.通过2个或者3个FIFO的存储来实现3X3像素窗口;

3.通过2行或者3行Shift_RAM的存储来实现3X3像素窗口;

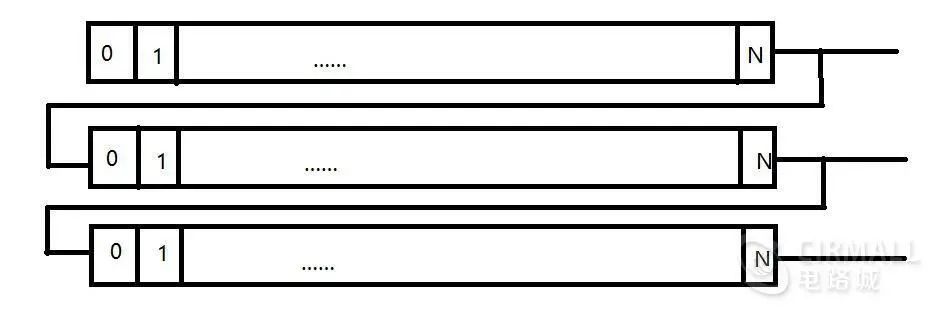

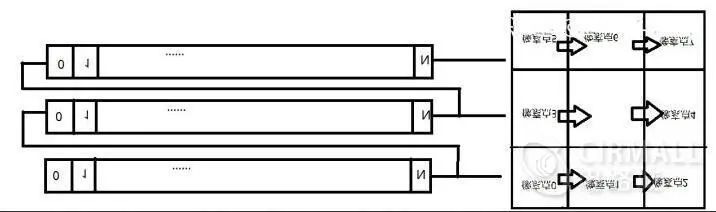

以shift_ram为例,shift_ram就是移位寄存器,如图:

左方数据输入,N是每行的像素点数,每行输出的就是要的矩阵。

2.Sobel边缘检测

在图像处理中,边缘是一幅图像中最基本的特征,每幅图像的边缘包含了用于识别的有用信息,是图像分析和模式识别的主要特征提取手段。在模式识别或进行其他的中,在很多方法来识别,其中一种方法就是识别出来图像边缘。在图像中,一幅图像的“临界”表示为图像上亮度显著变化的地方,边缘指的是一个区域的结束,也是另一个区域的开始。“边缘点”指的是图像中具有坐标[x,y],且处在强度显著变化的位置上的点。常用的边缘检测算法大多是以原始图像灰度值为基础,通过考察图像的每个像素的某个邻域内 灰度的变化,利用边缘一阶或二阶导数的规律来检测边缘。下图左边为原始的黑白灰度的图像,通过边缘检测算法后变成了右边的图像。

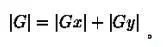

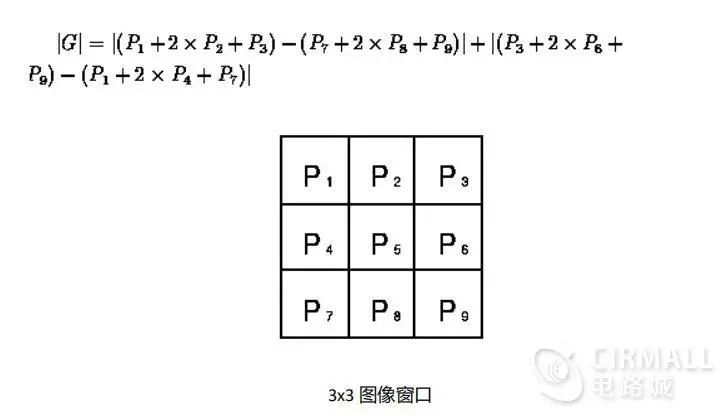

sobel 是一个梯度的计算,如下图所示,是 x 和 y 方向的 3x3 窗口的卷积。

使用算式

来计算目标点的卷积值:

这里注意一定是绝对值,要大于0。

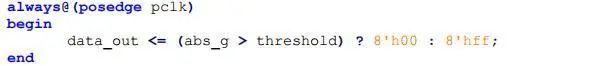

计算完成以后,要进行简单的二值化处理,将 sobel 值和阈值对比,产生黑白的二值化图像。将大于阈值设置为与背景色相反的图像。

利用此即可确定图像中各物体的边缘。

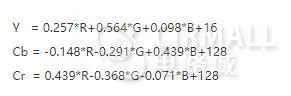

3. RGB转YCbCr

摄像头采集的RGB565格式数据为16比特,SDRAM不能同时将两帧RGB图像存储。因此在存入SDRAM前先将RGB格式转换为YCbCr格式并提取亮度分量作为灰度图像。YCbCr是通过有序的三元组来表示的,三元由Y(Luminance)、Cb(Chrominance-Blue)和Cr(Chrominance-Red)组成,其中Y表示颜色的明亮度和浓度,而Cb和Cr则分别表示颜色的蓝色浓度偏移量和红色浓度偏移量。人的肉眼对由YCbCr色彩空间编码的视频中的Y分量更敏感,而Cb和Cr的微小变化不会引起视觉上的不同,根据该原理,通过对Cb和Cr进行子采样来减小图像的数据量,使得图像对存储需求和传输带宽的要求大大降低,从而达到在完成图像压缩的同时也保证了视觉上几乎没有损失的效果,进而使得图像的传输速度更快,存储更加方便。我们要的到灰度图像,首先要将采集到的彩色图像转化为YCbCr。其转换公式如下:

……

-

FPGA

+关注

关注

1656文章

22299浏览量

630680 -

控制器

+关注

关注

114文章

17659浏览量

190424 -

控制模块

+关注

关注

2文章

144浏览量

19664

原文标题:《来实战》第4期:国内牛人用FPGA打造运动目标追踪系统(持续更新中......)

文章出处:【微信号:cirmall,微信公众号:电路设计技能】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

嵌入式和FPGA的区别

复杂的软件算法硬件IP核的实现

【开源FPGA硬件】硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......

如何在资源受限型应用中使用 FPGA

基于FPGA实现FOC算法之PWM模块设计

无位置传感器无刷直流电机的+FPGA+控制实现

基于Matlab与FPGA的双边滤波算法实现

基于FPGA的压缩算法加速实现

火爆开发中|开源FPGA硬件板卡,硬件第一期发布

Xilinx Ultrascale系列FPGA的时钟资源与架构解析

基于DBFP与DB-Attn的算法硬件协同优化方案

当我问DeepSeek AI爆发时代的FPGA是否重要?答案是......

数据中心中的FPGA硬件加速器

FPGA硬件资源与算法设计

FPGA硬件资源与算法设计

评论