什么是RAM?

RAM(Random Access Memory)中文是随机存取存储器。为什么要强调随机存储呢?因为在此之前,大部分的存储器都是顺序存储(Direct-Access),比较常见的如硬盘,光碟,老式的磁带,磁鼓存储器等等。随机存取存储器的特点是其访问数据的时间与数据存放在存储器中的物理位置无关。

RAM的另一个特点是易失性(Volatile),虽然业界也有非易失(non-volatile)的RAM,例如,利用电池来维持RAM中的数据等方法。

RAM主要的两种类别是SRAM(Static RAM)和DRAM(Dynamic RAM)。

SRAM和DRAM的区别

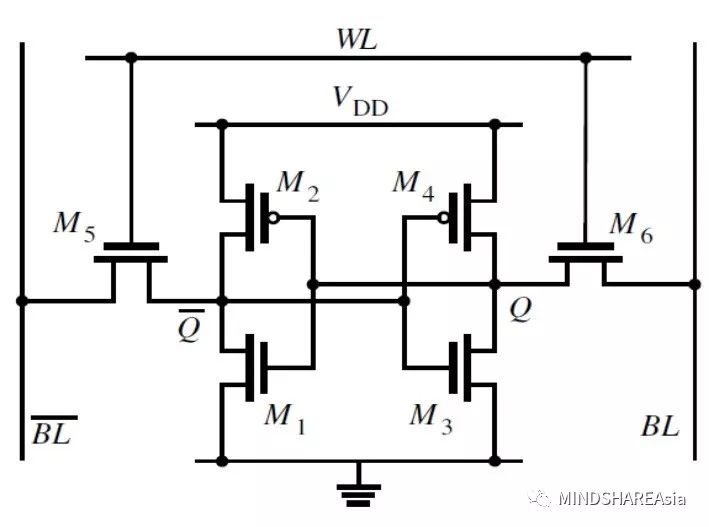

SRAM的S是Static的缩写,全称是静态随机存取存储器。而DRAM的D是Dynamic的缩写,全称是动态随机存取存储器。这两者有什么区别呢?首先我们看看SRAM的结构,你可以网上搜索一下有很多资料介绍SRAM的,比较出名的是6场效应管组成一个存储bit单元的结构:

工作原理相对比较简单,我们先看写0和写1操作。

写0操作

写0的时候,首先将BL输入0电平,(~BL)输入1电平。

然后,相应的Word Line(WL)选通,则M5和M6将会被打开。

0电平输入到M1和M2的G极控制端

1电平输入到M3和M4的G极控制端

因为M2是P型管,高电平截止,低电平导通。而M1则相反,高电平导通,低电平截止。

所以在0电平的作用下,M1将截止,M2将打开。(~Q)点将会稳定在高电平。

同样,M3和M4的控制端将会输入高电平,因NP管不同,M3将会导通,而M4将会截止。Q点将会稳定在低电平0。

最后,关闭M5和M6,内部M1,M2,M3和M4处在稳定状态,一个bit为0的数据就被锁存住了。

此时,在外部VDD不断电的情况下,这个内容将会一直保持。

下面通过动画来观察一下写0的过程。

写1操作

这里不再重复,大家可以自己推演一下过程。这里仍然提供写1过程动画。

读操作

读操作相对比较简单,只需要预充BL和(~BL)到某一高电平,然后打开M5和M6,再通过差分放大器就能够读出其中锁存的内容。

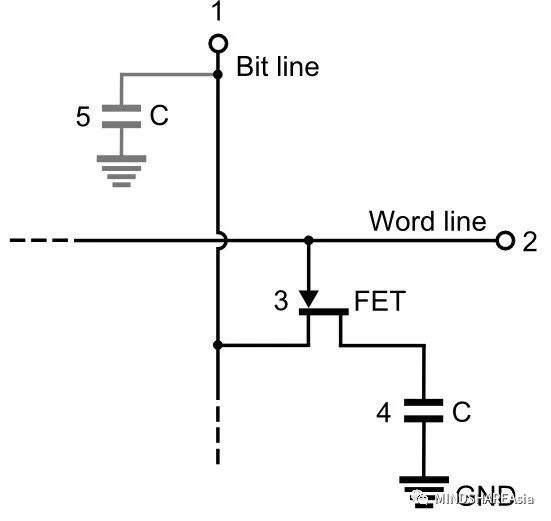

DRAM(Dynamic RAM)是指动态随机存取存储器。与SRAM最大的不同是,DRAM需要通过刷新操作来保持其存储的内容。让我们先来看看其一个bit存储单元(Cell)的结构:

其核心部件是4号位的电容C,这个电容大小在pF级别,用来存储0和1的内容。由于电容会慢慢放电,其保存的内容将会随时间推移而慢慢消失。为了保证其内容的完整性,我们需要把里面的内容定期读出来再填写回去。这个操作称为刷新操作(Refresh)。

其写操作相对简单:(我们以写1为例)

当需要写1的时候,先将BL(Bit Line)输入高电平1,然后选中对应的Word Line(同一时间将只有一根WL被选中),打开相应的MOS管,如图中所示3号位。此时,外部驱动能力很强,通过一定的时间,4号位的电容将会被充满。此时,关闭3号位的MOS管。内容1将在一定时间内被保存在4号位的电容中。写0的操作与之相反,不同的是将4号位电容中的电荷通过Bit Line放光。然后关闭3号位的MOS管,锁存相应数据。

而读操作相对来说,较为复杂。我们可以观察到4号位电容非常小,只有pF级别,而Bit Line往往都很长,上面挂了非常多个存储单元(cell),我们可以通过5号位的电容来表示。所以当我们直接把3号位的MOS管打开,Bit Line上将基本看不到什么变化。

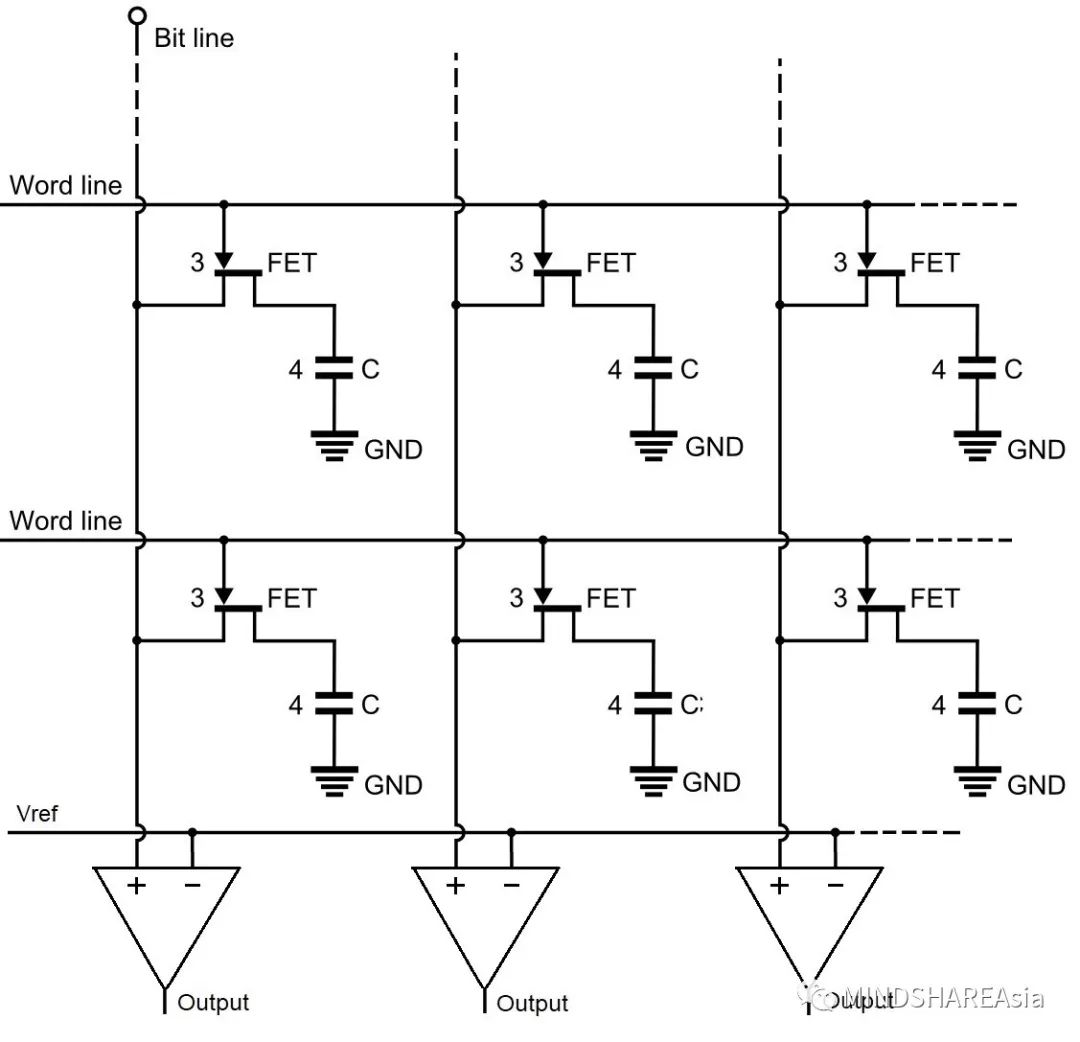

于是有人提出是否能够采用放大器来放大4号位电容的效果。结构图如下图所示:

我们可以定Vref为1/2的VDD电压,在读取电容里数据之前,我们先将所有Bit Line预充1/2 VDD的电压。然后,打开Word Line让选中的电容连接到Bit Line上面,如果原本的内容是1,则Bit line的总电压将会小幅攀升。否则,则会小幅下降。再通过差分放大器,将结果放大从而实现读操作。

这套方案是可以工作的,但Bit Line的数量不能太大。否则会导致距离Vref供电处较远的放大器Vref的值偏低,而导致差分放大器工作异常。同时,对于所谓的1/2 VDD预充,也存在不准的情况。

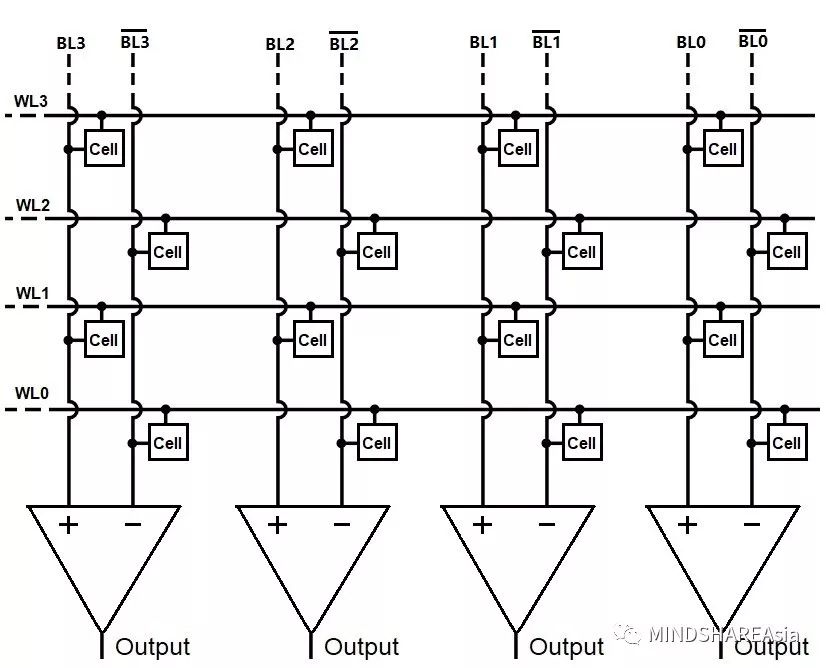

为了解决这个问题,有人提出,不如将原来的一根Bit Line设计成一对Bit Line,当其中一根Bit Line上的Cell被选中时,另一根Bit Line将不会有Cell被选中。从而没有Cell被选中的Bit Line可以充当放大器的Vref输入,其长度,负载以及寄生参数将会和另一根Bit Line十分一致,这样一来,放大器的工作就更加稳定了。结构图如下所示:

当读操作之前,我们先将1/2 VDD电压同时注入到BL和(~BL)上,这个动作被称为(pre-charge预充电)然后其中一根作为参考,来观察另一根Bit Line在某个Cell导通后的变化。

最后,我们总结一下区别:

SRAM成本比较高(6个场效应管组成一个存储单元)

DRAM成本较低(1个场效应管加一个电容)

SRAM存取速度比较快

DRAM存取速度较慢(电容充放电时间)

SRAM一般用在高速缓存中

DRAM一般用在内存条里

-

DRAM

+关注

关注

41文章

2402浏览量

189558 -

存储器

+关注

关注

39文章

7755浏览量

172176 -

sram

+关注

关注

6文章

833浏览量

117718

原文标题:终于!有人讲懂了DRAM和SRAM!

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

EMI高性能同步SRAM内存方案

sram存储器是什么,sram存储芯片选型要点

PSRAM与DRAM/SRAM相比的优势是什么?

低功耗串口SRAM外扩芯片型号有哪些

国产芯片伪SRAM存储器psram

并行sram芯片介绍,并行sram芯片应用场景

DRAM芯片选型,DRAM工作原理

SRAM和DRAM的区别

SRAM和DRAM的区别

评论