从1998年三星生产出最早的商用DDR SDRAM芯片到现在差不多已经过去20多年了,DRAM市场一直在发展,从DDR到DDR2,DDR3,DDR4,然后是即将进入市场的DDR5。今天我们来聊一下DDR的JEDEC规范。

什么是JEDEC?

JEDEC全称:JointElectron Device Engineering Council JEDEC是一个全球性的固态技术协会组织,理论上不隶属于任何一个国家或者政府实体,为半导体产业制定标准。包括很多方面,今天我们只关注DDR的相关规范。 DDR的开发是从1996年开始,对应JEDEC的规范 JESD79于2000年发布。JEDEC规范由两部分组成,一个是针对memory chip,另外一个是memory module。当然,随着RDIMM,LRDIMM的兴起,JEDEC相对应的制定出了RCD和Data Buffer的规范。我们今天主要聊JEDEC的SDRAM规范,也就是JESD79系列, 这里大家需要注意的是这个规范是针对DRAM芯片的,而不是内存条。有兴趣的同学可以去JEDEC网站上去下载相对应的规范,规范最后面的字母代表版本,比如JESD79-4C的C就代表目前针对DDR4 SDRAM的规范的版本是C。而JESD79后面的数字就代表了是DDR第几代。目前JEDEC网站上针对DDR5 SDRAM的规范还在制定当中,如果继续按照这个命名规律的话,应该是JESD79-5。

| Name | Doc |

| Double Date Rate (DDR) SDRAM | JESD79F |

| DDR2 SDRAM Specification | JESD79-2F |

| DDR3 SDRAM Standard | JESD79-3F |

| DDR4 SDRAM | JESD79-4C |

| DDR5: JEDEC DDR5 standard in currently in development | NA |

JEDEC的网站:www.jedec.org

下面这个表列举了JEDEC 规范从DDR到DDR5的主要变化,我们可以看到,为了配合整体行业对于性能,容量和省电的不断追求,规范的工作电压越来越低,芯片容量越来越大, IO的速率也越来越高。虽然目前DDR5的JEDEC规范还没有正式出台,但是我们可以从这个趋势以及现有网上的资料得到相同的结论。

|

Feature /Option |

DDR | DDR2 | DDR3 | DDR4 | DDR5* |

|

Voltage (VDDQ) |

2.5V | 1.8V | 1.5V | 1.2V | 1.1V |

|

Device Width |

x4, x8, x16 |

x4,x8, x16 |

x4, x8, x16 |

x4,x8, x16 |

x4, x8, x16 |

|

Die Density |

64Mb~ 1Gb |

128Mb~ 4Gb |

512Mb~ 8Gb |

2Gb~ 16Gb |

8Gb~ 64Gb |

|

Data Rates |

200~ 400MT/s |

400~ 800MT/s |

800~ 1600MT/s |

1600~ 3200MT/s |

3200~ 6400MT/s |

| Prefetch | 2n | 4n | 8n | 8n | 16n |

| Bank | 4 | up to 8 | 8 |

4banks pergroup |

2 or 4 banks per group |

|

Bank Group |

NA | NA | NA |

4 for x4/X8; 2 for x16; |

8 for x4/x8; 4 forx16; |

|

Burst Length |

2, 4 or 8 | 4 or 8 | 8 | 8 | 16 |

表 (一)

声明:目前DDR5的JEDEC标准还没有正式发布,因此这里所有的DDR5相关的数据来自于网上公开的数据,后续以JEDEC发布为准。同时,从DDR5开始,每根内存上有两个独立的通道。

从上面的表里面我们还可以看到,除了电压,容量和IO的速率变化之外,还列出了Bank,Bank Group,Prefetch和Burst Length的演进,bank数越来越多,到DDR4出现bank group,prefetch也从2n增加到4n,8n。那么这些变化之间有什么联系吗?DDR5又会有什么样的变化?要了解这些,我们需要回顾一下SDRAM的基本读写操作,以及DRAM的核心频率和IO频率。

Prefetch和burst length

虽然我们说现在DDR4的最大速率是3200MT/s, 但是这是指的DDR4的IO频率,即DDR4和memroy controller之间的接口数据传输速率。那么DRAM是怎么实现用比较低的核心传输频率来满足日益高涨的高速IO传输速率的需求呢?这就是靠prefetch来实现的。

| Prefetch |

Core Frequency |

IO CLK Frequency |

IO Data Rate |

|

| SDRAM | NA |

100-150 MHz |

100-150 MHz |

100-150 Mbps |

| DDR | 2 |

100-200 MHz |

100-200 MHz |

200-400 Mbps |

| DDR2 | 4 |

100-200 MHz |

200-400 MHz |

400-800 Mbps |

| DDR3 | 8 |

100-266 MHz |

400-1066 MHz |

800-2133 Mbps |

| DDR4 | 8 |

100-266 MHz |

800-1600 MHz |

1600-3200 Mbps |

| DDR5* | 16 |

100-266 MHz |

1600-3200 MHz |

3200-6400 Mbps |

表 (二)

从DDR开始到DDR3很好理解,Prefetch相当于DRAM core同时修了多条高速公路连到外面的IO口,来解决IO速率比内部核心速率快的问题,IO数据速率跟核心频率的倍数关系就是prefetch。那么这么一路增加prefetch,到了DDR4为什么不继续增加prefetch了呢?因为prefetch的增加对应的就是burst length的有可能相应增加。怎么理解prefetch和burst length之间的关系呢?Prefetch跟DRAM核心频率和IO频率之间的比例相关,而burst length的长度跟CPU的cache line大小有关。Burst length的长度有可能大于或者等于prefetch。但是如果prefetch的长度大于burst length的长度,就有可能造成数据浪费,因为CPU一次用不了那么多。所以从DDR3到DDR4,如果在保持DDR4内存data lane还是64的前提下,继续采用增加prefetch的方式来提高IO速率的话,一次prefetch取到的数据就会大于一个cache line的大小 (512bits),对于目前的CPU系统,反而会带来性能问题。那么DDR4是怎么解决的呢?

Bank Group

我们注意到在表一里面,到了DDR4出现了Bank Group,这就是DDR4在不改变prefetch的情况下,能继续提升IO速率的秘密武器。DDR4利用Bank group的interleave,实现IO速率在DDR3基础上进一步提升。

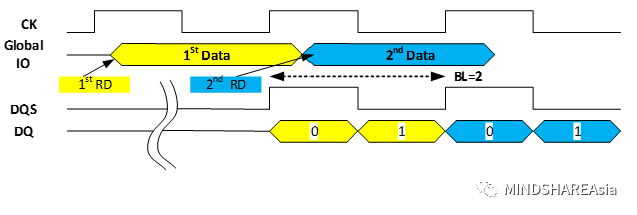

图一:DDR1

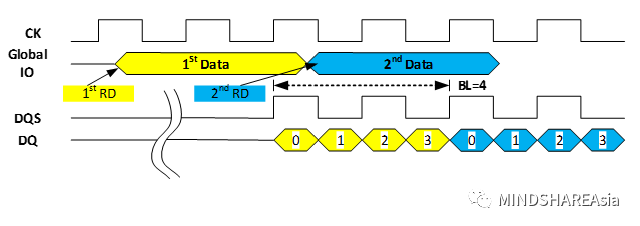

图二:DDR2

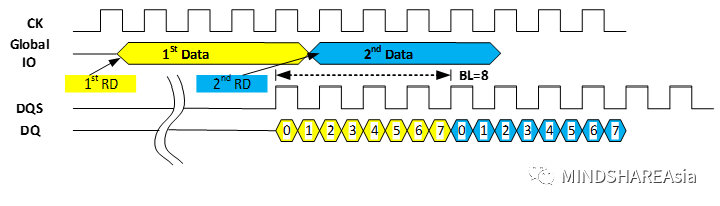

图三:DDR3

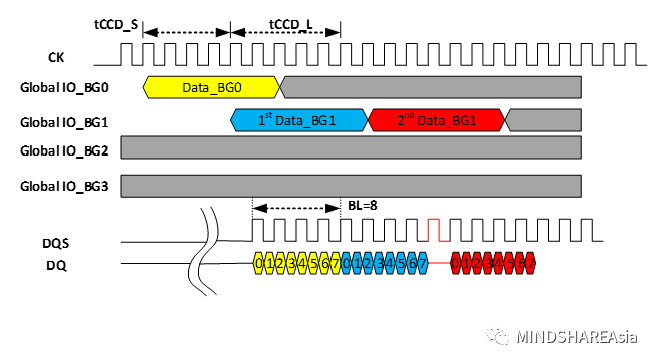

图四:DDR4

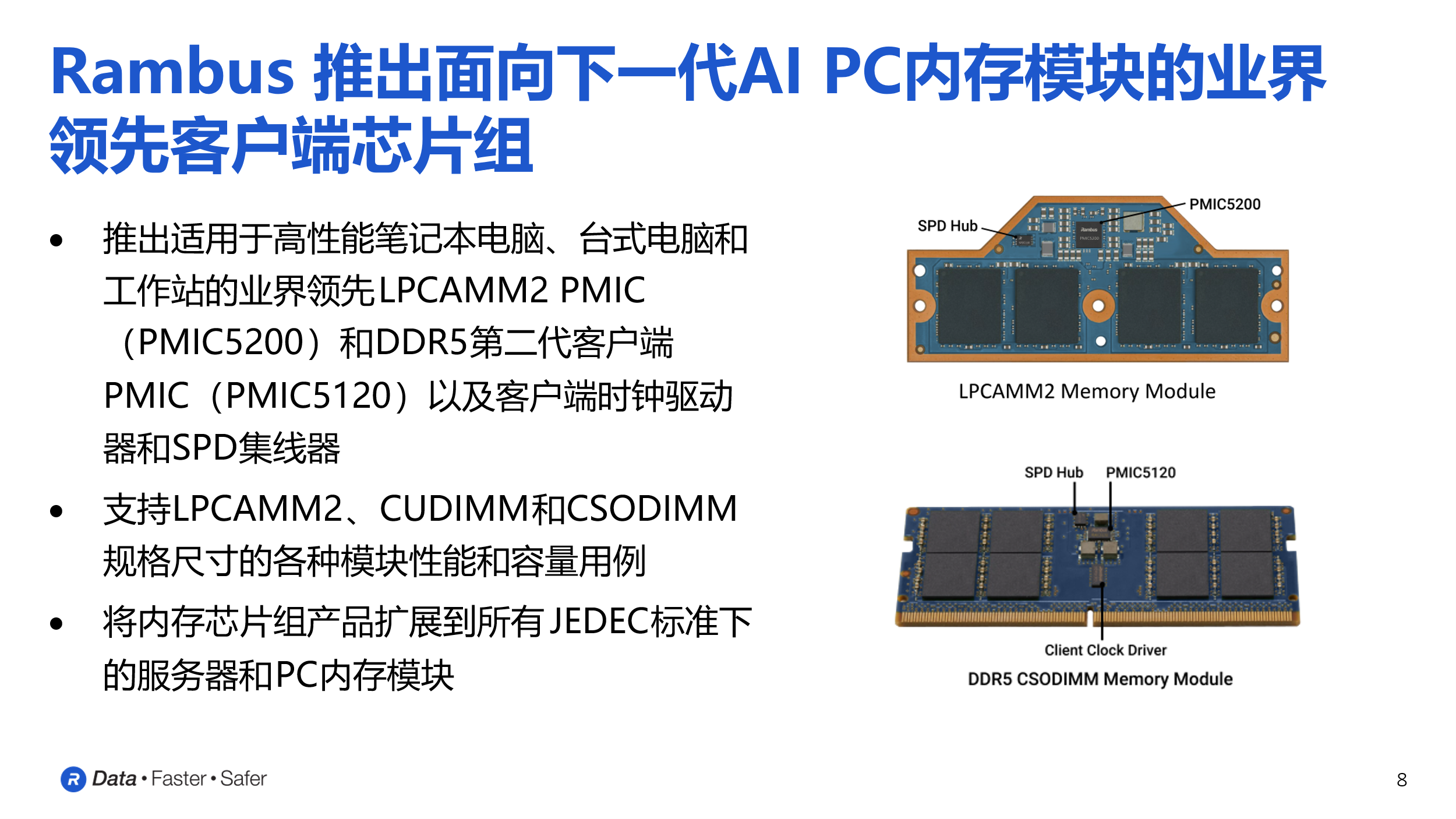

从上面的图四中可以看到,每个bank group有自己的global IO,这样就可以利用bank group的interleave来进一步解决内部速度和外部速度不匹配的问题。相当于在DDR3的基础上继续修了并行的相对比较慢的高速公路搭到外面的超高速单行道。 到了DDR5,我们还能继续利用Bank Group的interleave来实现提升IO速率的目的吗?如果继续这样做的话,对于速率提升的效果就很有限,所以到了DDR5还是走到了增加prefetch的方向。DDR5的prefetch是16,那么怎么解决我们前面提到的cache line大小的问题呢?DDR5采取的方式是减少DIMM data lane的数量,从64个data lane降低到32个data lane,从而继续保持64 Byte的cache line大小。 从以上JEDEC DDR到DDR4的发展历史,我们可以看到,DRAM的演进就是在为CPU系统架构服务的基础上,围绕着成本、降低电源消耗、加大容量、提高IO速率来不断演进。基于DRAM操作的原理,最大化的提高DRAM的使用率。因此,我们也可以看到DDR5提供了更多的bank数量和更加细化的refresh粒度等等,这些都是为了物尽其用,提高系统性能。我们在后续的文章中,会继续介绍DRAM的基本性能以及DDR5的新功能。

最后留给大家的问题:对于DDR4,bank group与group之间是tCCD_L还是tCCD_S?为什么?

-

半导体

+关注

关注

336文章

29983浏览量

258297 -

DDR

+关注

关注

11文章

747浏览量

68531 -

内存

+关注

关注

9文章

3173浏览量

76115

原文标题:来啦!DDR内存的前世、今生和未来!

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片装甲的前世今生

如何为蜂鸟添加DDR内存扩展

回收DDR内存芯片 收购DDR全新拆机带板

三大内存原厂或将于2025年停产DDR3/DDR4

不挑硬件,亲民之选,亦逍遥DDR5内存装机评测

德明利DDR5内存助力AI PC时代存储性能与市场增长

国产DDR5内存上市,内存市场价格战一触即发

量大管饱,亲民之选,神凝DDR5国风内存评测

安泰功率放大器应用:纳米材料的前世今生

TMS320DM644x DMSoC DDR2内存控制器用户指南

DDR内存的前世、今生和未来!

DDR内存的前世、今生和未来!

评论