最近,JEDEC固态存储协会正式公布了HBM技术第三版存储标准HBM2E,针脚带宽、总容量继续大幅提升。对于一些大企业,集成这些技术可以说不费吹灰之力,但不是谁都有这个实力。

Rambus今天就宣布了一套完整的HBM2E控制器+PHY物理层方案,可以帮助企业轻松用上HBM2E。

单个堆栈HBM2E系统架构图(俯视和侧视)

HBM2E标准支持每个堆栈最多12-Hi,针脚数据率最高3.2Gbps,使用1024-bit位宽的时候最大容量可以做到24GB,总带宽则是409.6GB/s。

如果是支持四堆栈的系统,位宽就是4096-bit,总容量将高达96GB,总带宽则是1.64TB/s。

目前,SK海力士、三星都已经完成了HBM2E产品开发,并投入生产,预计NVIDIA、AMD的下一代高端计算卡都会使用。

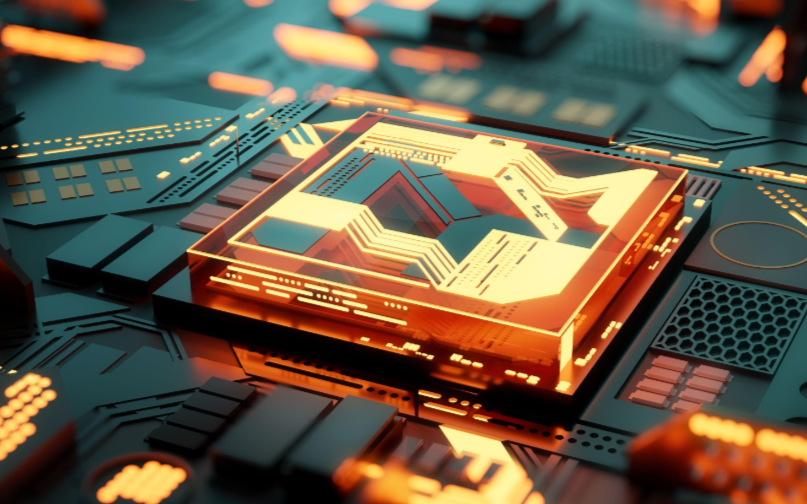

Rambus的方案完整支持上述标准,其控制器内核兼容DFI 3.1标准,并支持通过AXI、OCP和其他各种专用界面连接逻辑芯片。

HBM2E内存界面子系统示例图

厂商购买了该方案的授权之后,就可以获得将HBM2E内存与其逻辑芯片集成的所有资源,包括控制器的源代码。

如果企业技术实力有限,也可以由Rambus的工程师提供付费支持,但具体授权费用、支持费用均未公开。

责任编辑:wv

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储器

+关注

关注

39文章

7758浏览量

172217 -

Rambus

+关注

关注

0文章

68浏览量

19348

发布评论请先 登录

相关推荐

热点推荐

HBM迎头赶上!国产AI芯片飞跃

A800和H20之间。 根据报道,平头哥PPU采用HBM2e显存,单卡显存容量96GB,片间带宽为700GB/s,采用PCIe5.0×16通道接口,单卡功耗为400W。英伟达A800显存同样采用

Renesas RA2E1微控制器:低功耗与高性能的完美结合

Renesas RA2E1微控制器:低功耗与高性能的完美结合 在当今的电子设备设计领域,低功耗、高性能的微控制器是众多工程师追求的目标。Renesas RA2E1微

RA2E2微控制器:低功耗与高性能的完美结合

RA2E2微控制器:低功耗与高性能的完美结合 在当今的电子设备设计领域,低功耗、高性能的微控制器需求日益增长。Renesas的RA2E2系列微控制器

RA4E2微控制器:高性能与多功能的完美融合

的性能、丰富的外设以及出色的安全性,成为众多工程师的首选。今天,我们就来深入了解一下RA4E2系列微控制器的特点和优势。 文件下载: ra4e2.pdf

Renesas RA2E3微控制器:低功耗设计与高性能表现

Renesas RA2E3微控制器:低功耗设计与高性能表现 在电子工程师的日常工作中,选择一款合适的微控制器(MCU)至关重要。Renesas RA

RA8E2微控制器:高性能与多功能的完美结合

功能,为电子设计带来了更多可能性。 文件下载: ra8e2.pdf 一、RA8E2概述 RA8E2微控制器集成了多个基于Arm的32位核心系

RA0E2微控制器:低功耗与高性能的完美结合

。本文将深入剖析RA0E2系列微控制器的特点、电气特性以及实际应用中的注意事项。 文件下载: ra0e2.pdf 一、RA0E2概述 RA0

TLE8262 - 2E通用系统基础芯片HERMES数据手册解读

,为CAN - LIN汽车应用(如车身控制器、网关应用)提供了全面的解决方案。本文将深入解读TLE8262 - 2E的数据手册,帮助电子工程师更好地了解和应用这款芯片。 文件下载

DP83867E/IS/CS:高性能以太网物理层收发器的技术剖析与应用实践

DP83867E/IS/CS:高性能以太网物理层收发器的技术剖析与应用实践 在当今高速发展的网络通信领域,以太网物理层收发器扮演着至关重要的

Renesas RA4E2微控制器:特性与设计要点解析

微控制器.pdf 一、RA4E2概述 RA4E2 Group采用了Arm® Cortex® - M33核心,最高运行频率可达100 MHz,具备高达128 KB的代码闪存、

深度剖析RA2E3微控制器:特性、电气参数与应用考量

深度剖析RA2E3微控制器:特性、电气参数与应用考量 在当今电子设备小型化、低功耗化的趋势下,微控制器的性能和特性愈发关键。RA2E3作为一

RA0E2微控制器:低功耗设计的理想之选

。今天,我们就来深入了解一下RA0E2微控制器的详细信息。 文件下载: Renesas Electronics RA0E2通用微控制器 (M

DP83867E/IS/CS以太网物理层收发器:特性与设计要点详解

DP83867E/IS/CS以太网物理层收发器:特性与设计要点详解 在如今这个数据驱动的时代,以太网通信在各个领域都扮演着至关重要的角色。DP83867E/IS/CS作为

Cadence推出HBM4 12.8Gbps IP内存系统解决方案

需求。Cadence HBM4 解决方案符合 JEDEC 的内存规范 JESD270-4,与前一代 HBM3E IP 产品相比,内存带宽翻了一

Rambus宣布一套完整的HBM2E控制器+PHY物理层方案 可帮助企业轻松用上HBM2E

Rambus宣布一套完整的HBM2E控制器+PHY物理层方案 可帮助企业轻松用上HBM2E

评论