AMD在7nm Zen2架构锐龙处理器上使用了chiplets小芯片设计,这是AMD的一大创举,使得制造64核128线程处理器更加简单,这一实现也是几何AMD多个团队的功劳。

那这种设计到底能带来什么好处呢?在日前的ISSCC大会上,AMD公布了一些数据,对比了7nm Zen2在不同核心配置下的成本数据。

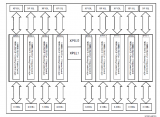

首先来看桌面版的,如果将16核32线程的锐龙3代作为100%基准,那么采用原生核心的16核处理器成本将超过2,至少是两倍的成本。

如果是EPYC霄龙处理器,那么核心数越多,成本优势就越明显,64核7nm锐龙作为基准的话,那么48核的成本就是0.9,而原生48核设计的成本至少是1.9,依然是两倍水平。

当然,随着核心数的减少,成本收益也会下滑,桌面8核的成本就跟原生核心设计差不多了,16核及以上才会有比较明显的成本降低。

AMD上月底在ISSCC 2020大会上公布了64核小芯片设计的秘密,其中AMD在最后一页感谢了全球研发团队的贡献,分别提到了奥斯汀(Austin)、班加罗尔、波斯顿、柯林斯堡Fort Collins、海得拉巴、万锦市、圣克拉拉及上海等地。

这其中,奥斯汀是AMD原来的总部,也是研发团队的核心,班加罗尔、海得拉巴是印度的,万锦市是加拿大的,上海是中国的,圣克拉拉是现在的AMD总部。

由此可见,现代CPU之复杂,不是一两个团队就能搞定的,AMD这样的公司都需要全球多个团队协力。

-

处理器

+关注

关注

68文章

20332浏览量

254919 -

amd

+关注

关注

25文章

5707浏览量

140404 -

cpu

+关注

关注

68文章

11327浏览量

225880

发布评论请先 登录

绕开先进制程卡脖子:2026先进封装成中国AI芯片自主突围关键一战

重磅研究:7nm FinFET 性能优化的隐藏密码 —— 栅极与鳍片间距调控

AMD即将亮相ISE 2026

三星发布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

强强联手 | AMD嵌入式高层一行访问ALINX,深化2026战略合作前沿技术布局

“汽车智能化” 和 “家电高端化”

国产AI芯片真能扛住“算力内卷”?海思昇腾的这波操作藏了多少细节?

AMD 7nm Versal系列器件NoC的使用及注意事项

全球首款2nm芯片被曝准备量产 三星Exynos 2600

一文详解Advanced IO wizard异步模式

芯动科技独家推出28nm/22nm LPDDR5/4 IP

基于AMD Versal器件实现PCIe5 DMA功能

八天三次收购!AMD收购AI芯片制造商Untether AI团队,刺激创新

如何使用多个miniprog4对多个CCG7x设备进行编程?

AMD实现首个基于台积电N2制程的硅片里程碑

AMD的7nm Zen2是全球多个团队协力设计的

AMD的7nm Zen2是全球多个团队协力设计的

评论