近日,中科院对外宣布,中国科学家研发出了新型垂直纳米环栅晶体管,这种新型晶体管被视为2nm及一下工艺的主要技术候选。这意味着此项技术成熟后,国产2nm芯片有望成功“破冰”,意义重大。

目前最为先进的芯片制造技术为7nm+Euv工艺制程,比较出名的就是华为的麒麟990 5G芯片,内置了超过100亿个晶体管。麒麟990首次将将5G Modem集成到SoC上,也是全球首款集成5G Soc,技术上的确实现了巨大突破,也是国产芯片里程碑式的意义。

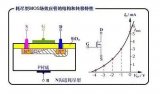

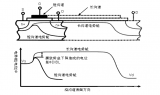

而继华为之后,中科院研发出了2nm及以下工艺所需要的新型晶体管——叠层垂直纳米环栅晶体管。据悉,早在2016年官方就开始针对此类技术开展相关研究,历经重重困难,中科院斩获全球第一,研发出世界上首个具有自对准栅极的叠层垂直纳米环栅晶体管。

同时这一专利还获得了多项发明专利授权,中科院的这项研究成果意义很大,这种新型垂直纳米环栅晶体管被视为2nm及以下工艺的主要技术候选,可能对国产芯片制造有巨大推动作用。如今在美国企业的逼迫下,国产企业推进自主可控已成为主流意识,市场空间将被进一步打开。相信在5年的时间内,在技术方面将实现全面突破。切断对于华为的技术提供,这将是中国整体研发芯片的一个里程碑式转折,中国将不再过于依赖美国所提供的相关芯片及其技术。

责任编辑:wv

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54411浏览量

469151 -

晶体管

+关注

关注

78文章

10439浏览量

148576

发布评论请先 登录

相关推荐

热点推荐

国产来袭!2nm AI GPU?

的时间和成本内实现。 近日,据媒体报道,上海棣山科技有限公司(以下简称“棣山科技”)对外披露其2nm高端AI GPU芯片最新研发进展。据悉,该公司自主攻关的这款芯片已达到国际前沿设

2nm“诸神之战”打响!性能飙升+功耗骤降,台积电携联发科领跑

电子发烧友网报道(文/莫婷婷)2025年,2nm制程正式开启全球半导体“诸神之战”。就在近期,MediaTek(联发科)宣布,首款采用台积电 2 纳米制程的旗舰系统单芯片(SoC)已成

三星发布Exynos 2600,全球首款2nm SoC,NPU性能提升113%

电子发烧友网综合报道 近日,三星电子正式发布其手机芯片Exynos 2600。这款芯片意义非凡,它不仅是三星首款2nm芯片,更是全球首款采用2

三星公布首批2纳米芯片性能数据

三星公布了即将推出的首代2nm芯片性能数据;据悉,2nm工艺采用的是全栅极环绕(GAA)晶体管技术,相比第二代3nm工艺,性能提升5%,功耗

台积电2纳米制程试产成功,AI、5G、汽车芯片,谁将率先受益?

与现行的3nm工艺相比,台积电在2nm制程上首次采用了GAA(Gate-All-Around,环绕栅极)晶体管架构。这种全新的结构能够让晶体管电流控制更加精确,减少漏电问题,大幅提升

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

传统的平面场效应晶体管开始,经鳍式场效应晶体管、纳米片全环绕栅极场效应晶体管,向下一代叉形片和互补场效应晶体管发展,见图1和图

发表于 09-06 10:37

全球首款2nm芯片被曝准备量产 三星Exynos 2600

据外媒韩国媒体 ETNews 在9 月 2 日发文报道称全球首款2nm芯片被曝准备量产;三星公司已确认 Exynos 2600 将成为全球首款采用 2nm 工艺的移动 SoC

下一代高速芯片晶体管解制造问题解决了!

在半导体工艺演进到2nm,1nm甚至0.7nm等节点以后,晶体管结构该如何演进?2017年,imec推出了叉片晶体管(forksheet),

发表于 06-20 10:40

台积电2nm良率超 90%!苹果等巨头抢单

当行业还在热议3nm工艺量产进展时,台积电已经悄悄把2nm技术推到了关键门槛!据《经济日报》报道,台积电2nm芯片良品率已突破 90%,实现重大技术飞跃!

无结场效应晶体管详解

当代所有的集成电路芯片都是由PN结或肖特基势垒结所构成:双极结型晶体管(BJT)包含两个背靠背的PN 结,MOSFET也是如此。结型场效应晶体管(JFET) 垂直于沟道方向有一个 PN

我国研发出新型垂直纳米环栅晶体管 国产2nm芯片有望

我国研发出新型垂直纳米环栅晶体管 国产2nm芯片有望

评论