文章来源:半导体与物理

原文作者:jjfly686

本文主要讲述芯片制造中的晕环注入。

当晶体管栅长缩至20纳米以下,源漏极间可能形成隐秘的电流通道,导致晶体管无法关闭。而晕环注入(Halo Implant)技术,正是工程师们设计的原子级“结界”,将漏电流牢牢封锁在沟道之外。

一、穿通效应:纳米晶体管的“幽灵通道”

问题的根源:耗尽区的失控扩张

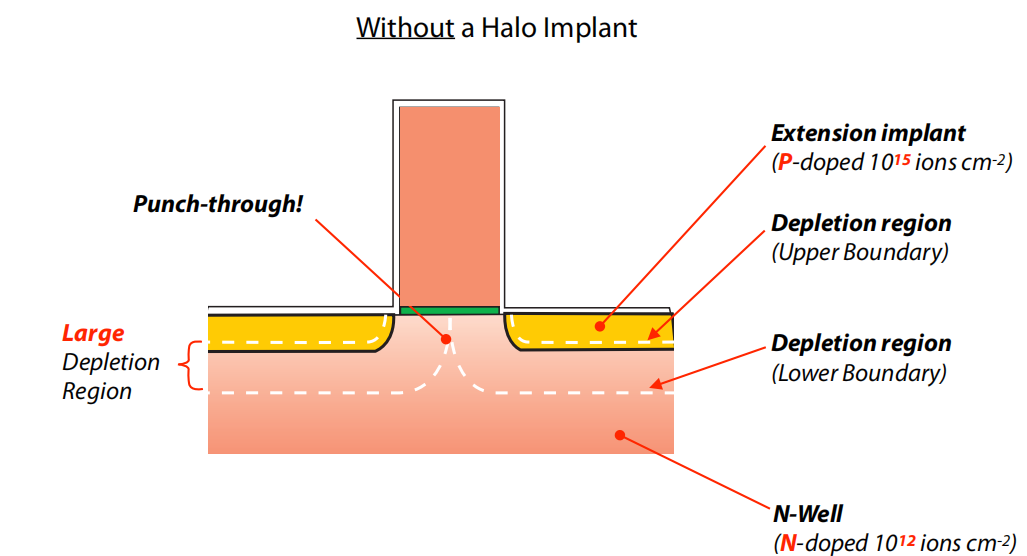

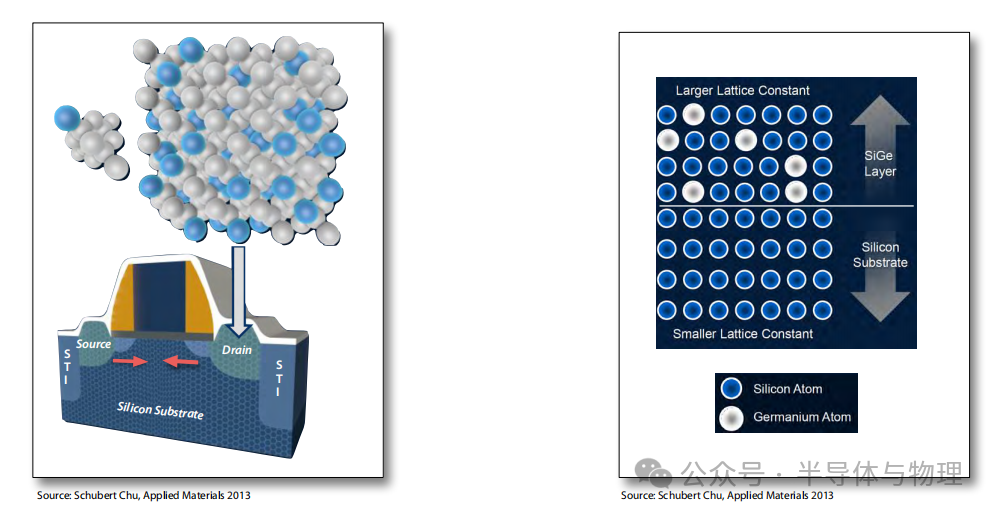

每个PN结交界处都存在耗尽区——一个缺乏自由载流子的绝缘区域(如图1)。当源极(P⁺延伸注入)与漏极(N⁺延伸注入)之间的耗尽区相连时,就会形成穿通通道:传统结构(无晕环注入):轻掺杂N阱(10¹² ions/cm²)对抗重掺杂P⁺延伸区(10¹⁵ ions/cm²);耗尽区向N阱深处大幅延伸(深度可达100 nm);栅长<20 nm时,源漏耗尽区相接,电子直接隧穿。结果:晶体管在关闭状态漏电,功耗飙升甚至烧毁芯片。

二、晕环注入:原子级的“耗尽区牢笼”

技术原理:不对称掺杂的巧思

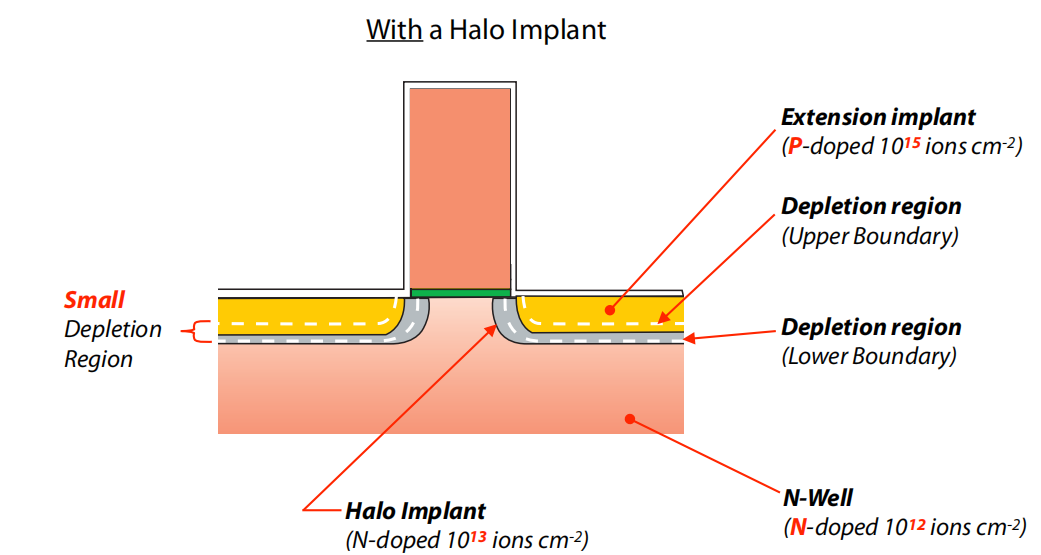

晕环注入通过在沟道边缘植入高浓度反型掺杂原子,构建局部电荷屏障:

注入位置:仅位于栅极边缘正下方(深度约20 nm),避开沟道中心;

掺杂设计:

| 区域 | 掺杂类型 | 浓度 (ions/cm²) | 作用 |

|---|---|---|---|

| P⁺延伸区 | 硼 | 10¹⁵ | 形成源/漏极 |

| N阱 | 磷 | 10¹² | 晶体管基底 |

| 晕环区 | 磷 | 10¹³ | 封锁耗尽区扩张 |

晕环的额外电荷(10¹³ ions/cm²)中和P⁺区的空穴电荷,将耗尽区深度压缩70%(从100 nm→30 nm);

由于晕环仅存在于栅极边缘,沟道中心载流子迁移率不受影响。

工艺四步

栅极侧墙形成:沉积氮化硅并刻蚀,定义注入窗口;

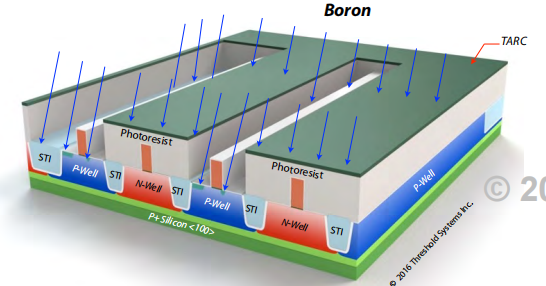

倾斜离子注入:晶圆倾斜25-45°,磷离子以50 keV能量注入;

退火激活:纳秒激光局部加热,避免掺杂扩散;

延伸注入同步:垂直注入硼形成源漏延伸区。

-

晶体管

+关注

关注

78文章

10439浏览量

148576 -

芯片制造

+关注

关注

11文章

735浏览量

30529 -

PN结

+关注

关注

8文章

498浏览量

51907

原文标题:芯片制造:晕环注入

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片制造中的晕环注入技术

芯片制造中的晕环注入技术

评论