一、DIP的测试点:TOP的测试点,TOP要裸铜,在Layout 里面加上SolderMask 这一层(即PCB厂所说的开窗),BOT要盖绿漆,在Layout 里面不需要SolderMask这一层,(即PCB厂所说的不开窗,MASK住)。BOT测试点的设置则相反。

二、测试点不能离零件太近,因为零件有一定的高度,离太近零件上了之后顶针顶不到。

三、POWERPCB中加测试点SOLDMASK的处理

1.以TPVIA-TOP的测试点为例:

这是一个DIP的TOP测试点,如果我们想把TOP的SOLDMASK做到42,BOT的SOLDMASK不做让它盖绿漆,那么我们只需在Soldermask Top层只需设成32就可以了(如上图所示),因为出GERBER时它系统所设的SOLDMASK都会在此基础上加10MIL

当然,此项设定也要按要求自己修改,而BOT要盖绿漆,不用设,则默认为0MIL。

2.出GERBER时设定要作修改不能以系统默认的为准,格式如下:

在TOP层选择PAD,TESTPOINT;

在SOLDMASK 选择LINE,VIA,COPPER,TEXT,TESTPOINT,

3.如果测试点除了以VIA的形式出现外,还有以零件的形式出现,那么这些以零件形式出现的测试点该如何设置它的SOLDERMASK呢?

在PAD里面加SOLDERMASK是没有用的,因为TOP层出GERBER有选PAD,始终以这个尺寸去加系统所设的SOLDMASK为准。

NOTE:

SOLDMASK 选择VIA。因为测试点是以VIA的形式存在的。而TOP层出GERBER选择PAD则会按我们所设的自动在MASK层加10mil。

四、测试点设置

Name: 75是指探针到探针的中心距离,Fixture Drill: 16是指实际探针的SIZE,那么Probe to Probe的间距应设为:75-16=59,即在检查DRC的时候是以所设的Fixture Drill为标准,而不是以实际的TEST PAD SIZE为标准。

责任编辑:ct

-

pcb

+关注

关注

4417文章

23962浏览量

426096 -

华强pcb线路板打样

+关注

关注

5文章

14629浏览量

44706

发布评论请先 登录

11:如何在 Allegro 中添加自定义的测试点 I Allegro PCB 设计小诀窍

08. 如何在 Allegro中设置禁止添加测试点区域?| 芯巧Allegro PCB 设计小诀窍

物镜搭配筒镜使用时需要注意什么

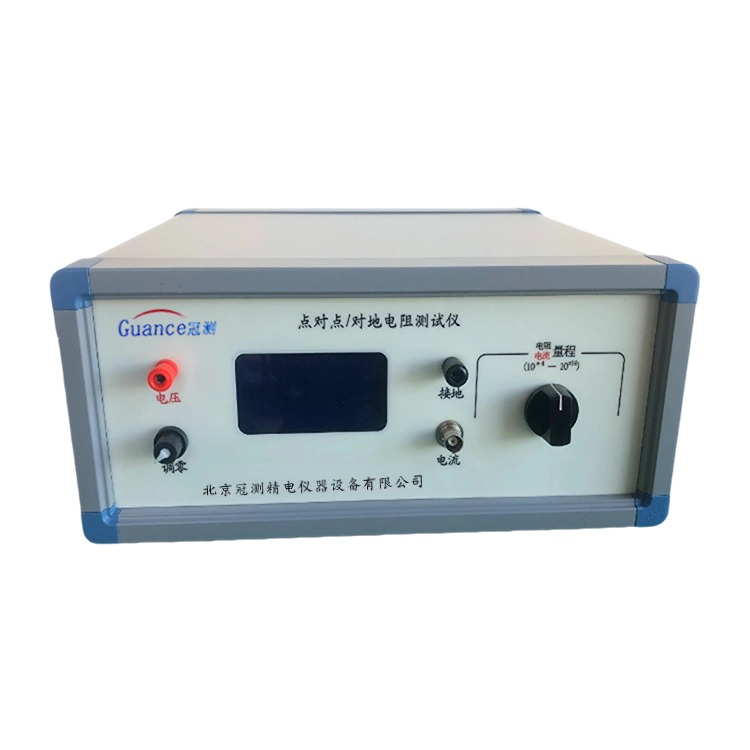

测试点氧化或污浊时的应急技巧:点对点对地电阻测试如何获得真实数据

企业选择SDWAN方案时,需要注意哪些?

PCB板上加测试点需要注意哪一些

PCB板上加测试点需要注意哪一些

评论