2006年前英特尔高级副总裁帕特·基尔辛格说:“今天,光学是一个非常小的细分技术,明天,它将成为我们制造每一个芯片的主流。” 事实上,光互连对于内部和数据中心之间的高速通信是非常重要的。

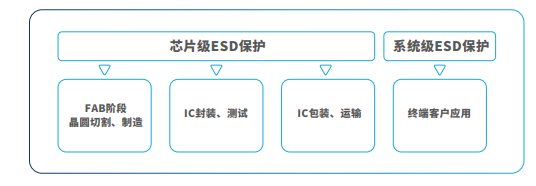

最近公司接触的项目中,因为所有其他功都能高度集成在一个CMOS芯片上,外部只需要激光二极管。为了让CMOS高速通信芯片和激光二极管之间实现高速通信,片上ESD(静电保护)保护的寄生电容必须尽可能的小。在过去5年当中,公司在不同的光互联项目中,一直使用公司自创的TAKE CHARGE 工具,得到了很好的结果。当通用的或者半导体厂的在片ESD不符合您的需求时,采用公司的TAKE CHARGE是非常理智的选择。因为,TAKE CHARGE在数千个IC商业应用芯片上已经证明,它能提供一个快速,可靠的方式来平衡ESD保护与成本之间的关系,同时发挥最大的IC性能。

设计无约束

保护接口与最敏感的节点,如GATE,核心器件等

高速电路的低寄生电容

200fF,100fF甚至低于15fF

缩短几个月量产和上市的时间

现有低寄生电容可用的on-chip ESD 解决方案ESD

TSMC: 180nm down to 28nm

UMC: 130nm, 65nm, 28nm

GF: 65nm

SMIC: 40nm

Several other foundries, …

针对其他技术节点或者半导体厂的私人定制EOS / ESD解决方案,可在几天内交货

大幅降低IC成本

已经在硅产品上被证明的ESD解决方案有助于降低IC开发成本和时

兼容所有的标准工艺流程

已经和欧洲,美国的大客户在光互连项目方面取得很多合作和经验

公司所有合作的客户:

如果你在硅光电这块或者高速电路这块有涉足,那么公司的on-chip ESD 解决方案,会给贵公司产品带来更多的附加价值。

-

半导体

+关注

关注

339文章

31192浏览量

266320 -

硅光电

+关注

关注

0文章

5浏览量

7564 -

高速电路

+关注

关注

8文章

170浏览量

24917

发布评论请先 登录

ESD 3D打印材料全面说明:PETG-ESD、ABS-ESD、PC-ESD对比

探索AFBR - S4N44P164M 4×4 NUV - MT硅光电倍增管阵列的卓越性能

探索AFBR - S4N44P044M 2×2 NUV - MT硅光电倍增管阵列的卓越性能

探索AFBR - S4N22P014M NUV - MT硅光电倍增管阵列的卓越性能

探索Broadcom AFBR - S4P11P012R近红外双通道硅光电倍增管

探索Broadcom HLPT-B3x0-00000硅NPN光电晶体管的卓越性能

探索ESD7424:超低电容ESD保护二极管的卓越性能

ESD测试的详细解释

带宽7.2Tb/s!海思光电推出HI-ONE硅光引擎

传感器走向“AI on-chip”与低功耗集成化

聚智姑苏,共筑硅基光电子产业新篇 — “硅基光电子技术及应用”暑期学校圆满落幕!

在ModusToolbox2.3下,基于BTSDK3.1开发cyw20719b2程序,是否可以像wiced studio一样设置?

概伦电子芯片级HBM静电防护分析平台ESDi介绍

关于硅光电应用下的on-chip ESD的性能分析和介绍

关于硅光电应用下的on-chip ESD的性能分析和介绍

评论