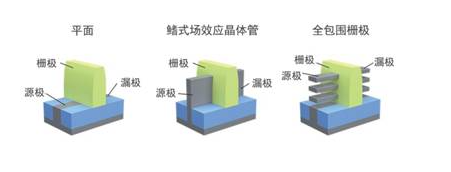

在22nm,或许是16nm节点,我们将需要全新的晶体管。而在这其中,争论的焦点在于究竟该采用哪一种技术。这场比赛将关乎到晶体管的重新定义。在22/20nm逻辑制程的开发中,业界都争先

2012-03-06 10:08:16 2292

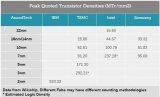

2292 3nm工艺,外媒的报道显示,台积电是计划每平方毫米集成2.5亿个晶体管。 作为参考,采用台积电7nmEUV工艺的麒麟9905G尺寸113.31mm2,晶体管密度103亿,平均下来是0.9亿/mm2,3nm工艺晶体管密度是7nm的3.6倍。这个密度形象化比喻一下,就是将奔腾4处理器缩小到

2020-04-20 11:27:49 5155

5155 研究机构IMEC已经发表了一篇论文,该研究表明,在5nm节点上,STT-MRAM与SRAM相比可以为缓存提供节能效果。这种优势比非易失性和较小的空间占用更重要。

2019-10-18 06:01:42

的B和C对称、和E极同样是N型。也就是说,逆接C、E也同样有晶体管的功效。即电流由E→C流动。3. 逆向晶体管有如下特点。hFE低(正向约10%以下)耐压低 (7 to 8V 与VEBO一样低)↑通用

2019-04-09 21:27:24

晶体管之间的差异性:就三极管,mos管和可控硅之间的差别和相同点的相关概念有点模糊,请各位大侠指点!!!

2016-06-07 23:27:44

晶体管分类 按半导体材料和极性分类 按晶体管使用的半导体材料可分为硅材料晶体管和锗材料晶体管。按晶体管的极性可分为锗NPN型晶体管、锗PNP晶体管、硅NPN型晶体管和硅PNP型晶体管。 按结构

2010-08-12 13:59:33

电路为电流放大倍数hFE=200的晶体管开关电路,试计算当5V的电压连接着100Ω的电阻加载到集电极(晶体管处于饱和状态)时的基极电流IB。这里,基极电流的富裕度为5倍。答案在原文章中。

2017-03-28 15:54:24

孔,按动相应的V(BR)键,再从表中读出反向击穿电压值。对于反向击穿电压低于50V的晶体管,也可用图5-58中所示的电路进行测试。将待测晶体管VT的集电极C、发射极E与测试电路的A端、B端相连(PNP

2012-04-26 17:06:32

晶体管测量模块的基本特性有哪些?晶体管测量模块的基本功能有哪些?

2021-09-24 07:37:23

`非常不错的晶体管电路设计书籍!`

2016-11-08 14:12:33

或使其特性变坏。(5) 集电极--发射极反向电流ICEOICEO是指晶体管基极开路时,集电极、发射极间的反向电流,也称穿透电流。ICEO越小越好,现在应用较多的硅晶体管,其ICEO都很小,在1A以下

2018-06-13 09:12:21

晶体管的主要参数有哪些?晶体管的开关电路是怎样的?

2021-06-07 06:25:09

本文为大家介绍“Si晶体管”(之所以前面加个Si,是因为还有其他的晶体管,例如SiC)。 虽然统称为“Si晶体管”,但根据制造工艺和结构,还可分为“双极”、“MOSFET”等种类。另外,还可根据处理

2020-06-09 07:34:33

本篇开始将为大家介绍“Si晶体管”。虽然统称为“Si晶体管”,不过根据制造工艺和结构,还可分为“双极”、“MOSFET”等种类。另外,还可根据处理的电流、电压和应用进行分类。下面以“功率元器件”为主

2018-11-28 14:29:28

即是内置了电阻的晶体管。数字晶体管有诸多优点如:1. 安装面积减少 2. 安装时间减 3. 部件数量减少 等等。数字晶体管是ROHM的专利。内置电阻的晶体管是由ROHM最早开发并取得专利的。5. 基极

2019-05-05 00:52:40

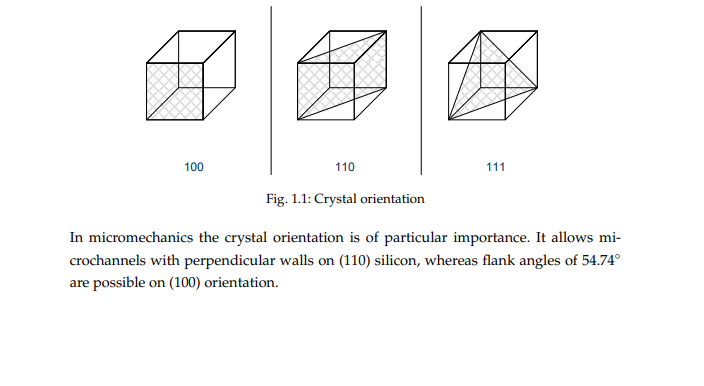

1.晶体管的结构晶体管内部由两PN结构成,其三个电极分别为集电极(用字母C或c表示),基极(用字母B或b表示)和发射极(用字母E或e表示)。如图5-4所示,晶体管的两个PN结分别称为集电结(C、B极

2013-08-17 14:24:32

型号的晶体管。 5.开关三极管的选用小电流开关电路和驱动电路中使用的开关晶体管,其最高反向电压低于100V,耗散功率低于1W,最大集电极电流小于1A,可选用3CK3、3DK4、3DK9、3DK12等

2012-01-28 11:27:38

的B和C对称、和E极同样是N型。也就是说,逆接C、E也同样有晶体管的功效。即电流由E→C流动。3. 逆向晶体管有如下特点。hFE低(正向约10%以下)耐压低 (7 to 8V 与VEBO一样低)↑通用

2019-05-09 23:12:18

晶体管 &

2010-08-12 13:57:39

IB3042-5晶体管产品介绍IB3042-5报价IB3042-5代理IB3042-5咨询热IB3042-5现货,李先生 深圳市首质诚科技有限公司,Integra Technologies公司成立

2019-05-14 11:00:13

`产品型号:IB3042-5产品名称:晶体管Integra于1997年由一些企业工程师发起,他们相信他们可以为新一代雷达系统设计人员提供创新的高性能RF功率晶体管解决方案。我们推向市场的款产品是采用

2019-04-15 15:12:37

产生的噪声更少。它比其他晶体管小,可以像其他晶体管一样用于集成电路。X. 如何识别PNP晶体管PNP晶体管通常通过其结构来识别。在比较NPN和PNP晶体管的结构时,我们看到了各种差异。识别PNP晶体管

2023-02-03 09:44:48

晶体管(transistor)是一种固体半导体器件,可以用于检波、整流、放大、开关、稳压、信号调制和许多其它功能

2010-08-13 11:36:51

multisim仿真中高频晶体管BFG35能用哪个晶体管来代替,MFR151管子能用哪个来代替?或是谁有这两个高频管子的原件库?求大神指教

2016-10-26 11:51:18

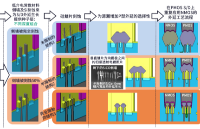

在半导体工艺演进到2nm,1nm甚至0.7nm等节点以后,晶体管结构该如何演进?2017年,imec推出了叉片晶体管(forksheet),作为环栅(GAA)晶体管的自然延伸。不过,产业对其可制造

2025-06-20 10:40:07

互补晶体管的匹配

2019-10-30 09:02:03

晶体管的工作原理是一样的。》 光电晶体管光电晶体管是由双极晶体管或场效应晶体管组成的光电器件。光被吸收在这种器件的有源区域,产生光生载流子,这些载流子通过内部电放大机制并产生光电流增益。光电晶体管在三

2023-02-03 09:36:05

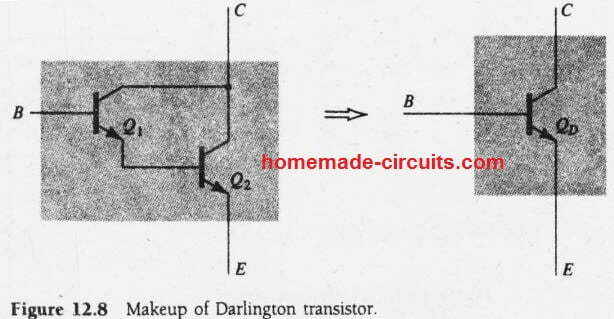

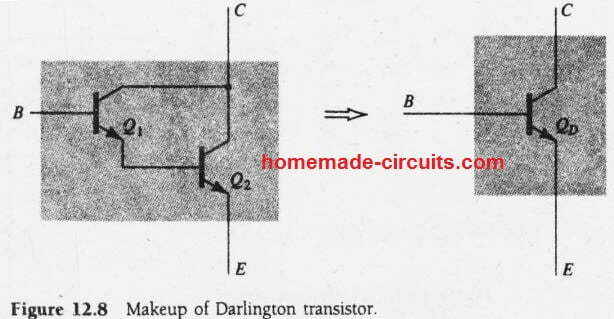

达林顿晶体管是一对双极晶体管,连接在一起,从低基极电流提供非常高的电流增益。输入晶体管的发射极始终连接到输出晶体管的基极;他们的收藏家被绑在一起。结果,输入晶体管放大的电流被输出晶体管进一步放大

2023-02-16 18:19:11

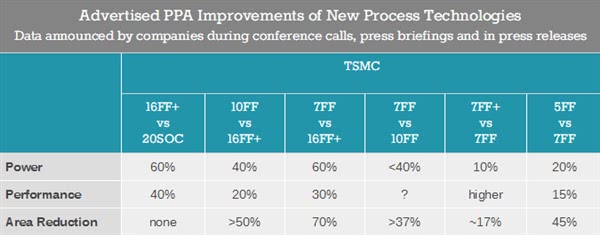

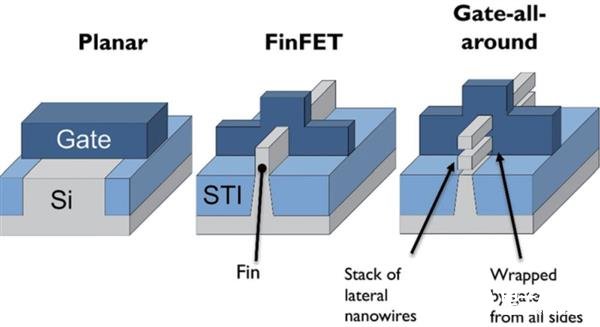

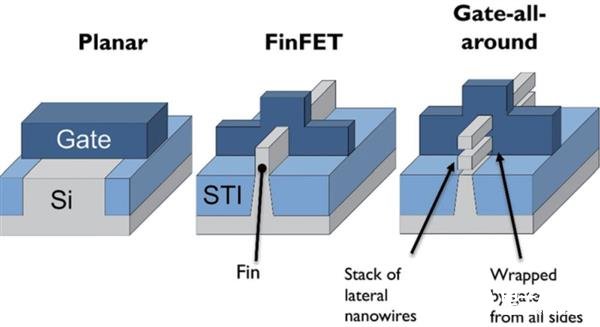

场效应管的演变 鳍式场效应晶体管的未来发展前景 FinFET在5nm之后将不再有用,因为它没有足够的静电控制,需要晶体管的新架构。然而,随着技术节点的进步,一些公司可能会出于经济原因决定在同一节点上

2023-02-24 15:25:29

从7nm到5nm,半导体制程芯片的制造工艺常常用XXnm来表示,比如Intel最新的六代酷睿系列CPU就采用Intel自家的14nm++制造工艺。所谓的XXnm指的是集成电路的MOSFET晶体管栅极

2021-07-29 07:19:33

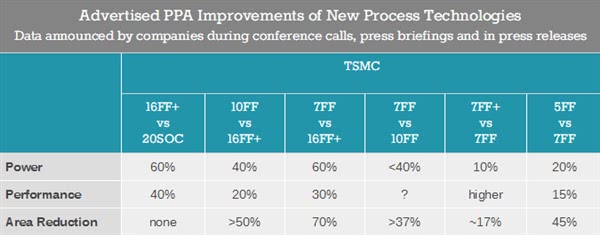

nm晶圆厂进入生产状态。台积电的5nm制程分为N5及N5P两个版本。N5相较于当前的7nm制程N7版本在性能方面提升了15%、功耗降低了30%,晶体管密度提升了80%。N5P版本性能较N5提升7

2020-03-09 10:13:54

请教:单结晶体管在什么位置,有人说是UJT,但好象用不了呀?

2013-09-26 16:55:49

各位高手,小弟正在学习单结晶体管,按照网上的电路图做的关于单结晶体管的仿真,大多数都不成功,请问谁有成功的单结晶体管的仿真仿真啊,可以分享下吗。

2016-03-04 09:15:06

台积电宣布5nm基本完工开始试产:面积缩小45%、性能提升15%.pdf(105.52 KB)

2019-04-24 06:00:42

电流,进而改变流过给定晶体管的集电极电流。 如果我们达到集电极电流的最大流量,则晶体管已饱和。将晶体管导通所需的输入电压和电流量由基极电阻决定 图5. 数字逻辑晶体管开关 在R上方的电路

2023-02-20 16:35:09

什么是微波功率晶体管?如何提高微波功率晶体管可靠性?

2021-04-06 09:46:57

来至网友的提问:如何选择分立晶体管?

2023-11-24 08:16:54

晶体管依照用途大致分为高频与低频,它们在型号上的大致区别是什么?例如《晶体管电路设计》中列举的:高频(2SA****,2SC*****)、低频(2SB****,2SD****)。现在产品设计中最常用的型号是哪些?

2017-10-11 23:53:40

bandgap中晶体管的热噪声比较大,通过什么手段能解决?

2021-06-24 07:29:25

选定方法①使TR达到饱和的IC/IB的比率是IC/IB=20/1②输入电阻:R1是±30% E-B间的电阻:R2/R1=±20%③VBE是0.55~0.75V数字晶体管具有下面的关系式。■数字晶体管

2019-04-22 05:39:52

选定方法数字晶体管的型号说明IO和IC的区别GI和hFE的区别VI(on)和VI(off)的区别关于数字晶体管的温度特性关于输出电压 - 输出电流特性的低电流领域(数字晶体管的情况)关于数字晶体管

2019-04-09 21:49:36

10月7日,沉寂已久的计算技术界迎来了一个大新闻。劳伦斯伯克利国家实验室的一个团队打破了物理极限,将现有最精尖的晶体管制程从14nm缩减到了1nm。晶体管的制程大小一直是计算技术进步的硬指标。晶体管

2016-10-08 09:25:15

晶体管的代表形状晶体管分类图:按照该分类,掌握其种类1. 按结构分类根据工作原理不同分类,分为双极晶体管和单极晶体管。双极晶体管双是指Bi(2个)、极是指Polar(极性)。双极晶体管,即流经构成

2019-05-05 01:31:57

没事看看了电力电子,看到这个原理图,有点迷糊了,按图所示,如果集电极C处为N型半导体,按照图中来C极应该接负极才对呀?为什么还接正极?这样如何导通?有没有大神指导下GTR的双晶体管模型是什么样的?

2020-06-11 09:03:42

来至网友的提问:如何选择分立晶体管?

2018-12-12 09:07:55

这个达林顿晶体管厂家是哪家

2022-05-30 16:36:56

本帖最后由 eehome 于 2013-1-5 10:10 编辑

高清图详解英特尔最新22nm 3D晶体管

2012-08-05 21:48:28

高清图详解英特尔最新22nm_3D晶体管

2012-08-02 23:58:43

晶体管分类

按半导体材料和极性分类 按晶体管使用的半导体材料可分为硅材料晶体管和锗材料晶体管。按晶体

2009-11-05 10:48:53 4989

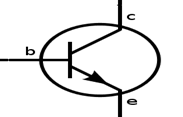

4989 PNP晶体管,PNP晶体管是什么意思

PNP晶体管是另一种类型晶体管.它的结构如图1所示。

2010-03-05 11:18:05 6814

6814 双极晶体管,双极晶体管是什么意思

双极晶体管

双极型晶体管内部电流由两种载流子形成,它是利用电流来控制。场效应管是电压控制器

2010-03-05 11:48:46 6586

6586 电力晶体管(GTR),电力晶体管(GTR)是什么意思

电力晶体

电力晶体管管按英文GiantTransistor直译为巨型晶体

2010-03-05 13:32:30 14825

14825 CMOS晶体管,CMOS晶体管是什么意思

金属-氧化物-半导体(Metal-Oxide-Semiconductor)结构的晶体管简称MOS晶体管,有P型MOS管和N型MOS管之分

2010-03-05 15:22:51 4129

4129 晶体管耗散功率,晶体管耗散功率是什么意思

晶体管耗散功率也称集电极最大允许耗散功率PCM,是指晶体管参数变化不超过规定允许值时的最大

2010-03-05 17:34:10 8979

8979 未来环保汽车会是什么样?

一汽-大众

2010-04-07 09:08:53 1996

1996

晶体管种类很多,检测方法也不一样,这里详细介绍了各种晶体管的检测方法

2016-02-23 17:43:00 0

0 为什么说7nm是物理极限?缩短晶体管栅极的长度可以使CPU集成更多的晶体管或者有效减少晶体管的面积和功耗,并削减CPU的硅片成本。不过这种做法也会使电子移动的距离缩短,容易导致晶体管内部电子自发通过

2016-10-10 16:49:39 6418

6418 摩尔定律是指IC上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。然而事情的发展总归会有一个权限,5nm则是硅芯片工艺的极限所在,事实上,随着10nm、7nm芯片研发消息不断报出

2016-12-22 10:23:11 43944

43944 作为台积电最有竞争力的竞争对手,三星联手IBM打造5nm新工艺叫板台积电。

为了实现这个壮举,就必须在现有的芯片内部构架上进行改变。研究团队将硅纳米层进行水平堆叠,而非传统的硅半导体行业的垂直堆叠构架,这使得5nm晶体管的工艺有了实现可能,而这一工艺将有可能引爆未来芯片性能的进一步高速发展。

2018-01-20 19:56:27 7498

7498

关键层面上首次尝试使用EVU极紫外光刻系统,工艺节点从CLN7FF升级为CLN7FF+,号称晶体管密度可因此增加20%,而在同样密度和频率下功耗可降低10%。 台积电5nm(CLN5)将继续使用荷兰

2018-05-15 14:35:13 4690

4690

化合物半导体的主要问题是硅和III-V半导体之间的大的晶格(lattice)失配,导致晶体管沟道的缺陷。有一家公司开发了一种含有V形沟槽的FinFET进入硅衬底。这些沟槽充满铟镓砷并形成晶体管的鳍片。沟槽底部填充磷化铟以减少漏电流。

2019-08-29 15:58:09 4056

4056

CPU使用数十亿个微型晶体管,电子门打开和关闭以执行计算。晶体管越小,所需的功率就会越小。7nm和10nm是这些晶体管尺寸的测量尺寸。nm是纳米和微小长度的缩写,以此来判断特定CPU有多强大的有用指标。

2019-08-18 10:02:17 7884

7884 7nm+ EUV节点之后,台积电5nm工艺将更深入地应用EUV极紫外光刻技术,综合表现全面提升,官方宣称相比第一代7nm EDV工艺可以带来最多80%的晶体管密度提升,15%左右的性能提升或者30%左右的功耗降低。

2019-09-26 14:49:11 5945

5945 CPU里的晶体管都是集成的超微晶体管,一个22纳米工艺的i5可能集成上十亿的晶体管。

2020-01-31 16:10:00 15286

15286 目前全球最先进的半导体工艺已经进入 7nm,下一步还要进入 5nm、3nm 节点,制造难度越来越大,其中晶体管结构的限制至关重要,未来的工艺需要新型晶体管。

2019-12-10 15:40:49 7723

7723 5nm工艺问世,CPU工艺与性能是一种什么样的关系

2020-01-09 14:03:04 5428

5428 Intel之前已经宣布在2021年推出7nm工艺,首发产品是数据中心使用的Ponte Vecchio加速卡。7nm之后的5nm工艺更加重要了,因为Intel在这个节点会放弃FinFET晶体管转向GAA晶体管。

2020-03-11 09:51:09 6774

6774

FinFET晶体管随后也成为全球主要晶圆厂的选择,一直用到现在的7nm及5nm工艺。

2020-03-12 07:48:00 2686

2686 台积电5nm制造工艺基于ULV,也就是紫外线光刻技术实现,之前的7nm EUV工艺同样也是基于这项技术。那么制程的缩小又意味着什么?相比于7nm工艺,5nm工艺可以进一步提升芯片的晶体管密度,提升性能并降低功耗,可广泛用于PC、智能手机等设备的元器件中。

2020-03-12 14:10:44 3184

3184 本文首先阐述了晶体管的概念,其次介绍了晶体管的优越性,最后阐述了晶体管的控制方式。

2020-03-14 09:47:12 13941

13941 。 摩尔定律认为,集成电路上可容纳的晶体管数量,每隔18至24个月就会增加一倍,性能也将提升一倍。当芯片制程演进到5nm,它晶体管的集成度和精细化程度都要比以往更高,可容纳更复杂的电路设计,并将更丰富的功能融入其中。 但从目前行业

2020-07-10 17:53:37 1201

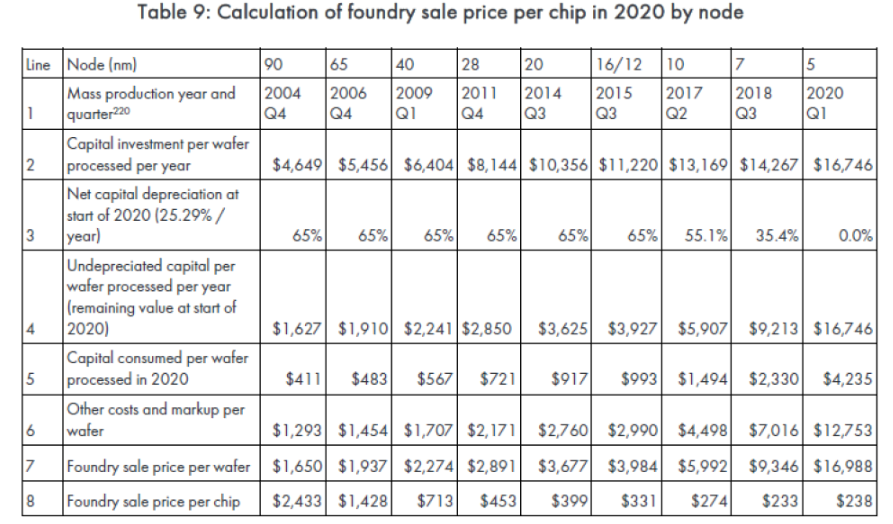

1201 此前苹果已经发布了A14芯片,作为全球首颗采用台积电5nm工艺的芯片,其集成118亿个晶体管,在性能和能效上相比A13都有一定提升。但A14芯片采用台积电5nm工艺,所付出的代价也是相当高的! 最近

2020-09-28 16:26:28 5832

5832

的通道更容易控制。但是,随着3nm和5nm技术节点面临的难题不断累积,FinFET的效用已经趋于极限。 晶体管缩放的难题 在每个技术节点,设备制造商可以通过缩小晶体管的方法来降低器件面积、成本和功耗并实现性能提升,这种方式也称为PPAC(功率、性能、面积、成本)

2021-01-25 15:25:40 3874

3874

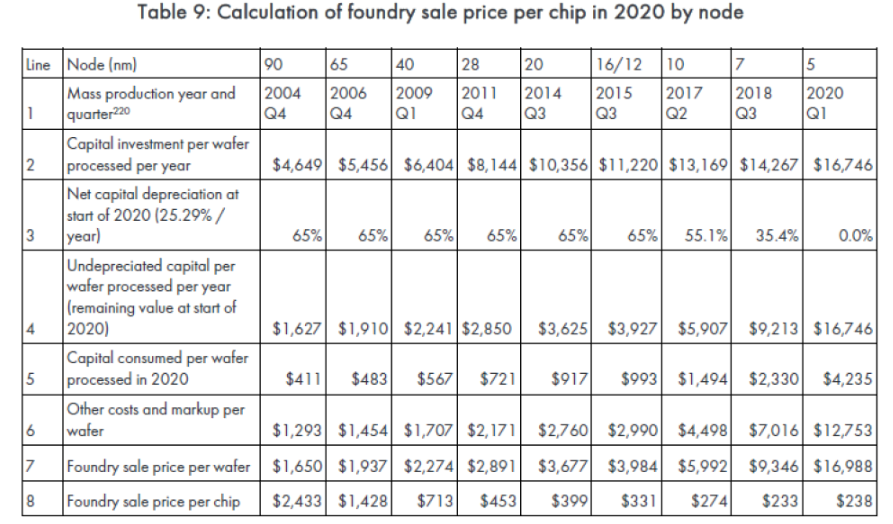

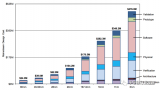

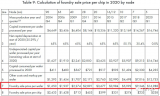

与Nvidia P100 GPU(610m㎡,907亿个晶体管,强度为148.2 MTr/m㎡)相当。 从上表可以看到,5nm晶圆单片的代工销售价约是16988美元,对比7nm,涨幅超80%。而对于使用16nm或

2020-10-10 17:57:07 4645

4645

Mate 40系列来了,麒麟9000也终于来了! 这是全球第一颗、也是唯一一颗5nm工艺制造的5G SoC,集成多达153亿个晶体管,首次突破150亿大关,是目前晶体管最多、功能最完整的5G SoC

2020-10-23 09:11:10 5006

5006 Mate 40系列来了,麒麟9000也终于来了!这是全球第一颗、也是唯一一颗5nm工艺制造的5G SoC,集成多达153亿个晶体管,首次突破150亿大关,是目前晶体管最多、功能最完整的5G SoC。

2020-10-23 10:37:18 5336

5336 使用5nm制程技术,CPU,GPU和NPU的性能遥遥领先。该芯片还集成了华为最强大的通信芯片以及最先进的ISP。由于采用了5nm工艺,麒麟9000集成了153亿个晶体管,比A14仿生晶体管多30%。麒麟9000是业界功能最强大的芯片。

2020-10-28 16:27:02 5165

5165 昨天,半导体逆向工程与IP服务机构ICmasters近日将一颗苹果A14放在了显微镜下,仔细观察了一番这个怪物。 苹果A14采用台积电5nm工艺制造,集成多达118亿个晶体管,内核面积仅为88

2020-11-06 09:58:11 2359

2359 首先苹果带来了其自研Mac芯片—M1。据苹果介绍,M1芯片将CPU、GPU、内存等整合在一起。采用5nm技术,拥有160亿个晶体管,主打低功耗、小体积等特点。

2020-11-11 10:04:42 3085

3085 从 2020 年下半年开始,各家手机芯片厂商就开始了激烈的 5nm 芯片角逐,苹果、华为、高通、三星相继推出旗舰级 5nm 移动处理器,并宣称无论是在性能上还是在功耗上都有着优秀的表现。 不过

2021-01-20 14:57:54 42510

42510

功耗是芯片制造工艺演进时备受关注的指标之一。比起7nm工艺节点,5nm工艺可以使产品性能提高15%,晶体管密度最多提高1.8倍。三星猎户座1080、华为麒麟9000、骁龙888和苹果的A14芯片都

2021-02-04 08:40:57 5208

5208 功耗是芯片制造工艺演进时备受关注的指标之一。比起7nm工艺节点,5nm工艺可以使产品性能提高15%,晶体管密度最多提高1.8倍。三星猎户座1080、华为麒麟9000、骁龙888和苹果的A14芯片都

2021-02-04 14:33:10 8218

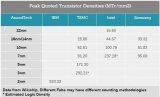

8218 台积电的5nm芯片每平方毫米约有1.73亿个晶体管,三星的5nm芯片每平方毫米约有1.27亿个晶体管。这样对比来看,IBM 2nm晶体管密度达到了台积电5nm的2倍。

2021-05-10 14:22:34 3501

3501

虽然栅极间距(GP)和鳍片间距(FP)的微缩持续为FinFET平台带来更高的性能和更低的功耗,但在5nm及更先进节点上,兼顾寄生电容电阻的控制和实现更高的晶体管性能变得更具挑战。

2022-05-05 16:00:29 2446

2446

现在的芯片技术越来越先进,人们常常能够听到某某公司又研发出5nm、4nm芯片的消息,而目前全球所研发出的最先进的芯片是IBM公司的2nm芯片,我们都知道芯片内部有很多晶体管,那么2nm芯片的晶体管

2022-07-04 09:15:36 5743

5743 7nm芯片和5nm芯片的区别在哪?7nm芯片和5nm芯片哪个好?在其他变量恒定的情况下,5nm芯片肯定要强于7nm芯片,5纳米芯片意味着更小的芯片,5纳米芯片要优于7纳米芯片,但是最终还是要看机器是否能够发挥芯片的最大功效。

2022-07-05 09:26:18 25002

25002 ,即“芯片上的晶体管数量大约每两年翻一番”。为了获得缩小晶体管的好处,VLSI 行业正在不断改进晶体管结构和材料、制造技术以及设计 IC 的工具。迄今为止,晶体管已采用各种技术,包括高 K 电介质、金属

2022-07-28 16:18:55 1347

1347

不过电子设备专家表示,到2047年,量子计算的发展速度还不足以挑战晶体管的地位。“晶体管仍将是最重要的计算元件。”IEEE会士、加州大学伯克利分校电气工程和计算机科学教授萨耶夫•萨拉赫丁

2023-03-21 10:59:55 1333

1333 在比利时安特卫普举行的ITF World 2023上,英特尔技术开发总经理Ann Kelleher概述了英特尔在几个关键领域的最新进展,最有趣的是英特尔将在未来采用堆叠CFET晶体管。

2023-05-20 10:01:14 910

910

达林顿晶体管是一种众所周知且流行的连接,使用一对双极晶体管结型晶体管(BJT),设计用于像统一的“超β”晶体管一样工作。下图显示了连接的详细信息。

2023-06-29 10:06:49 2671

2671

华为发布首款5nm 5G SoC,集成153亿晶体管 在当今的数字时代,5G成为了一种越来越重要的通信技术,它能够大幅提升传输速度和低延时,以实现更高的数据传输质量。而华为公司最近发布了自家

2023-09-01 16:47:35 9729

9729 晶体管就像电子开关一样工作。它可以打开和关闭电流。一种简单的思考方法是将晶体管视为没有任何活动部件的继电器。晶体管在某种意义上类似于继电器,您可以使用它来打开和关闭某物。

2023-10-15 16:30:00 6365

6365

上次我的文章解释了所谓的7nm不是真的7nm,是在实际线宽无法大幅缩小的前提下,通过改变晶体管结构的方式缩小晶体管实际尺寸来达到等效线宽的效果那么新的问题来了:从平面晶体管结构(Planar)到立体

2023-12-19 16:29:01 1396

1396

NMOS晶体管和PMOS晶体管是两种常见的金属氧化物半导体场效应晶体管(MOSFET)类型,它们在多个方面存在显著的差异。以下将从结构、工作原理、性能特点、应用场景等方面详细阐述NMOS晶体管和PMOS晶体管的区别。

2024-09-13 14:10:00 9544

9544

电子发烧友App

电子发烧友App

评论