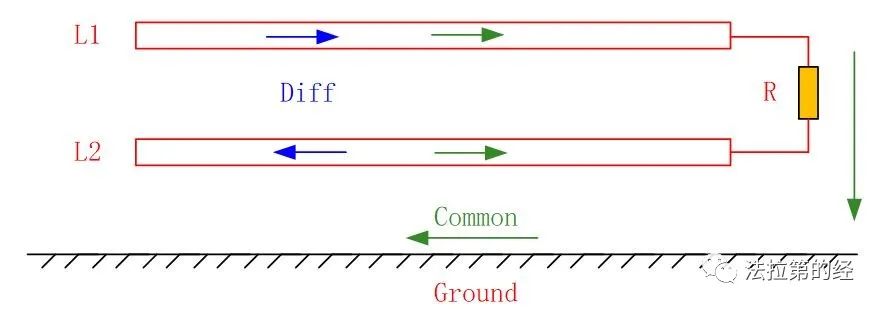

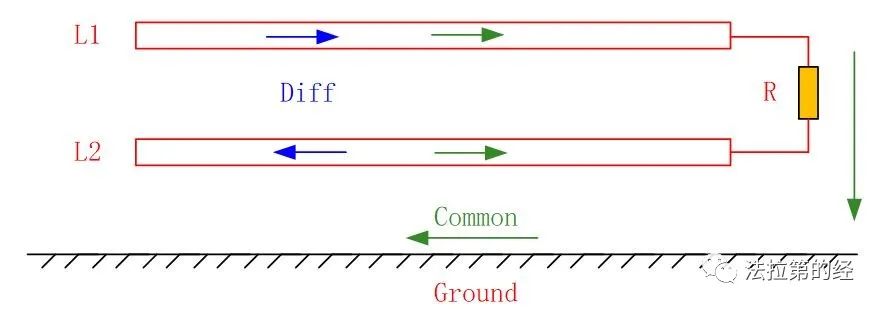

为了提高电路的共模抑制比,常采用对消驱动电路(右腿驱动)来提高共模抑制比,本文分析了对消驱动电路的原理,结合实际电路实际验证了电路的效果。

2012-02-02 11:20:15 3869

3869

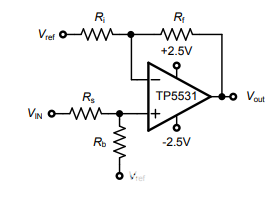

许多硬件工程师会将放大器的共模抑制比视为最难掌握的直流参数,首先因为定义所涉及的因子容易产生混淆;其次,掌握了共模抑制比的定义,按其字面理解难以在设计中直接使用;最后,掌握了放大器的共模抑制比参数

2020-10-14 16:41:45 13606

13606

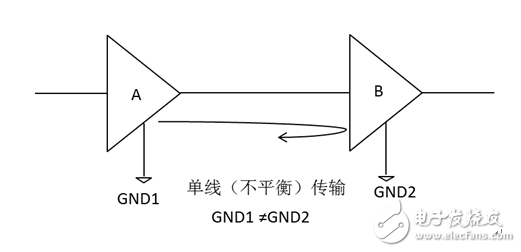

共模抑制比(CMRR)是最重要的规格参数,它表示将要测量的共模信号量。CMMR的值经常取决于信号频率和指定的功能。CMMR功能专门用于降低传输线上的噪声。例如,当在嘈杂的环境中测量热电偶的电阻时,来自环境的噪声表现为两条输入引线上的偏移,并使其成为共模电压信号,CMRR仪器测量应用于噪声的衰减。

2022-08-30 17:21:05 15546

15546

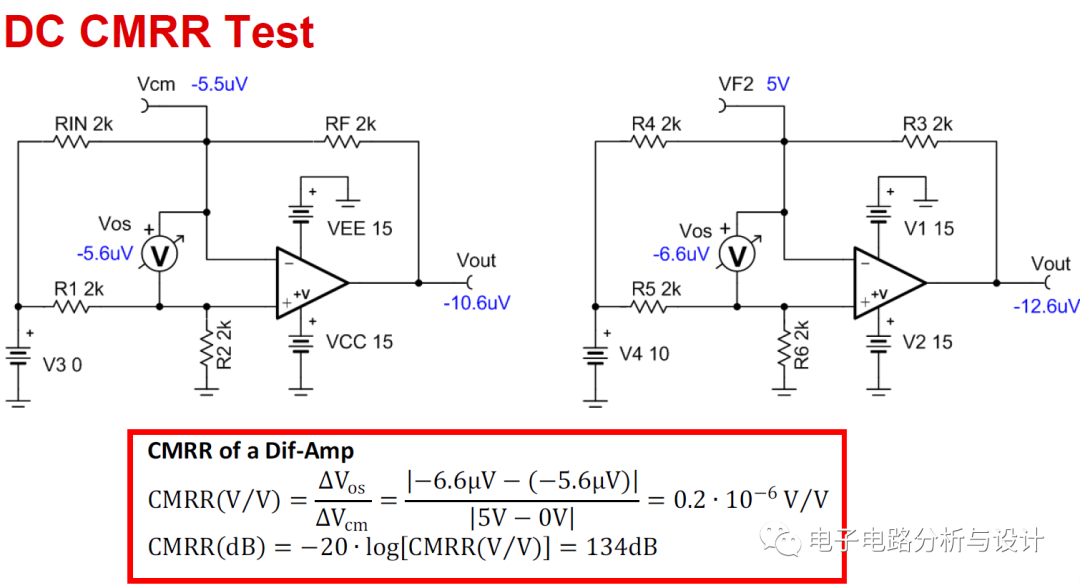

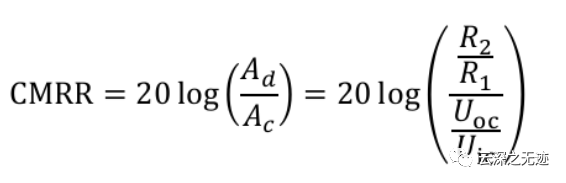

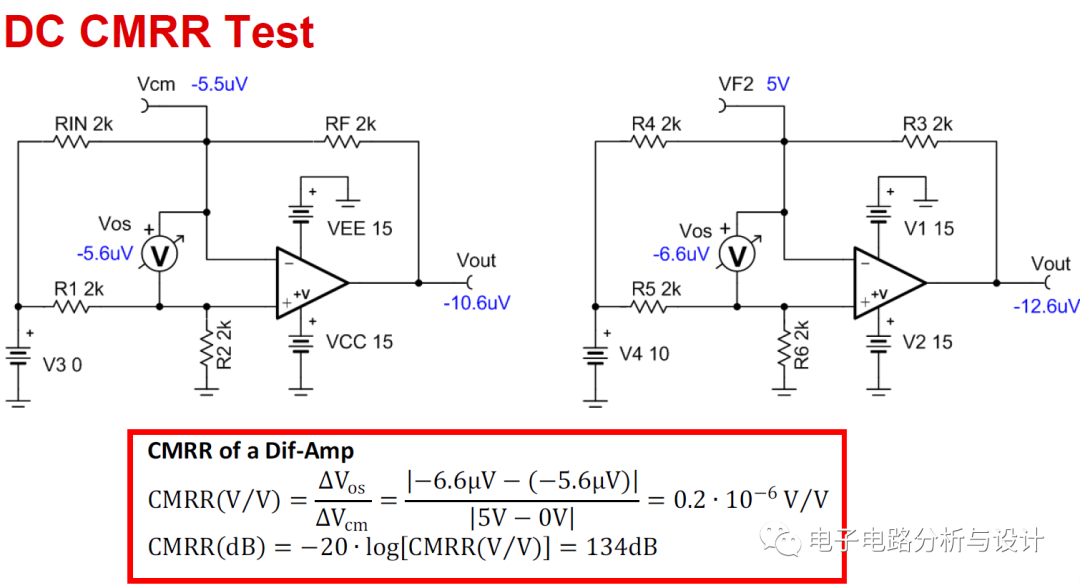

实际上,共模电压的变化会引起输出变化。 运算放大器共模抑制比(CMRR)是 指共模增益与差模增益的比值。

2023-02-12 17:08:42 7038

7038

在高压差分探头的设计和应用中共模抑制比(Common Mode Rejection Ratio,简称CMRR)是一个重要的性能指标。CMRR代表了差分信号和共模信号之间的差异,量化了探头能够抵抗共模

2023-08-09 09:41:30 1504

1504

今天继续给大家分享运放另一项指标——共模抑制比(CMRR)。

2023-10-01 13:10:00 13734

13734

在开始讨论运放的共模抑制比CMRR之前,我们先了解一下运放的共模输入电压和轨对轨运放。

2023-11-02 10:20:11 9676

9676

一、什么是共模抑制比?共模抑制比(CMRR)是衡量放大器对共模信号抑制能力的一个关键指标,是用来描述设备抵御共模信号影响的能力。共模信号是指同时存在于两个输入端并具有相同大小和相位的信号,例如电源

2024-06-04 08:10:46 6434

6434

共模抑制比(CMRR:comon-mode-rejection-ratio)和电源抑制比(PSRR:power-supply-rejection-ratio)是运放性能的重要指标,关于他们的具体仿真

2021-12-27 07:24:51

我在找信号放大器的时候,有的给出了增益,类似于功率可以增加多少倍,有的给出了共模抑制比,这两个我怎么分别?我最后的结果是看我的信号功率能否从-15dBm增加到10dBm,共模抑制比我怎么换算?

2018-08-09 09:48:40

读论文analysis of switched-capacitor commom-mode feedback circuit1.与单端输出相比,全差分电路有更好的共模抑制比和电源抑制比。2.共模环路

2021-10-29 07:10:25

AD-运算放大器共模抑制比CMRR

2012-04-01 10:47:33

按照图接法,后面跟0.5~100Hz的贝塞尔带通滤波器,测INA128共模抑制比波形失真,在输入频率很低时,几十Hz时波形会上面一部分被截平,频率变高到100Hz以后波形变得正常。这是为什么?

2024-09-20 07:35:42

按照图接法,后面跟0.5~100Hz的贝塞尔带通滤波器,加入15V的共模信号,测INA128共模抑制比波形失真,上部分波形被截去一部分,这是为什么?

2024-09-20 07:36:50

,10V共模电压也就产生0.1mV的电压误差而已。

为了排除单板的问题,换了一片其它厂商的P2P兼容芯片,0V共模输出电压为0,10V时输出电压大约0.5mV,去掉分压电阻贡献的0.5mV,共模抑制比

2024-08-13 07:29:17

请问在仪表放大器正极、负极同时增加相同规格的电压跟随器,为什么会导致共模抑制比的大幅度下降呢?

如果仅使用仪表放大器INA317,实测共模抑制比能达到110dB。而为了增加高输入阻抗和驱动能力,前

2024-08-01 06:49:48

Java语言学习六大关键

2021-01-01 07:59:00

ads1291共模抑制比与频率曲线中,为什么CMRR是负数,我们的理解CMRR应该是正数。

谢谢

2024-11-25 08:16:54

仪表放大器AD620的共模输入范围超过电源电压,会影响共模抑制比吗?比如AD620采用正负5V电源供电,放大倍数为10倍,测试时共模输入范围为7.07V / 100Hz,会影响共模抑制比吗?

2023-11-15 06:49:17

使用AD8422BRZ放大差分信号时,共模抑制比最大只能做到90dB,有什么方法可以改善共模抑制比大于100dB呢

2024-05-31 07:35:34

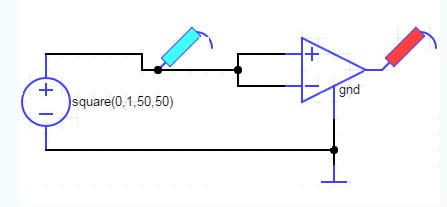

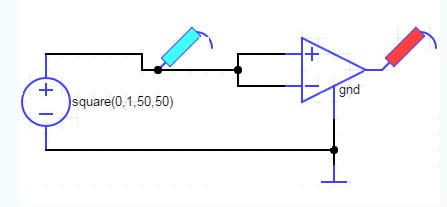

如图所示,下面是一个交流耦合放大电路,在电路的差分输入端输入差模(100uV,10Hz)和共模信号(10V,10Hz),进行电路的共模抑制比(CMRR)测试,测试发现:

1、差分信号从INS+

2018-08-03 06:26:16

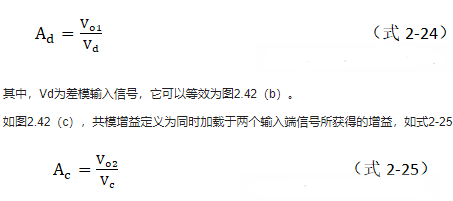

共模抑制比(CMRR) 是指差分放大器对同时加到两个输入端上的共模信号的抑制能力。更确切地说,CMRR是产生特定输出所需输入的共模电压与产生同样输出所需输入的差分电压的比值。差分放大器共模响应,是指

2016-09-23 15:34:29

[td][/td] 如图所示,如何设计AD8221交流耦合电路能:

1、降低噪声,提高信噪比(SNR);

2、提高仪表运放输入阻抗;

3、提高共模抑制比(CMRR)。

2023-11-17 09:47:43

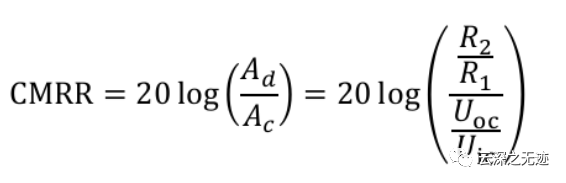

通过精确匹配的电阻网络提高差分放大器的共模抑制比

2021-01-28 06:19:27

提高差分放大器的共模抑制比,电阻的选择很关键

2021-03-11 07:17:03

最近需要测定仪表放大器的共模抑制比, 按照:将所有电极连在一起,相对于大地驱动这些电极。同样,共模抑制的定义是20×log(VOUT/VIN),其中,VIN为共模驱动信号,VOUT为特定目标导联

2024-09-03 08:28:22

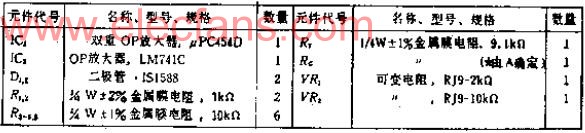

如何利用高增益运放,设计了一种具有高共模抑制比,高增益数控可显的测量放大器。提高了测量放大器的性能指标,并实现放大器增益较大范围的步进调节。

2021-04-22 06:59:18

下图是电子学第二版的一个差分放大电路,书中说这电路共模抑制比是10万,这能从图中算出来吗?

2020-04-08 23:09:06

影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

2024-09-09 07:32:22

此电路用来检测脑电波的信号,性能要求此电路的共模抑制比要达到不低于80dB,而现在实测只能达到67dB,想知道,影响电路共模抑制比的因素有哪些?如何去提高电路的共模抑制比?

2024-08-20 07:21:02

怎么根据共模抑制比Kcmr、最大共模输入电压Vic挑选运放

常见的集成运放推荐?

2024-08-19 06:22:13

怎么测ADS1299芯片的共模抑制比?将通道1的正负极输入短接,接入一个0.5VP,共模电压2.5V,F=50Hz,FFT图像显示输出在50Hz时,为80dB。然而手册是-110dB,应该怎么测出-110dB的共模抑制比呢?

2024-11-15 06:26:03

用到AD8227这款芯片,感觉共模抑制比有点低,请问怎么测定这个参数,我试过:将所有电极连在一起,相对于大地驱动这些电极。同样,共模抑制的定义是20×log(VOUT/VIN),其中,VIN为共模

2023-11-21 06:24:20

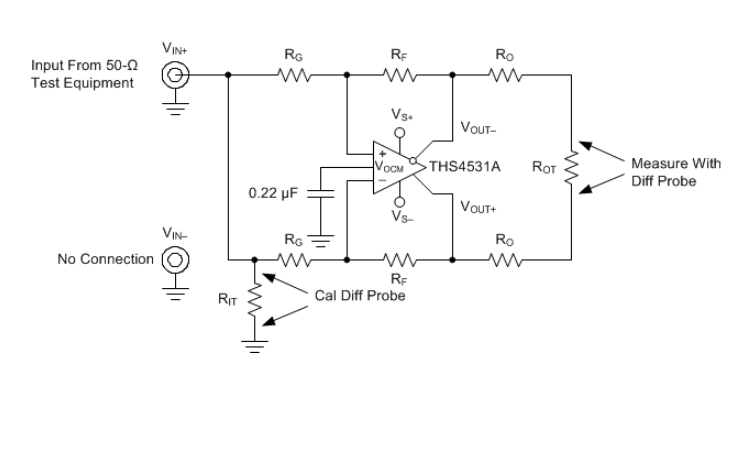

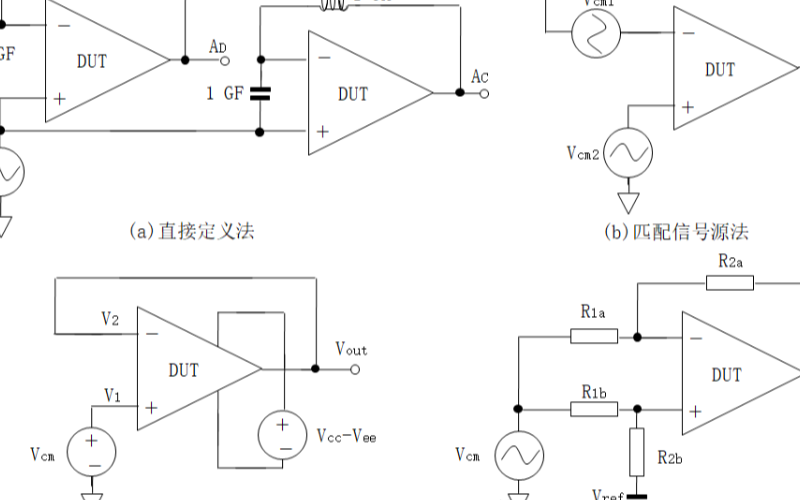

常被误用的放大器共模抑制比测量方法会存在哪些不足?有没有一种有效测量共模抑制比电路方案介绍?

2021-03-11 06:00:18

容易让人想到,在高增益下产生任何输出偏移,都需要电源的明显变化!但一定要记住:共模抑制比 (CMRR) 和 PSRR 都是输入参考参数:(1) PSRR 和 CMRR 定义为输入失调电压变化 ΔVOS

2018-09-19 11:00:26

有没有测电路中INA818共模抑制比的测试方法

2024-08-02 10:23:18

可以给我一些关于仪表放大器共模抑制比的测量方法吗?最好详细一点

2024-08-01 07:16:28

50Hz的共模信号(相对REF),我该怎么判断共模抑制比的大小才合理?

问题三:如果我对1.65V产生的共模信号进行软件校准清零,再叠加1V 50Hz的共模信号(相对REF)上去,测得的值是否为真实的1V 50Hz 下的共模抑制比?

如果不正确,那怎样才能测到正确的值?

2024-08-05 06:27:21

如图所示,下面是一个交流耦合放大电路,在电路的差分输入端输入差模(100uV,10Hz)和共模信号(10V,10Hz),进行电路的共模抑制比(CMRR)测试,测试发现:

1、差分信号从INS+

2023-11-17 09:09:39

寻找一款超高共模抑制比的仪表运放,起码高于120dB,越高越好

2018-08-03 07:12:09

ADC的Ref±输入端 也有共模抑制比对吧

2025-01-13 07:20:02

请问下有没有共模抑制比测量的芯片,我只百度到了下面的测量电路。

2021-12-29 11:39:15

如图所示,如何设计AD8221交流耦合电路能:1、降低噪声,提高信噪比(SNR);2、提高仪表运放输入阻抗;3、提高共模抑制比(CMRR)。

2018-08-06 06:55:10

用到AD8227这款芯片,感觉共模抑制比有点低,请问怎么测定这个参数,我试过:将所有电极连在一起,相对于大地驱动这些电极。同样,共模抑制的定义是20×log(VOUT/VIN),其中,VIN为共模

2018-09-13 11:52:30

1、很多人用运放选共模抑制比越大越好,考虑到成本,我想计算一下理论值到底符不符合,比如我采分流器上的电流±74A,Gain=0.0335,共模输入电压有5V,电流精度要满足0.05%,假如运放

2024-08-15 07:43:04

高共模抑制比仪用放大电路方案

2012-10-29 06:44:52

通过硬件和软件的仿真实验,总结出差分放大电路共模抑制比测定的正确方法关键词:差分放大电路;共模抑制比;差模电压放大倍数;共模电压放大倍数;仿真

2010-04-13 11:07:33 91

91 什么是共模抑制比

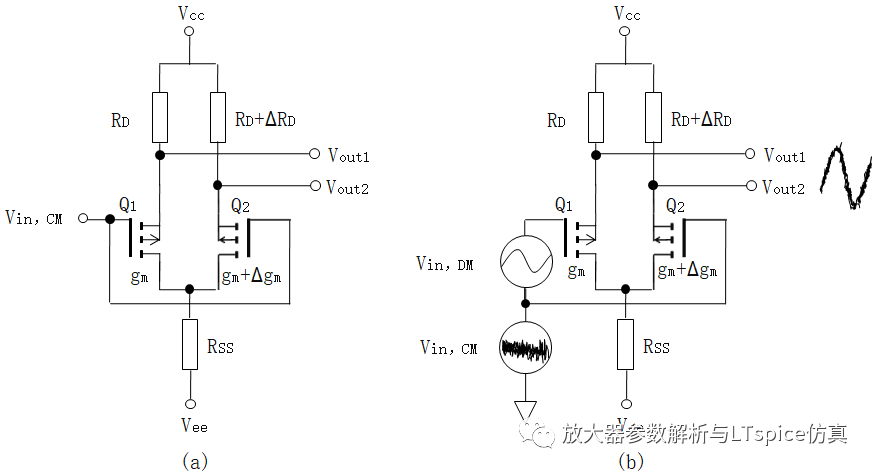

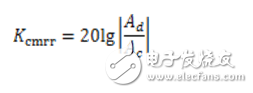

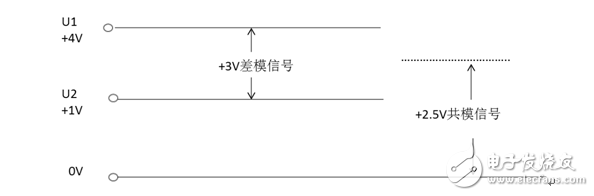

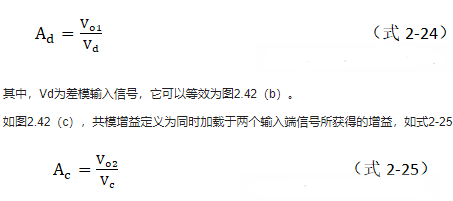

为了说明差动放大电路抑制共模信号的能力,常用共模抑制比作为一项技术指标来衡量,其定义为放大器对差模信号的电压放大倍数Aud 与对共模信号的电

2007-10-15 17:37:51 9087

9087

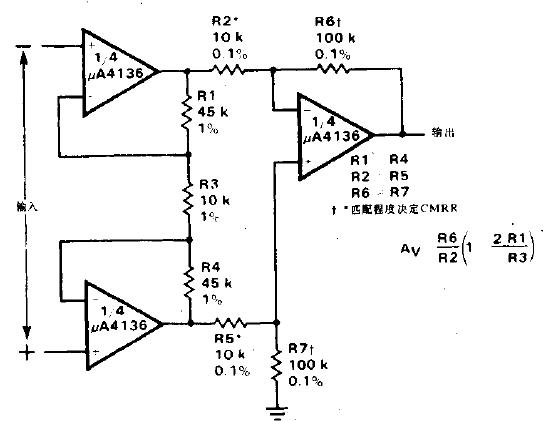

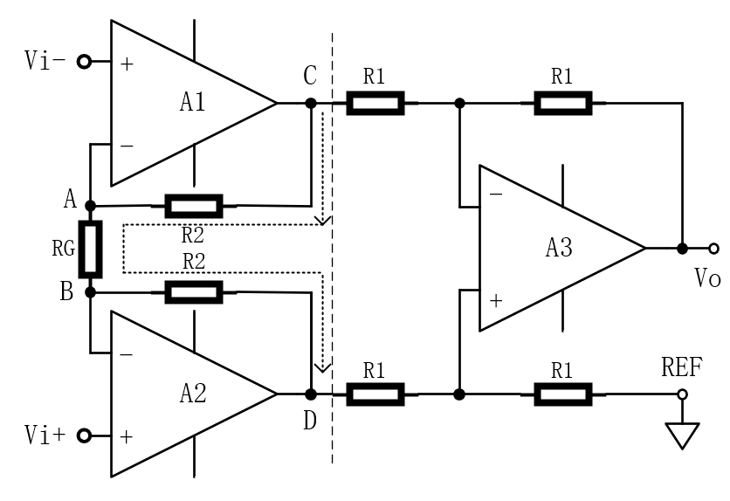

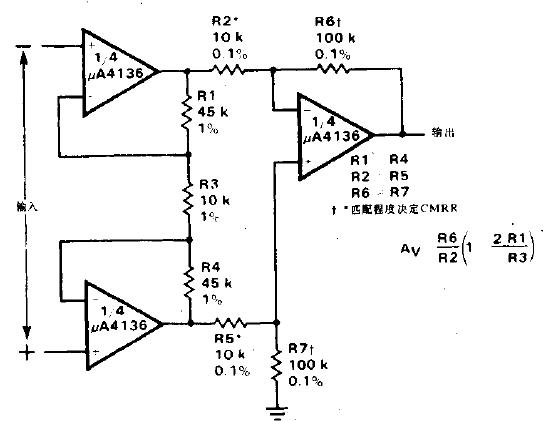

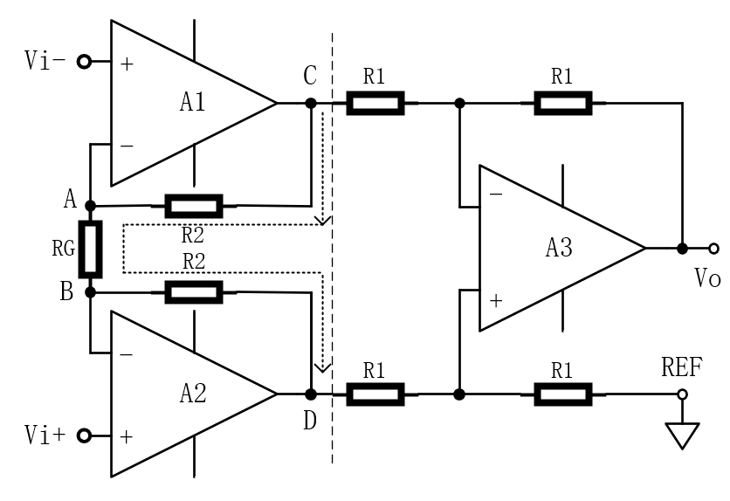

具有高共模抑制比的差分输入仪器用放大器电路图

2009-04-01 09:14:11 1310

1310

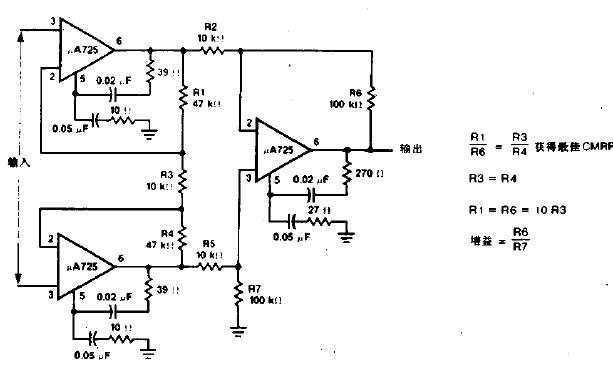

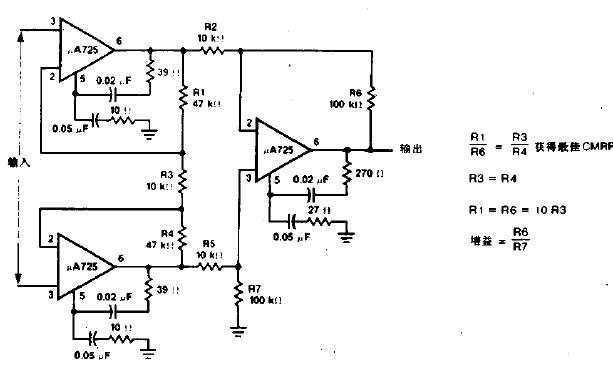

具有高共模抑制比的仪器用放大器电路图

2009-04-01 09:14:35 1196

1196

放大器的共模抑制比的定义

共模抑制比(CMRR)是指差分放大器对同时加到两个输入端上的共模信号的抑制能力。更确切地说,CMRR是产生特

2009-04-22 20:40:37 2542

2542 苹果上网本所面对的六大问题

乔布斯是个幸福的人,有时他的一场病都能引起不小的关注。苹果的粉丝们

2010-02-03 11:06:33 409

409 共模抑制比,共模抑制比是什么意思

共模抑制比的定义

为了综合评价差动放大电路对共模信号的抑制能力和对差模信号的放大能力,特

2010-03-09 16:36:11 14810

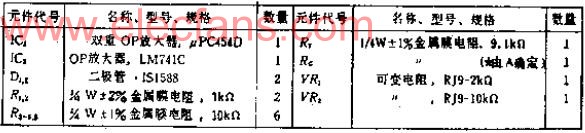

14810 共模抑制比和输入阻抗高的仪表用差动放大电路

电路的功能

一个OP放大器构成的高增益差

2010-04-27 16:16:13 3717

3717

本文针对传统仪用放大电路的特点,介绍了一种高共模抑制比仪用放大电路,引入共模负反馈,大大提高了通用仪表放大器的共模抑制能力。

2012-02-02 14:32:34 118

118 华强盛电子导读:网络变压器共模抑制比CMRR概念及原理 网络变压器共模抑制比CMRR 在网络变压器工程图纸中我们会看到一个参数 CMRR,它中文翻译为共模抑制比,那么它是个什么概念呢

2019-02-25 17:55:54 2464

2464 在电子学中,差分放大器(或其他装置)的共模抑制比(CMRR)是一个度量,用于量化装置抑制共模信号的能力,即那些同时出现在两个输入端且同相出现的信号。一个理想的差分放大器将有无限的共模抑制比,但这在

2019-09-14 10:57:00 65839

65839

来源:罗姆半导体社区 共模抑制比(CMRR) 是指差分放大器对同时加到两个输入端上的共模信号的抑制能力。更确切地说,CMRR是产生特定输出所需输入的共模电压与产生同样输出所需输入的差分电压的比值

2023-02-01 13:42:32 5689

5689 如《放大器共模抑制比(CMRR)参数评估与电路共模抑制能力实例分析》中案例,由于电阻误差导致电路共模抑制能力下降,是使用通用放大器组建差动放大电路的常见问题之一。工程师常常疑惑1%误差的电阻

2020-10-31 09:42:35 4820

4820

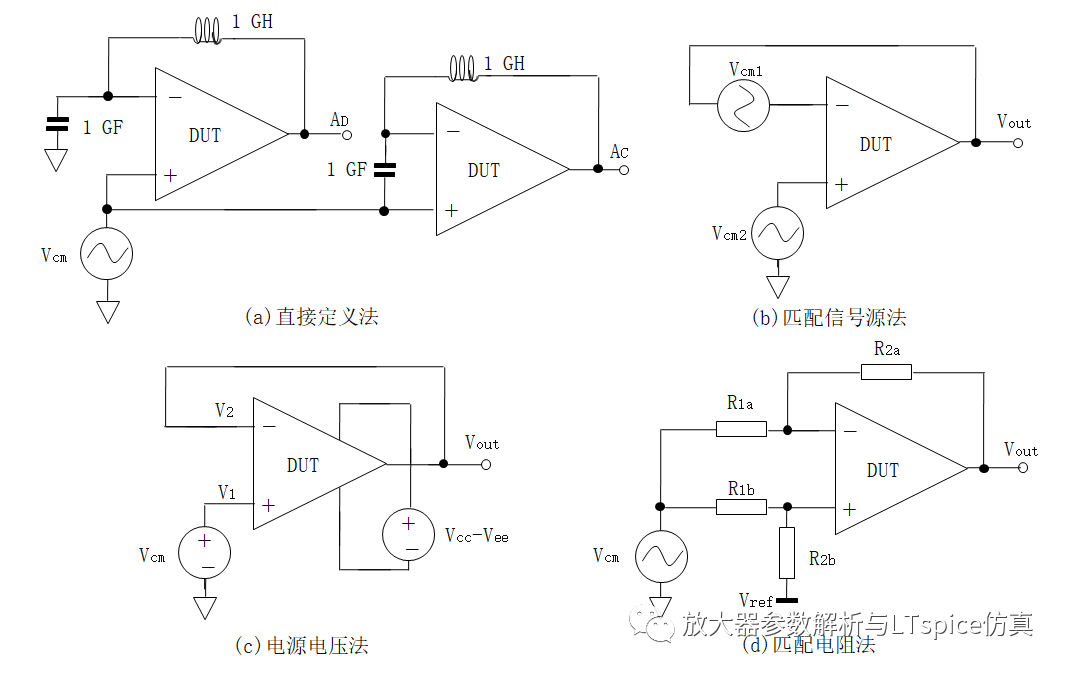

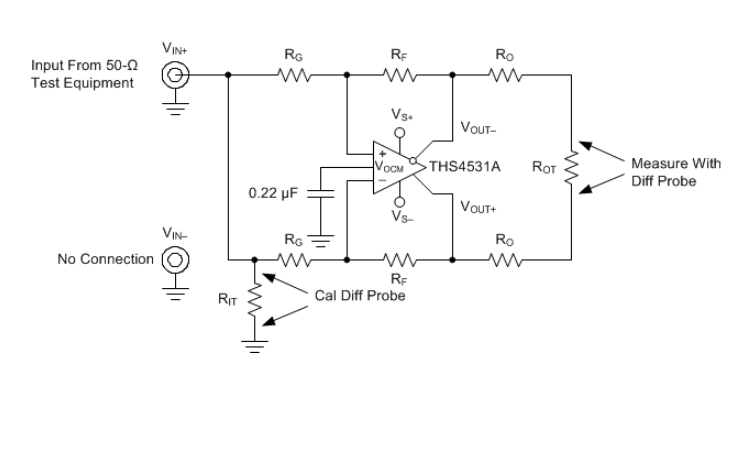

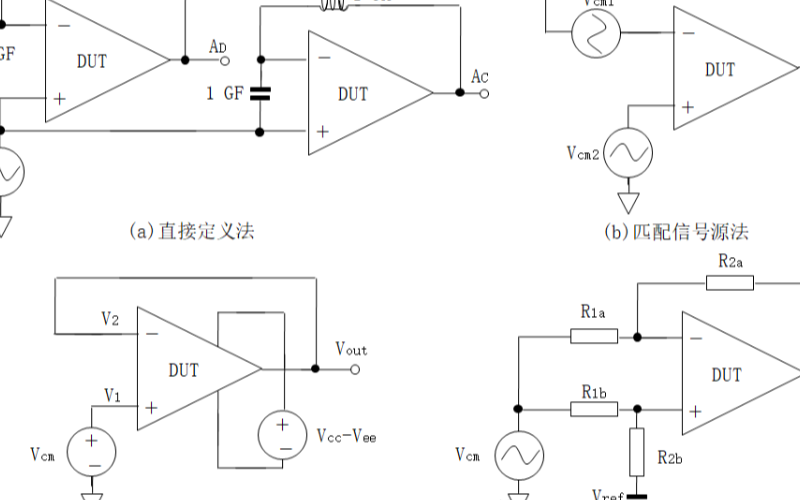

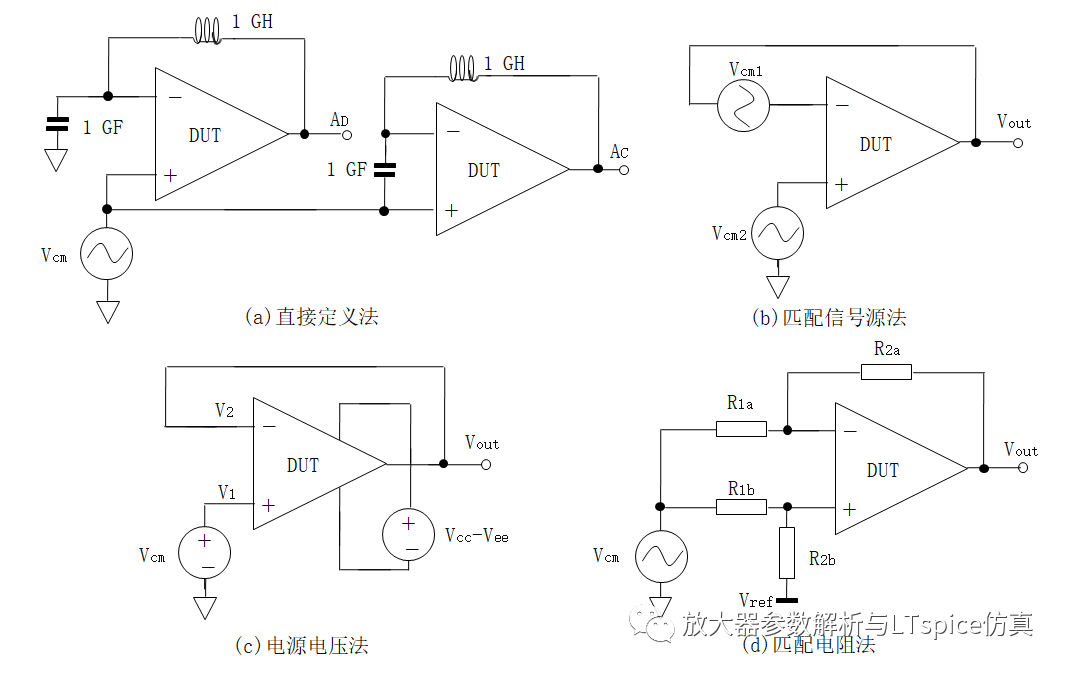

测量放大器的失调电压、偏置电流参数,可根据所设计的电路简易调整就能完成测试。而共模抑制比参数的测试方法却相对复杂,本篇分析几种常被误用的放大器共模抑制比测量方法的不足之处,以及提供一种有效测量

2020-11-04 18:00:47 5693

5693

在《放大器共模抑制比(CMRR)参数评估与电路共模抑制能力实例分析》文中,介绍使用共模抑制比的倒数,将共模信号折算到输入端评估所引起的误差,有工程师认为这种方式在输入共模信号为交流信号时的结果不准

2020-11-14 11:09:05 5371

5371

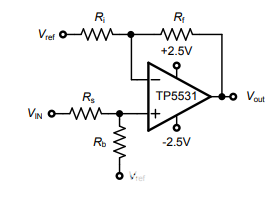

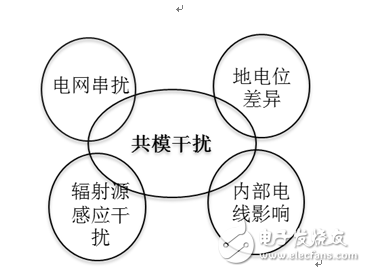

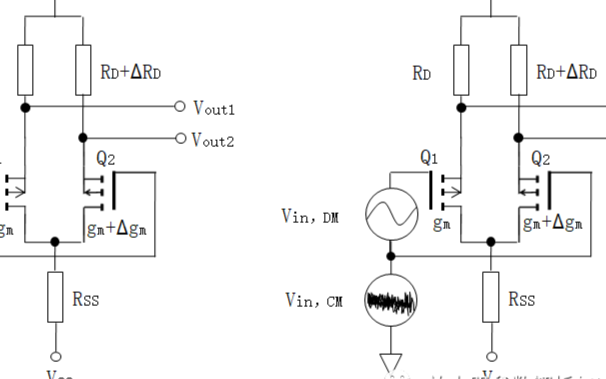

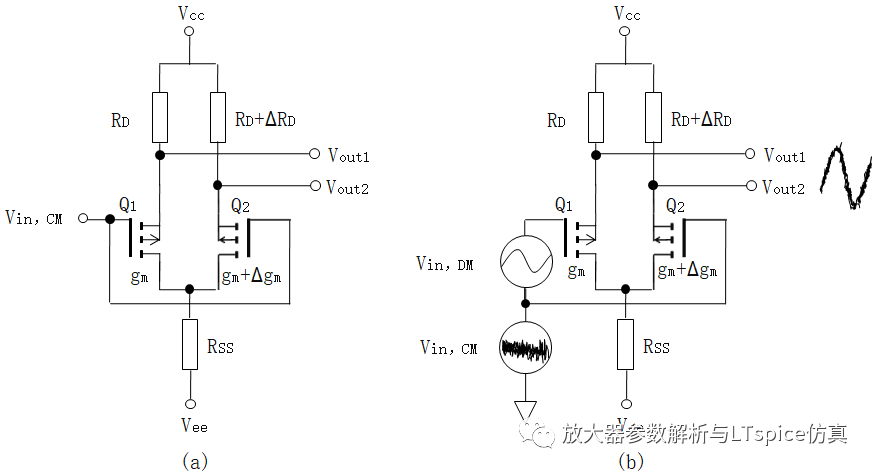

共模抑制比的提高方法和模拟噪声分析的注意事项 一、共模抑制比的提高方法 我们重点介绍通过精确匹配的电阻网络提高差分放大器的共模抑制比。在各种应用领域,采用模拟技术时都需要使用差分放大器电路

2021-05-04 10:15:00 11080

11080

MT-042:运算放大器共模抑制比(CMRR)

2021-03-21 08:57:14 13

13 共模抑制比(CMRR:comon-mode-rejection-ratio)和电源抑制比(PSRR:power-supply-rejection-ratio)是运放性能的重要指标,关于他们的具体仿真

2022-01-05 14:22:58 6

6 理想情况下,差分放大器电路中的电阻应仔细选择,其比值应相同 (R2/R1 = R4/R3)。这些比值有任何偏差都将导致不良的共模误差。差分放大器抑制这种共模误差的能力以共模抑制比(CMRR) 来表示。

2022-06-01 09:41:09 4460

4460 其实在共模信号为交流信号时,这种评估方法仍然实用,问题在于放大器的共模抑制比参数并非恒定不变,它随共模信号频率变化变化。本篇介绍共模抑制比随共模交流信号变化的原因,评估示例,并通过仿真增强理解。

2023-02-22 14:30:55 2374

2374

测量放大器的失调电压、偏置电流参数,可根据所设计的电路简易调整就能完成测试。而共模抑制比参数的测试方法却相对复杂,本篇分析几种常被误用的放大器共模抑制比测量方法的不足之处,以及提供一种有效测量共模抑制比电路以及提供仿真。

2023-02-22 14:33:45 4622

4622

仪表放大器共模抑制比怎么计算? 仪表放大器是一种性能较高的放大器,其主要功能是对信号进行高精度的放大和测量,具有通用性,不仅可用于电子器件中,还可用于传感器和仪表等领域。仪表放大器的共模抑制比是衡量

2023-09-05 17:39:18 4532

4532 失调电压和共模抑制比的区别和联系 失调电压和共模抑制比是两个重要的电路参数,它们的测量和分析对于电路的设计和稳定性评估非常重要。本文将详细介绍失调电压和共模抑制比的定义、测量方法以及它们之间的区别

2023-09-21 17:40:32 1979

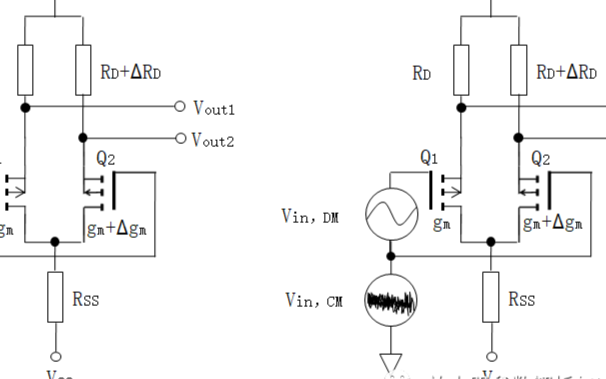

1979 带恒流源的差分放大器如何提高共模抑制比的? 差分放大器是常见的电路设计,它可以提供高增益和高共模抑制比。但是,由于器件的不匹配和温度变化等因素,共模电压可能会出现偏移,使得差分电路的性能受到影响

2023-10-23 10:29:16 2984

2984 什么是共模抑制比CMRR?什么是电源抑制比PSRR? 共模抑制比(common mode rejection ratio,CMRR)和电源抑制比(power supply rejection

2023-10-29 11:45:48 10804

10804 影响共模抑制比的主要因素 如何提高共模抑制比? 共模抑制比是一种衡量信号处理系统抑制共模干扰的能力的指标。它表示当输入信号被共模干扰所扰动时,系统输出信号中共模干扰的减弱程度。共模抑制比较大的系统

2023-11-08 17:46:26 3551

3551 运放的共模抑制比高有什么作用?共模抑制比比较高的运放有哪些啊? 共模抑制比(Common Mode Rejection Ratio,CMRR)是一个衡量运放的性能的重要指标,表示运放在输入信号的共模

2023-11-20 16:35:53 3089

3089 电子发烧友网站提供《适合过程控制应用的完整高速、高共模抑制比(CMRR)精密模拟前端.pdf》资料免费下载

2023-11-24 15:33:30 0

0 同相比例放大器为什么对共模抑制比要求高?运放的共模抑制比如何仿真? 同相比例放大器是一种常见的放大电路,用于放大微弱信号。在应用中,通常需要对放大的信号进行差分测量,即对信号的差值进行放大,而抑制

2024-01-26 14:42:55 3544

3544 共模抑制比和边模抑制比分别是什么意思?有什么区别? 共模抑制比和边模抑制比是电子电路设计中两个重要的性能指标。它们描述了一个电路在输入信号中存在的共模干扰和边模干扰下能够提供的抑制程度。共模抑制比

2024-02-05 14:55:20 3211

3211 共模抑制比详解在探头的数据手册上,共模抑制比性能参数是核心指标之一。共模抑制比又名CMRR,通常用分贝(dB)来表示,其计算公式为:其中其中本司光隔离产品CMRR在直流或低频下能达到120dB以上

2025-06-23 09:45:17 1138

1138

仪表放大器最显著的优势之一在于其极高的共模抑制比(Common-Mode Rejection Ratio,CMRR),这一指标直接决定了系统在强共模干扰环境下对微弱差模信号的提取能力。因此,在仪表

2025-12-25 07:41:04 121

121

电子发烧友App

电子发烧友App

评论