作者:John Johnson,德州仪器

本文介绍时钟抖动对高速链路性能的影响。我们将重点介绍抖动预算基础。

用于在更远距离对日益增长的海量数据进行传输的一些标准不断出现。来自各行业的工程师们组成了各种委员会和标准机构,根据其开发标准的目标(数据吞吐量和通信距离)确定抖动预算;同时还要考虑到组成通信链路的模块的局限性。

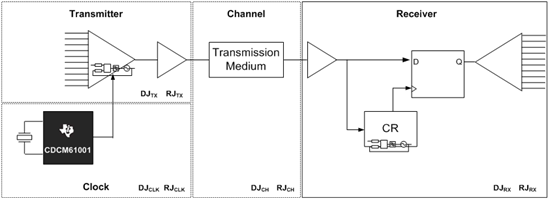

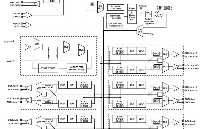

图 1 通信链路—抖动组件

图 1 显示了集成有一个嵌入式时钟的典型高速通信链路。每个子系统(时钟、发送器、通道和接收机)都会对整体抖动预算的增加产生影响。子系统抖动包括一个决定性 (DJ) 组件和一个随机组件 (RJ),如图 1 所示。为了实现可接受的通信效果,必须满足下列条件:

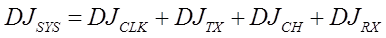

方程式 1

方程式 1

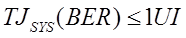

其中:TJSYS 是总抖动,而 1UI 为1个单位时间间隔(1 比特时间)

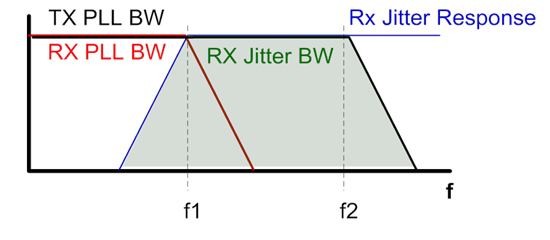

总抖动 (TJ) 包括每个子系统决定性抖动和随机抖动的和。由于随机抖动自身的属性,进行这种求和时需要特别注意。随机抖动呈现高斯(随机)分布,并且无边界。因此,随机抖动可表示为一个 RMS 值,并且在规定测量/整合带宽范围内对其进行估算。例如,图 1 所示接收机的抖动测量带宽便为 f2 - f1(参见图 2)。这是因为接收机锁相环路 (PLL) 追踪 f1 以下的抖动(从而排斥它),而发射 PLL 的频率上限为 f2。从接收机的角度来看,使链路性能降低的随机抖动降至这些限制之间。

图 2 高速通信链路—随机抖动测量带宽

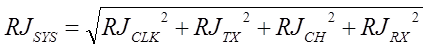

由于随机抖动是随机过程产生的结果,系统总随机抖动的计算需要进行方和根 (RSS) 计算,如方程式2所示:

方程式 2

决定性抖动源和的计算很简单:

方程式 3

方程式 3

最后,可对系统总抖动进行估算,由此可以实现链路预算;但是,还需要做更多的工作。这种计算涉及统计数学。需要用到一种被称之为 Q 因数的参数(参见表 1)。Q 因数的大小具体取决于误码率 (BER),同时还要根据链路性能/可靠性目标来选择。由于随机抖动的无边界属性,(最终)会出现误码。例如,10-8 的 BER 意味着,每发送 100,000,000 比特便会有一个比特被错误解释。现代的通信系统通常会要求一个达到或者超过 10-12 以上的 BER。

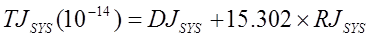

系统总抖动(以及链路预算)可使用方程式 4 计算得到:

方程式 4

方程式 4

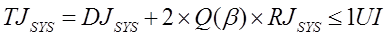

例如,10-14 的 BER 时,总抖动为:

方程式 5

方程式 5

本文讨论了构成总抖动预算的一些参数。下一次,我们将探讨时钟,并研究随机抖动和相位噪声之间的关系。

编辑:jq

-

嵌入式

+关注

关注

5186文章

20151浏览量

328905 -

模拟

+关注

关注

7文章

1445浏览量

85125 -

时钟

+关注

关注

11文章

1953浏览量

134548

发布评论请先 登录

高速光模块时钟解决方案:YSO233UJ通过高基频光刻工艺实现超低抖动与高频率稳定性

时钟振荡器选型与排障:从抖动预算到PCB电源的工程实操(含延伸阅读)

LMK03318 具有单 PLL 的超低抖动时钟发生器系列技术手册

LMK05028 低抖动双通道网络同步器时钟芯片总结

LMK05318 带BAW的超低抖动单通道网络同步器时钟技术手册

差分输出 × 超低抖动:打造高速稳定的大型数据同步时脉

差分输出VCXO:低抖动时钟源助力光通信系统精密同步

AD9547双路/四路输入网络时钟发生器/同步器技术手册

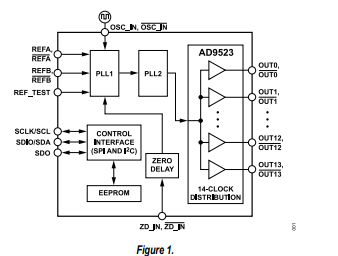

AD9523 14路输出、低抖动时钟发生器技术手册

高速链路时钟抖动规范基础知识

高速链路时钟抖动规范基础知识

评论