关于 MC1496 模拟乘法器芯片的 PCB 设计要点,以下是一些关键建议和注意事项,适用于设计承载该芯片的电路板:

核心设计原则

-

电源去耦(关键!)

- 每个电源引脚(V+、V-)附近放置 0.1μF陶瓷电容(如NPO/X7R),尽量贴近引脚。

- 增加 1μF~10μF 的钽电容或电解电容作为低频去耦,靠近芯片电源入口。

- 使用 星型拓扑或单独走线为模拟部分供电,避免数字噪声串扰。

-

接地设计

- 采用 单点接地或 分区接地(模拟地AGND),避免地回路干扰。

- 为芯片设置 独立接地铜箔区域,减小地线阻抗。

- 去耦电容接地端直接连接到地平面(过孔短而粗)。

-

信号布线

- 输入/输出信号线尽量短,减少寄生电容和辐射干扰。

- 高频应用时采用 50Ω阻抗匹配(尤其驱动射频负载)。

- 敏感信号(如输入引脚1、4、8、10)远离电源/时钟线,必要时用地线隔离。

-

热管理

- MC1496功耗较低(约300mW),但双电源供电时需确保散热:

- 芯片下方铺设接地铜箔辅助散热。

- 避免密闭空间,必要时添加散热孔。

- MC1496功耗较低(约300mW),但双电源供电时需确保散热:

关键外围电路与PCB对应

-

偏置电路

- 电流设定电阻(如引脚2-3间的Rext)选用 低温漂精密电阻(如金属膜电阻)。

- 电位器(如调平衡)建议使用 多圈精密电位器,布局时便于调试。

-

输入/输出耦合

- 若需隔直,耦合电容(Cin/Cout)选择 低ESR的陶瓷电容或薄膜电容(如C0G/NP0)。

- 高频应用时注意电容自谐振频率(SRF)。

高频应用特别注意事项

-

缩短高频路径

- 乘法器输出(引脚6、12)至负载的走线最短化。

- 避免直角走线,使用45°或圆弧拐角。

-

屏蔽与隔离

- 关键高频区域可用 接地屏蔽罩 或 接地过孔包围(Guard Ring)。

- 敏感走线避免平行长距离布线,采用垂直交叉。

调试与测试建议

- 预留测试点

- 关键节点(输入/输出、电源、偏置电压)添加测试焊盘。

- 平衡调节

- 调零电位器布局靠近芯片,减少引线干扰。

- Prototype验证

- 首次设计建议用 洞洞板或开发板测试电路,再制作PCB。

推荐PCB层叠结构

| 层序 | 用途 | 说明 |

|---|---|---|

| Top | 信号线 + 元件 | 布置芯片、关键信号线 |

| Mid1 | 接地层(AGND) | 完整地平面,低阻抗回流 |

| Mid2 | 电源层(可选) | 分割为V+/V-区域 |

| Bottom | 信号线 + 接地覆铜 | 次要走线,强化接地 |

示例布局示意图

[V+] ---[0.1μF]--- MC1496 (Pin 8)

│(贴片电容紧贴引脚)

[AGND]─┘

│

[V-] ---[0.1μF]--- MC1496 (Pin 5)

│

[信号输入]───短走线─── Pin 1/10

│

[输出]───50Ω走线─── Pin 6/12 → 负载总结 Checklist

- ✅ 电源去耦:0.1μF陶瓷电容 紧贴 V+/V-引脚

- ✅ 低噪声接地:单点/分区接地 + 完整地平面

- ✅ 信号隔离:敏感走线远离干扰源

- ✅ 高频优化:短直走线 + 阻抗匹配

- ✅ 可调试性:测试点 + 电位器易操作位置

遵循上述原则可显著提升电路稳定性,尤其在调制、混频等应用中降低失真和噪声。若需具体电路参考,建议查阅厂商资料(如ON Semi原厂设计指南)或开源射频项目案例。

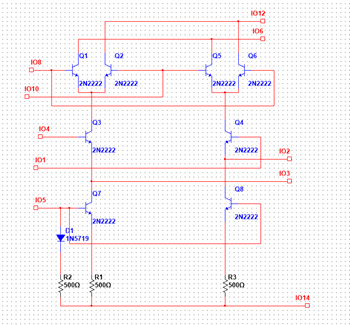

基于Multisim的MC1496调幅电路的仿真

包含MC1496调幅电路的设计分析以及仿真结果本文大部分内容都属于原创,如需转载,请附上本文网站,另外,如果需要相关的仿真图、程序代码等资料可以直接私信我。attach://1046610.docx

![]() NFDKAGON

2021-06-28 16:32:59

NFDKAGON

2021-06-28 16:32:59

乘法器原理_乘法器的作用

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为

2021-02-18 15:08:01

MC1496 平衡调制器和解调器

电子发烧友网为你提供()MC1496相关产品参数、数据手册,更有MC1496的引脚图、接线图、封装手册、中文资料、英文资料,MC1496真值表,MC1496管脚等资料,希望可以帮助到广大的电子工程师们。

2019-04-18 21:57:09

怎么设计基于FPGA的WALLACETREE乘法器?

在数字信号处理中,乘法器是整个硬件电路时序的关键路径。速度和面积的优化是乘法器设计过程的两个主要考虑因素。由于现代可编程逻辑芯片FPGA的集成度越来越高,及其相对于ASIC设计难度较低和产品设计

![]() mikee

2019-09-03 07:16:34

mikee

2019-09-03 07:16:34

Multisim调制解调电路仿真

求助,小弟做了AM基于乘法器MC1496的调幅电路和二极管包络检波电路;还有FM的变容二极管调频电路和相位鉴频器鉴频电路,现在需求将解调的信号为之前调制出的信号,也就是调制解调电路整合成一个电路,但是调制和解调电路所用的信号频率不相同,加上对原理不够了解,现在不知道如何修改,请各位大神指教,谢谢。

![]() ZzzzzzzSH

2020-04-14 23:37:40

ZzzzzzzSH

2020-04-14 23:37:40

采用Gillbert单元如何实现CMOS模拟乘法器的应用设计

在集成电路系统中,模拟乘法器在信号调制解调、鉴相、频率转换、自动增益控制和功率因数校正控制等许多方面有着非常广泛的应用。实现模拟乘法器的方法有很多,按采用的工艺不同,可以分为三极管乘法器和CMOS乘法器。

2021-03-23 09:40:19

基于CMOS工艺下的Gillbert单元乘法器的研究

在集成电路系统中,模拟乘法器在信号调制解调、鉴相、频率转换、自动增益控制和功率因数校正控制等许多方面有着非常广泛的应用。实现模拟乘法器的方法有很多,按采用的工艺不同,可以分为三极管乘法器和CMOS乘法器。

2019-05-31 08:20:00

BJ-EPM240学习板:乘法器设计实验

乘法器是模拟式电子式电能表的重要组成部分,也是电能表计量误差的最主要来源。对时分割乘法器在谐波条件下的计量误差进行了定量的研究与分析,根据时分割乘法器的工作原理,推导其在谐波条件下计量误差的理论表达式,并通过仿真计算验证计量误差量化表达式的准确性。

2019-12-24 07:05:00

硬件乘法器的相关资料分享

一,乘法器硬件乘法器是一个通过内部总线与 CPU 相连的 16 位外围模块。MSP430 单片机可以在部改变 CPU 结构和指令的情况下增加功能,这种结构特别适用于对运算速度要求很严格的情况。硬件

![]() 山川1998

2021-12-09 07:05:15

山川1998

2021-12-09 07:05:15

采用CSA与4-2压缩器改进Wallace树型乘法器的设计

在微处理器芯片中,乘法器是进行数字信号处理的核心,同时也是微处理器中进行数据处理的关键部件。乘法器完成一次操作的周期基本上决定了微处理器的主频。乘法器的速度和面积优化对于整个CPU的性能来说是非常重要的。为了加快乘法器的执行速度,减少乘法器的面积,有必要对乘法器的算法、结构及电路的具体实现做深入的研究。

2019-05-15 08:27:00

如何分析传统乘法器和vedic乘法器的时序延迟?

我正在研究一种适用于Vedic Maths算法的乘法器。我想对传统乘法器和vedic乘法器的时序延迟进行比较分析。我有spartan 3e和Xilinx 12.1时序分析器。请任何人都可以指导我

![]() Jade799153347

2019-07-04 06:36:45

Jade799153347

2019-07-04 06:36:45

模拟乘法器输出与输入的关系式

模拟乘法器是输出电压与两路输入电压之积成正比的有源网络。理想的乘法器具有无限大的输入阻抗及零输出阻抗,其标尺因子不随频率变化并且与电压的大小无关。如果理想的乘法器的任意一路输入电压为零时,则输出电压就为零。换句话说,它的失调、漂移和噪声电压均为零。

2021-02-18 17:21:19

如何实现一个四输入乘法器的设计

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

2019-11-28 07:06:00

模拟乘法器为何没输出信号

模拟乘法器为何没输出信号我在仿真analog 的乘法器。我使用的是 Multisim 自带的库文件。器件用的 AD834。我画好设计图后,接上虚拟示波器。可是,信号发生器里有信号,乘法器后没有。请问各位高人,我哪里画错了。还是,multisim自带的库文件就不行

![]() crazylogic2022

2022-04-01 16:48:04

crazylogic2022

2022-04-01 16:48:04

乘法器与调制器

我们使用调制器而不是乘法器有几个原因。乘法器的两个端口都是线性的,因此载波输入上的任何噪声或调制都会使信号输入成倍并降低输出,而调制器载波输入的幅度变化大多可以忽略不计。二阶机制会导致载波输入端的幅度噪声影响输出,但在最好的调制器中,这些噪声被最小化,这里不讨论。

2023-01-30 14:26:35

FPGA视频教程:BJ-EPM240学习板-乘法器设计实验

乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为乘法、除法、乘方和开方等模拟运算的主要基本单元,而且还广泛用于电子通信系统作为调制、解调、混频、鉴相和自动增益控制;另外还可用于滤波、波形形成和频率控制等场合,因此是一种用途广泛的功能电路。

2019-12-11 07:04:00

三种高速乘法器实现原理

随着3G技术的发展,关于图像、语音、加密等数字信号处理技术随处可见,而且信号处理的实时性也要求越高。实时性即是要求对信号处理的速度要快,而乘法器是数字信号处理中重要的基本运算,在很大程度上影响着系统的性能。人们开始开发高速的乘法器。

2022-07-03 11:14:20

模拟乘法器电路图

精密模拟乘法嚣电路由精密电容器开关LTC1043及运算放大器LT1056等可组成精密模拟乘法器。精度可达0.01%。电阻选用金属膜电阻,与LIC1043相连的电容器选用聚苯乙烯的,并尽量靠近器件的管脚安装。

2021-02-18 15:46:41

AVR的硬件乘法器8X8的吗?

AVR的硬件乘法器8X8的吗,数据手册上是这么写的。结果是16位的他这个乘法器应该是内核自带的吧,还是外设呢如果用CV编译,如何调用乘法器呢数据手册上只给出了汇编代码,如果是用c语言如何调用呢,还是不用调用直接写式子就可以了呢?

![]() lmxh123

2020-07-22 08:00:51

lmxh123

2020-07-22 08:00:51

哪里有包含ADC的FPGA板和包含FPGA的足够的乘法器模块?

/devkits/HW-SPAR3A-SK-UNI-G.htm它有两个模拟输入和fpga,有20个乘法器但是我想要更多的输入和更多的乘法器块,是否能够满足这些功能的任何板?

![]() 武汉核电曹志泉

2019-08-23 07:03:09

武汉核电曹志泉

2019-08-23 07:03:09

基于Multisim的MC1496调幅电路的仿真

及集电极调幅电路等。通常,多采用三极管调幅电路,被调放大器如果使用小功率小信号调谐放大器,称为低电平调幅;反之,如果使用大功率大信号调谐放大器,称为高电平调幅。这里的MC1496调幅电路的设计就是属于采用晶体管基极的调幅,它既能应用于小功率调幅的场合,在一些大功率调幅的场合里也有应用。

2023-06-02 11:33:43

硬件乘法器原理_硬件乘法器电路结构

硬件乘法器的实现本质是“移位相加”。对于二进制,乘数和被乘数的每一位非0即1,相当于乘数中的每一位分别和被乘数的每一个体位进行与运算,并产生其相应的乘积位。这些局部乘积左移一位与上次的和相加。即从

2021-02-18 16:34:45